(54) ЯЧЕЙКА ОДНОРОДНОЙ СТРУКТУРЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональная ячейка однородной структуры | 1989 |

|

SU1663609A1 |

| Элемент однородной структуры | 1979 |

|

SU826337A1 |

| ТРЕХКАСКАДНАЯ КОММУТАЦИОННАЯ СИСТЕМА | 2007 |

|

RU2359313C2 |

| Перестраиваемое логическое устройство | 1990 |

|

SU1815647A1 |

| Ячейка однородной вычислительной среды | 1977 |

|

SU691846A1 |

| Коммутационный элемент | 1980 |

|

SU928340A1 |

| ЯЧЕЙКА ОДНОРОДНОЙ СТРУКТУРЫ | 1993 |

|

RU2036511C1 |

| Ячейка однородной структуры | 1990 |

|

SU1778757A1 |

| А. П. Аристе, В. Д. Болотин, И. М. Браславский, Э. И. Ваус, Б. Г. Дысин, Ю. Ю. Кесс, М. Г. Кривоногое, В. Г. Куликов, И. В. Лапшин, В. И. Осетров, Г. С. Савинов, X. И. Тани, К. А. Тинн и Э. X. Тыугу | 1965 |

|

SU173040A1 |

| Ячейка однородной структуры | 1974 |

|

SU711564A1 |

Г

Изобретение относится к автомати ке и вычислительной технике и может найти применение для построения цифровых устройств на базе однородных микроэлектронных структур.

Известны ячейки однородной структуры, содержащие, блок входных логических элементов, информационные вхо ды которых соединены с информационными входами ячейки, блок настройки базисных функций, входы которого соединены с настроечными входами ячейки, блок выходных логических элементов, блок логических функций, блок арийметических функций и блок взаимопроникновения сигналов 1.

Наиболее близким техническим решением к изобретению является ячейка однородной структуры, содержащая блок входных логических элементов, информационные входы которого соединены с информационными входами ячейки, а выходы соединены с группами информационных входов блока логических функций блока арифметических функций, блока регистров, блока развязки логических функций, управляющие входы которых соединены с соответствукадими выходами блока настройки базисных функций, входы которого соединены с настроечными входами ячейки, а также блок координатной выборки, блок настройки входных логических элементов, блок совмещения автс 1атных и коммутационных функций и блок взаимопроникновения сигналов, регистр, элементы ИЛИ- ЯЕ, две группы элементов И, группу .элементов НЕ 2.

Однако известные устройства имеют

0 низкое быстродействие.

Целью изобретения является повышение быстродействия ячейки однородной структуры.

Это достигается тем, что в ячейке

5 однородной структуры, содержащей блок входных логических элементов/ информационные входы которого соединены с информационньпли входамк ячейки, выходы блока входных логических элемен0тов соединены с группами информационных входов блока логических функций, блока арифметических функций, блока регистра., блока развязки логических функций, управляющие входы которых

5 соединены с соответствующими выходами блока настройки базисных функций, входы которого соединены с настроечными входами ячейки, блок координатной выборки, выходы которого соеди0 с входами блока настройки базисных функций и через блок настройки входных логических элементов с управляющими входами блока входных логических элементов, управляющие входы блока совмещения автоматных и коммутационных функций и блока взаимопроникновения сигналов соединены с соответствующими выходами блока настройки базисных функций, выходы блока логических функций, блока арифметических функций, блока развязки логических функций, блока совмещения автоматных и коммутационных функций, блока взаимопроникновения сигналов соединены с соответствующими входами блока выходных логических элементов, входы блока настройки выходных логических элементов соединены с соответствующими входами ячейки, вход блока арифметических функций является тактирующим входом ячейки, регистр, элементы ИЛИ-НЕ, две группы элементов И, группу элементов НЕ, выхды блока входных логических элементов соединена через элементы НЕ группы с информационными входами блока совмещения автоматных и коммутационных функций и блока взаимопроникновения сигналов, выход блока логических функций соединен с входами блока раэвязки логических функций и блока совмещения автоматных и коммутационных функций, выходы блока регистров череэ регистр соединены с первыми входами элементов ИЛИ-НЕ, соответствующие выходы блока нас;,тройки базисных функций через элементы ИЛИ-НЕ соединены с первыми входами элементов И первой и второй групп, вторые входы которых соединены с соответствующими выходами блока .настройки базиснык функций выходы элементов И первой и второй групп соединены с соответствующими входами .блока выходных логических элементов, выходы которого соединены с выходами ячейки, вход регистра соединен с тактирующим входом ячейки, .

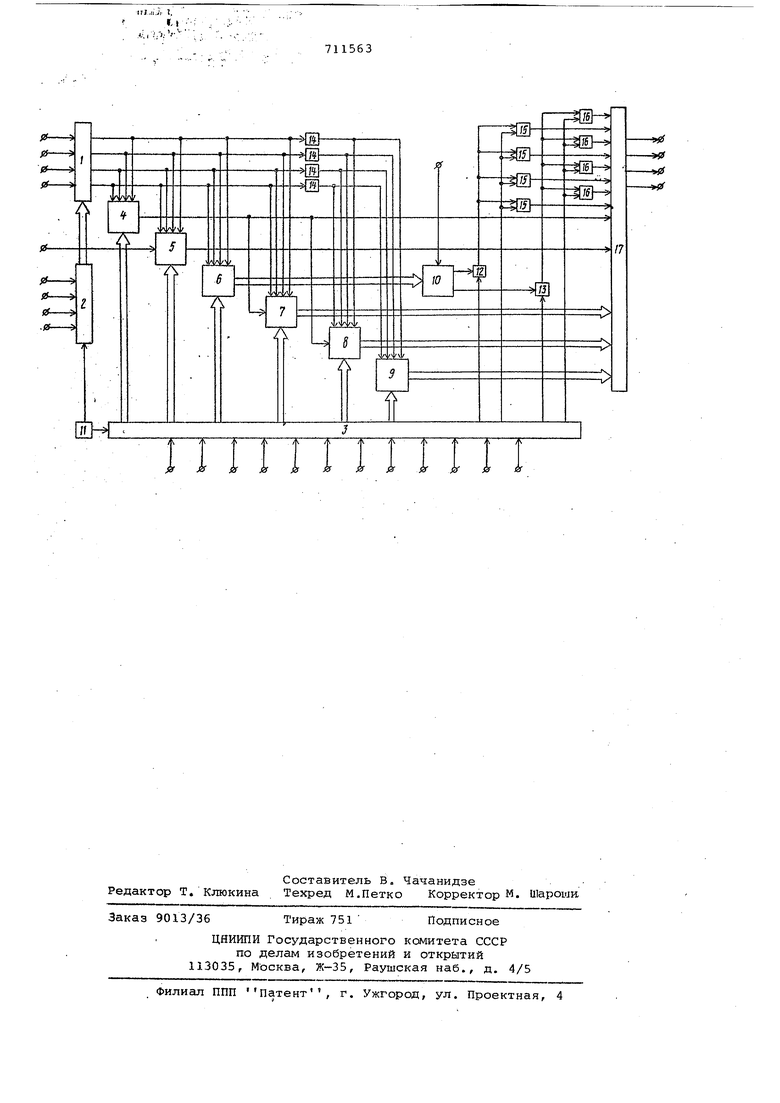

Яа чертеже представлена функциональная схема ячейки однородной струтуры.

Она; содержит блок 1 входных логических элементов,.блок 2 настройки входных логических элементов/ блок 3 настройки базисных функций, блок 4 логических функций, блок 5 арифметических функций, блок б регистров, блок 7 развязки логических функций, йлок 8 совмещения автоматных и ксвмму1 ационных функций, блок 9 взаимопроникновения сигналов, регистр 10, бло И координатной выборки, элементы ИЛИ-ЯЕ 12 и 13, элементы НЕ 14, элементы И 15 первой группы, элементы И 16 второй группы, блок 17 выходных логических элементов.

Ячейка ..однородной структуры функ. ционируетследующим образом.

На выходах блока 11 координатной выборкивырабатывается единичный логический уровень, который подключает соответствующие входы ячейки к блоку 2 настройки входных логических элементов и настроечные входы ячейки к блоку 3 настройки базисных функций. Далее осуществляется запись .:в блок 2 кода настройки блока 1 входных логических элементов, в результате чего Выбранные информационные входы соединяются со схемой яч.ейки, и запись в блок 3 кода настройки ячейки на реализацию базисных функций.

При выборе блока 4 .логических функций ячейка реа.лизует одну из перечисленных функций от одной до четырех переменных: И, И-НЕ, ИЛИ, ИЛИ-НЕ, равнозначности и неравнозначности.

При выборе блока 5 арифметических функций ячейка реализует либо последовательный полный сумматор для дюбых двух информационных входов ячейки, либо одну из перечисленных функций от одной до четырех переменных с задержкой на один такт: И, И-НЕ, .ИЛИ, ИЛИ-НЕ, равнозначности и неравнозначности. В этом случае к схеме :ячейки подключается тактирующий вход.

При реализации ячейкой четырёхразрядного сдвигового регистра используются блок 6 регистров, регистр 10, элементы ИЛИ-НЕ .12 и 13 и элементы И 15 и 16, а также тактирующий вход ячейки. Пусть ячейка реализует четырехразрядный сдвиговый.регистр с управлением. В этом случае блок 6 подключает к регистру 10 от одного до объединенных через дизъюкцию трех информационных входов ячейки, доторые могут быть выбраны произвольно и служат в качестве информационного входа четырехразрядного сдвигового регистра, и один произвольно выбранный из оставшихся информационных входов ячейки в качестве управляющего входа четырехразрядного сдв.игового регистра. При подаче единичного логического уровня на информационный вход ячейки который подключен к управляющему входу четырехразрядного сдвигового регистра, осуществляется подключение тактирующего входа ячейки к регистру 10 и начинается сдвиг информации. При подаче нулевого логического уровня на указанный информационный вход ячейки тактирующий вход ячейки отключается от регистра 10 и сдвиг информации прекращается. В этом случае информация через элементы ИЛИ-НЕ 12, элементы И 15 и блок 17 выходных логических элементов подается на соответствующие выходы ячейки. При помощи элементов И 15 осуществляется снятие информации с тех выходов ячейки, соответствующие информационные входы которых не были использованы в качестве информационных входов регистра 10. Если ячейка реализует четырехразрядный

сдвиговый регистр без управления, блок б подключает к регистру 10 от одного до объединеннЕдх через дизъюкцию четырех информационных входов ячейки, которые служат в качестве информационного входа регистра 10. В этсм случае тактирующий вход постоянно подключен к регистру 10, с которого информация снимается аналогичным образом через элемент ИЛИ-ЯЕ 13, элементы И 16 и блок 17.

При выборе блока 7 развязки логических функций ячейка реализует на двух произвольно выбранных выходах одну из перечисленных функций от одной до четырех переменных; И, И-НЕ, ИЛИ, ИЛИ-НЕ, равнозначности и неравнозначности. При этом на двух остальных выходах ячейки реализуется либо функция ИЛИ от двух переменных, либо выдача одного произвольно выбранного переменного.

При выборе блока 8.совмещения автоматных и коммутационных функций функционирует и блок 4. В этом слу,чае осуществляется подключение одног произвольно выбранного информационного входа ячейки к ее произвольно выбранному выходу. Для остальных информационных входов и выходов ячейка реализует одну из перечксленных функций от одной до трех переменных: Иу И-НЕ, ИЛИ, ИЛИ-НЕ, равнозначности и неравнозначности. При выборе блока :9 взаимопроникновения сигналов ячейка реализует полный базис коммутационных функций.

Формула изобретения Ячейка однородной структуры, с6держащая блок входных логических элементов, информационные входы которого соединены с информационными входарли ячейки, выходы блока входных логичейких элементов соединены с группами информационных входов блока логических функций, блока арифметических функций, блока регистров f блока развязки логических функций, управляющие входы которых соединены с соотВетствующими выходами блока настройки базисных функций, входы которого соединены с настроечными входами ячейки, блок координатной выборки, выходы которого соединены с входами блока настройки базисных функций и . блок настройки входных логических элементов с управляющими входами блока входных логических элементов, управляющие входы блока совмещения автоматных и коммутационных функций и блока взаимопроникновения сигналов соединены с соответствующими выходами блока настройки базисных функций, выходы блока логических функций, блока арифметических функций, блока развязки логических функций, блока совмещения автсматных и коммутационных функций, блока взаимопроникновения сигналов соединены с соответствующими входами блока выход0ных логических элементов, входы блока настройки (ВЫХОДНЫХ логических элеИентов соединены с соответствующими входами ячейки, вход блока арифметических функций является тактирующим

5 входом ячейки, регистр, элементы ИЛИ-.НЕ, две группы элементов И, группу элементов НЕ, отличающаЯс я тем, что, с целью повышения бы стродействия, выходы блока входных

0 логических элементов соединены через элементы НЕ группы с информационными входами блока совмещения автоматных и коммутационных функций и блока взаимопроникновения сигналов, выход бло5ка логических функций соединен с входами блока развязки логический функций и блока совмещения автоматных и коммутационных функций, выходы блока регистров через регистр соединены с первыми входами элементов ИЛИ-НЕ, соответствующие выходы блока настройки, базисных функций через элементы ИЛИНЕ соединены с первыми входами элементов И первой и второй групп, вторые входы которых соединены с соот5ветствующими выходами блока настройки базисных функций, выходы элементов И первой и второй групп соединены с соответствующими входами блока выходных логических элементов, выхо ды которого соединены с выходами ячейки, вход регистра соединен с тактирующим входом ячейки.

Источники информации, принятые во внимание при экспертизе

5

0 наук. М.: 1970.

5

с 24, рис. 1 (прототип).

711563

Авторы

Даты

1980-01-25—Публикация

1973-07-10—Подача