(54) ЯЧЕЙКА ОДНОРОДНОЙ СТРУКТУРЫ

входов пятого элемента И-НЕ, второй вход которого подключен к нулевому выходу четвертого триггера настройки, а выход к одному из входов шестого элемента И-НЕ, выход второго элемента И-НЕ соединен также со входами первого и второго элементов И, второй вход первого элемента И подключен к единичному выходу- первого триггера настройки, а выход - к горизонтальному информационному входу блока ускоренной коммутации, второй горизонтальный инАормадионный вход которого соединен с выходом второго элемента И, второй вход которого подключен к единичнолу выходу второго триггера настройки, первый вер.тикальный информационный вход блока ускоренной коммутации соединен с одним из входов седьмого элемента И-ЯЕ другой вход которого, подключен к нулевому выходу пятого триггера настройки, а выход соединен с одним из входов восьмого элемента И-НЕ, второй вход которого соединен с выходом ;девятого элемента И-НЕ, первый вход :которого соединен со вторым вертикальным информационным входом блока ускоренной коммутации, а второй вход- .с нулевым выходом шестого триггера настройки, третий вход восьмого элемента И-НЕ соединен с выходом десятого элемента И-НЕ, первый вход которого соединен с дополнительным информационным выходом блока выходных логических элементов, а второй вход подключен к нулевому выходу седьмого триггера настройки, выход восьмого элемента И-ЯЕ соединен с одним из входов одиннадцатого элемента И-НЕ,. второй вход которого подключен к нулевс 1у выходу восьмого триггера настройки, а Выход - ко второму входу шестого элемента И-НЕ, выход восьмого элемента И-НЕ соединен также со входами третьего и четвертого элементов И, второй вход третьего элемента И подключен к единичному выходу пятого триггера настройки, а выход - к первому вертикальному информационнстлу. входу блока ускоренной коммутации, второй вертикальный информационный вход которого соединен с выходом четвертого элемента И, второй вход которого подключен к единичному выходу шестого триггера настройки, выход шестого элемента И-НЕ соединен с дополнительным информационньйл входом блока входных логических элементов, нулевые вхццн триггеров настройки соединены с шиной сброса, а единичные входы со входами настройт и блока ускоренной кояимутации.

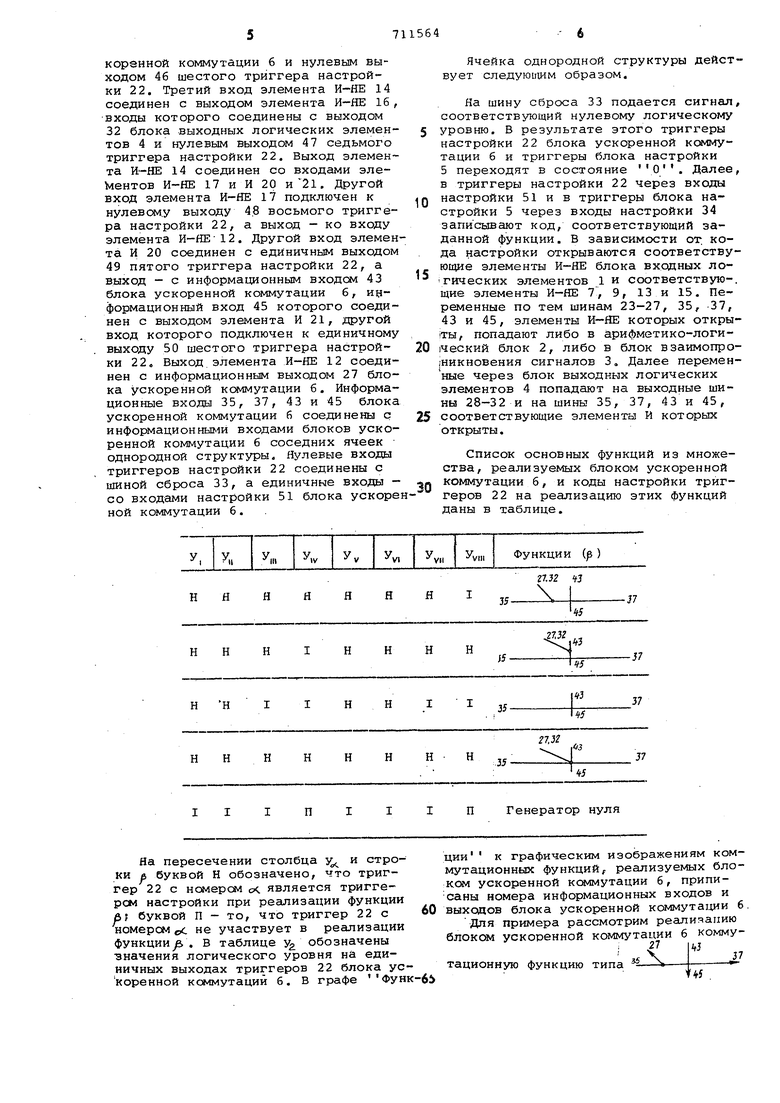

На чертеже дана функционгшьная схема ячейки однородной структуры.

Она содержит блок входных логических элеме 1тов 1; арифметико-логический блок 2; .блок взаимопроникновения

сигналов 3; блок выходных логическТП элементов 4; блок настройки 5; блок ускоренной-коммутации б, содержащий одиннадцать элементов И-НЕ 1-11f четыре элемента И 18-21 и восемь триггеров настройки 22.

Первая группа входов блока входных логических элементов 1 соединена с выходами блока настройки 5, вторая группа входов - с информационными выходами 23, 24, 25 и 26 блоков выходных логических элементов 4 соседних ячеек однородной структуры и информационным выходом 27 блока ускоренной коммутации 6, а выходы - с первой группой входоварифметико-логического блока 2 и блока взаимопроникновения сигналов 3, другая группа входов которых соединена с выходами блока настройки 5, а выходы подключены ко входам блока выходных логических элементов 4, выходы 28, 29, 30, 31 и 32 которого соединены с информационными входами блоков входных логических элементов 1 соседних ячеек однородной структуры и с информационным входом 32 блока ускоренной коммутации 6. Входы блока настройки 5 подключейы к шине сброса 33 и входам настройки 34 ячейки. Входы элемента И-НЕ 7 соединены с информационным входом 35 блока ускоренной коммутации 6 и нулевым выходом 36 первого триггера настройки 22, а выход - со входом элемента И-.НЕ 8. Второй вход элемента И-НЕ 8 соединен с выходом элемента И-НЕ 9, входы которого соединены с информационным входом 37 блока ускоренной коммутации 6 и нулевым выходом 38 второго триггера настройки 22. Третий вход элемента И-НЕ-8 соединен с выходом элемента И-НЕ 10, входы которого соединены с выходом 32 блока выходных логических элементов 4 и нулевым выходом 39 третьего триггера настройки 22. Выход элемента И-НЕ В соединен со входами элементов И-НЕ 11 и И 18 и 19. Другой вход элемента И-НЕ 11 подключен к нулевому выходу 40 четвертого триггера настройки 22, а выход - ко входу элемента И-НЕ 12. Другой вход элемента И 18 соединен с единичным выходом 41 первого триггера настройки 22, а выход - с информационным входом 33 блока ускоренной коммутации, б, информационный вход 35 которого соединен с выходом элемента И 19., другой вход которого подключен к единичному выходу 42 второго триггера настройки 22. Входы элемента И-НЕ 13 соединены с информационным входом ;43 блока ускоренной коммутации б и нулевым выходом 44 пятого триггера настройки 22, а выход - со входом элемента И-НЕ 14. Второй вход элемента И-НЕ 14 соединен с выходом эдтемента И-НЕ 15, входы которого соединены с информационным входом 45 блока ускорзиной коммутации б и нулевым выходом 46 шестого триггера настройки 22. Третий вход элемента И-НЕ 14 соединен с выходом элемента И-ЯЕ 16, входы которого соединены с выходом 32 блока выходных логических элементов 4 и нулевым выходом 47 седьмого триггера настройки 22. Выход элемента И-НЕ 14 соединен со входами элеЫентов И-НЕ 17 и И 20 и21. Другой вход элемента И-НЕ 17 подключен к нулевому выходу 4.8 восьмого триггера настройки 22, а выход - ко входу элемента И-НЕ12. Другой вход элемента И 20 соединен с единичным выходом 49 пятого триггера настройки 22, а выход - с информационным входсм 43 блока ускоренной коммутации б, информационный вход 45 которого соединен с выходом элемента И 21, другой вход которого подключен к единичному выходу 50 шестого триггера настройки 22, Выход элемента И-НЕ 12 соединен с информационным выходом 27 блока ускоренной коммутации б. Информационные входы 35, 37, 43 и 45 блока ускоренной коммутации б соединены с информационными входами блоков ускоренной коммутации б соседних ячеек однородной структуры. Нулевые входы триггеров настройки 22 соединены с шиной сброса 33, а единичные входы - со входами настройки 51 блока ускореной коммутации б.

Ячейка однородной структуры деист™ вует следуюишм образом.

На шину сброса 33 подается сигнал, соответствующий нулевому логическому уровню. В результате этого триггеры настройки 22 блока ускоренной коммутации б и триггеры блока настройки

О

5 переходят в состояние

Далее,

в триггеры настройки 22 через входы настройки 51 и в триггеры блока настройки 5 через входы настройки 34 записывают код, соответствующий заданной функции. В зависимости от; кода настройки открываются соответствующие элементы И-НЕ блока входных ло5тических элементов 1 и соответствую-, щие элементы И-НЕ Т, 9, 13 и 15. Переменные по тем шинам 23-27, 35, 37, 43 и 45, элементы И-НЕ которых откры1ТЫ, попадают либо в арифметико-логи0ческий блок 2, либо в блок взаимопро)никновения сигналов 3. Далее переменные через блок выходных логических элементов 4 попадают на выходные шины 28-32 и на шины 35, 37, 43 и 45,

5 соответствующие элементы И которых открыты.

Список основных функций из множества, реализуемых блоком ускоренной коммутации б, и коды настройки триггеров 22 на реализацию этих функций даны в таблице.

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка однородной структуры | 1974 |

|

SU711565A1 |

| Устройство для сопряжения однородной вычислительной системы | 1980 |

|

SU951287A2 |

| Устройство для сопряжения нескольких ЦВМ | 1982 |

|

SU1067493A1 |

| Устройство для обмена данными в вычислительной системе | 1984 |

|

SU1251090A1 |

| Устройство для контроля каналов ввода-вывода | 1980 |

|

SU935964A1 |

| Ячейка однородной структуры | 1989 |

|

SU1674104A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1989 |

|

SU1658163A1 |

| Программируемый коммутатор | 1982 |

|

SU1075410A1 |

| Устройство для цифровой записи-воспроизведения речевой информации | 1987 |

|

SU1490691A1 |

| Устройство для преобразования двоично- дЕСяТичНыХ чиСЕл B дВОичНыЕ | 1979 |

|

SU809152A1 |

llinilin Генератор нуля На пересечении столбца у и строки буквой Н обозначено, что триггер 22 с нсмером сх является триггером настройки при реализации функции и; буквой П - то, что триггер 22 с номером оС не участвует в реализации функции, В таблице у обозначены значения логического уровня на единичных выходах триггеров 22 блока ускоренной коммутаций б. В графе Функ ции к графическим изображениям коммутационных функций, реализуемых блоксхл ускоренной коммутации б, приписаны номера информационных входов и выходов блока ускоренной коммутации 6, Для примера рассмотрим реализацию блоксам ускоренной коммутации б комму Ч 57 тационную функцию типа

этсяи случае в триггерах 22 блока скоренной коммутации 6 записывают код у, y,v Уу о и У|, У|„ уГУуг, Ууш . 1. в результате этого элементы И-НЕ 9 и 10 закрыты, и пееменные от информационного входа 35 через открытые элементы Й-НЕ 7, 8 и 19 попадают на информационный вход 37, который превращается в информаионный выход. Эти же переменные через открытые элементы И-ЯЕ 11 и 12 ,. попадают на информационный выход 27, так как элемент И-НЕ 17 закрыт. Закрыты также элеме.нты И-ЯЕ 15 и 16. В езультате этого переменные от инфорационного входа 43 через открытые элементы И-ЯЕ 13, 14 и 21 попадают а информационный вход 45, который превращается в информационный,выход. Аналогично реализуются блоком ускоренной коммутации б и другие функции, данные в таблице.

Изобретение позволяет увеличить быстродействие ячейки однородной структуры в два раза.

Формула изобретения

Ячейка однородной структуры, содержащая блок входных логических элементов, первая группа входов которого соединена с выходами блока настройки, вторая группа входов с информационными входами ячейки, а выходы - с первой группой входов арифметико-логического блока и блока взаимопроникновения сигналов, другая группа входов которых соединена с выходами блока настройки, а выходы - с входами блока выходных логических элементов, выходы которого соединены с информационными выходами ячейки, входы блока настройки соединены с шинной сброса и входами настройки ячейки, блок ускоренной коммутации на элементах И и И-НЕ и на триг герах настройки, отличающаяся тем, что, с целью повышения быстродействия, первый горизонтальный информационный вход блока ускоренной кс 1мутации соединен с одним из входов первого элемента И-ЯЕ, другой вход которого подключен к нулевому выходу первого триггера настройки, а выход соединен с одним из входов второго элемента И-ЯЕ, второй вход которого соединен с выходом третьего элемента И-ЯЕ, первый вход которого соединен со вторым горизонтальным инфсзрйационным входом блока ускоренной коммутации, а второй вход - с нулевым выходов второго триггера настройки, третий вход второго элемента И-ЯЕ соединен с выходом четвертого элемента И-ЯЕ, первый вход которого соединен с дополнительным информационным выходом блока выходных логических элементов, а второй вход подключен к нулевому выходу третьего триггера настройки, выход второго элемента И-НЕ соединен с одним из входов пятого элемента И-ЯЕ, второй вход которого подключен к нулевому выходу четвертого триггера настройки, а выход - к одному из входов -шестого элемента И-НЕ, выход второго элемента И-НЕ соединен также со входами первого и второго элементов И,второй вход первого элемента И подключен к

единичнсму выходу первого триггера настройки, а выход - к первому горизонтальному информационному входу блока ускоренной коммутации, второй горизонтальный информационный вход которого соединен с выходом второго

S элемента И, второй вход которого

подключен к единичному выходу второго триггера настройки, первый вертикальный информационный вход блока ускоренной коммутации соединен с од0 ним из входов седьмого элемента И-ЯЕ, другой вход которого подключен к нулевому выходу пятого триггера настройки, а выход соединен с одним из входов восьмого элемента И-НЕ, вто5 рой вход которого соединен с выходом девятого элемента И-НЕ, первый вход которого соединен со. вторым вертикальным информационным входом блока ускоренной коммутации, а второй вход - с

п нулевым выходом шестого триггера .настройки, третий вход восьмого элемента И-ЯЕ соединен с выходом десятого элемента И-ЯЕ, первый вход которого соединен с дополнительным информационным выходом блока выходных погических элементов а второй вход подключен к нулевому выходу седьмого триггера настройки, выход восьмого элемента И-НЕ соединен с одним из - входов одиннадцатого элемента И-НЕ,

0 второй вход которого подключен к нулевоиу выходу восьмого триггера настройки, а выход - ко второму входу шестого элемента И-ЯЕ, выход восьмого элемента И-ЯЕ соединен также со

5 входами третьего и .четвертого элементов И, второй вход третьего элемента И подключен к единичному выходу пятого триггера настройки, а выход - к первому вертикальному инфор0 мационному входу блока ускоренной коммутации, второй вертикальный информационный вход которого соединен с выходом четвертого элемента И, второй вход которого подключен к единичее нему ВЫХОДУ шестого триггера настройки, выход шестого элемента И-ЙЕ соединен с дополнительным информационным входом блока входных логических элементов, нулевые входытриггеров настройки соединены с шиной сброса, а единичные входы - со входами настройки блока ускоренной коммутации.

Источники информации, принятые во внимание при экспертизе

микроэлектронных схемах. - Вопросм кибернетики.Однородные микроэлектронные структуры.М.,Советское радио.1973.

ройств и методы организации вычислительных процессов на однородных структурах, АВТ, вып. 3, Рига, Зинатне, 1972, с. 24, рис. 1. ттт

Авторы

Даты

1980-01-25—Публикация

1974-06-28—Подача