(54) СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Анализатор функций распределения экстремумов | 1977 |

|

SU746545A1 |

| Статистический анализатор | 1979 |

|

SU842833A1 |

| Статистический анализатор | 1976 |

|

SU643891A1 |

| Статистический анализатор | 1974 |

|

SU506869A1 |

| Статистический анализатор | 1979 |

|

SU832559A1 |

| Статистический анализатор | 1979 |

|

SU875388A1 |

| Устройство для анализа экстремумов случайного процесса | 1981 |

|

SU962977A1 |

| Анализатор функций распределения экстремумов | 1982 |

|

SU1091176A1 |

| Устройство для определения функции распределения размахов | 1976 |

|

SU622092A1 |

| Статистический анализатор | 1979 |

|

SU860081A1 |

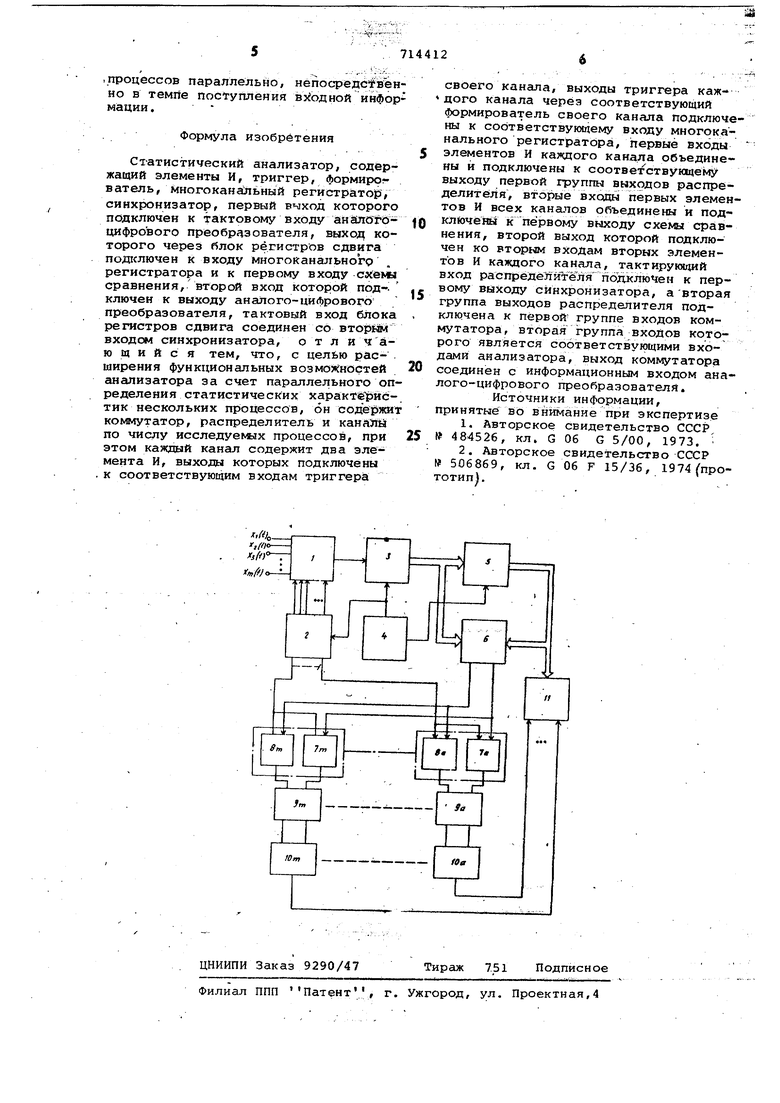

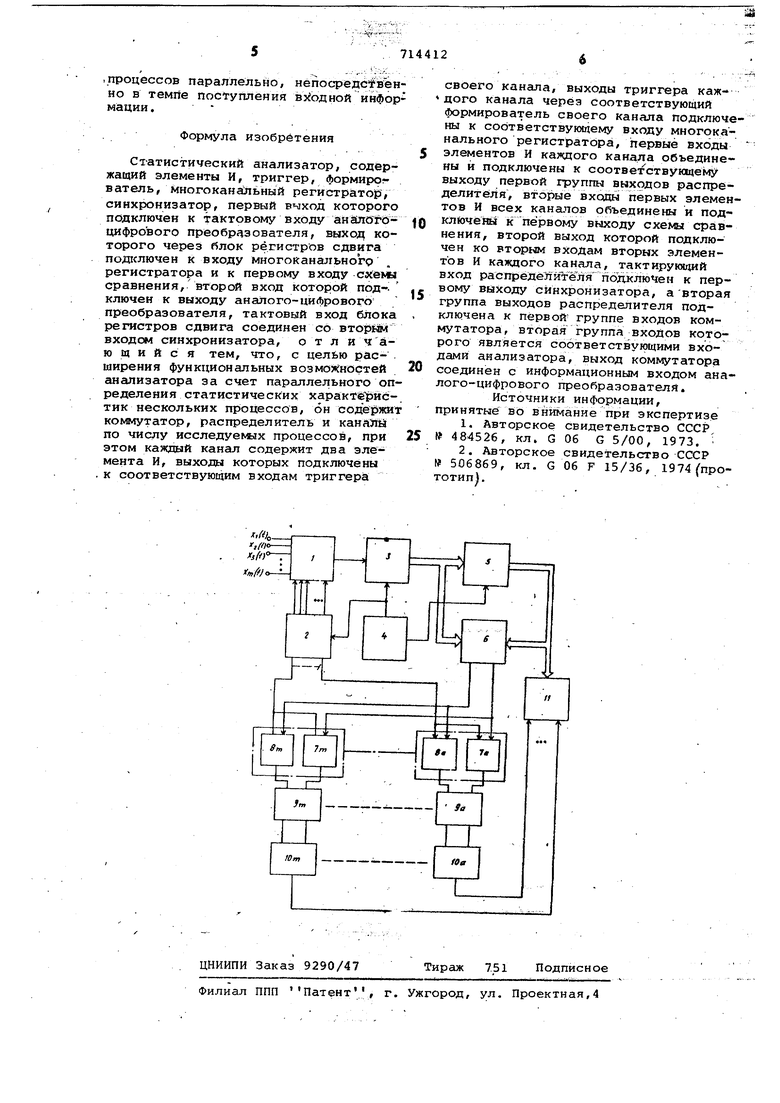

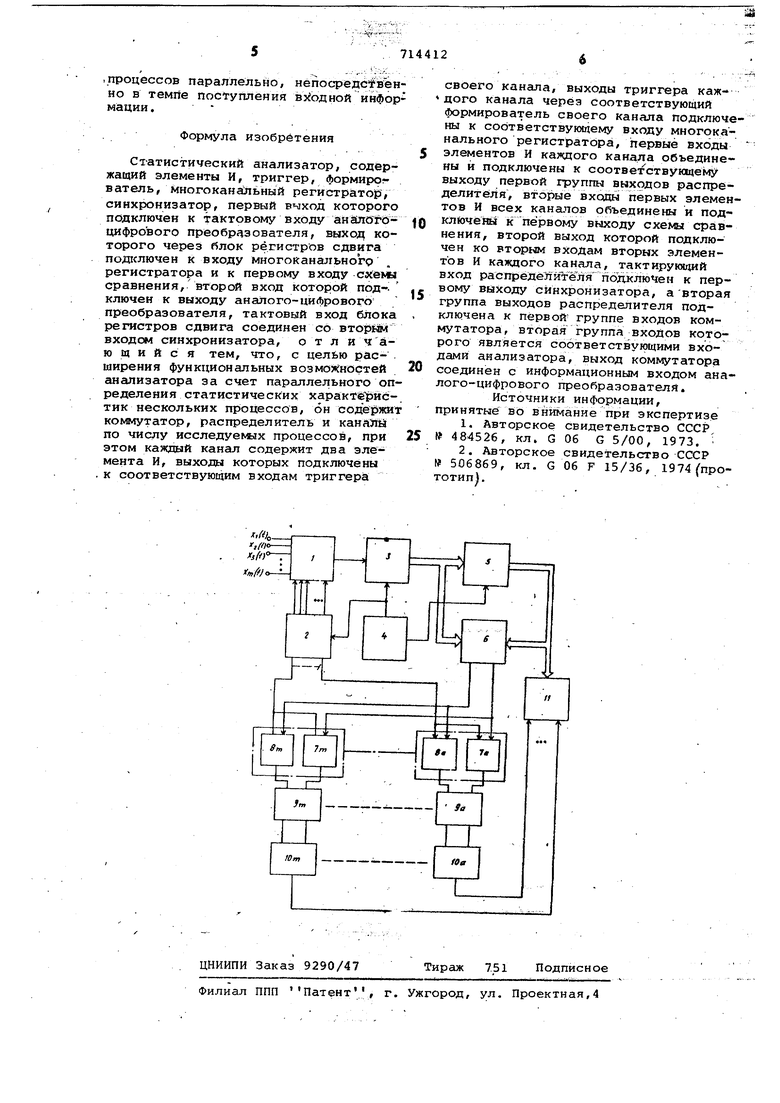

Изобретение относится к устройст.вам статистического анализа и может быть использовано для определения ве роятностных характеристик экстремумо при комплексном испытании новой техники, в частности, при исследовании распределения нагрузки в различных узлах машин и механизмов, в системе информационно-измерительных комплексов, автоконтроля, вычислительной техники. Известно устройство статистическо го анализа, содержащее аналого-цифро вой преобразователь, блок выделения экстремумов, запоминающий регистр, дифференцирующий бло.Кг триггер, элемент И, деишфратор, многоканальный регистратор 1, - -Наиболее близким техническим реше нием к предложенному является статис с кий анализатор 2, содержащий аналого-цифровой преобразователь, промежуточный регистр памяти, схему сравнения кодов для сравнения значений соседних выборок, триггер, му сортировки, регистр. Недостатком названных устройств является их ограниченные, функциональ ные возможности, а именно: невозможность определения параллельно ста истических характеристик нескольких процессов. Целью изобретения является расширение функциональных возможностей анализатора за сче параллельного определения статистических характеристик нескольких процессов. Эта цель достигается тем, что в статистический анализатор, содержавши элемент И, триггер, формирователь, многоканальный регистратор, синхронизатор, первый выход которого подключен к тактовому входу аналого-цифрового преобразователя, выход которого через блок регистров сдвига подключен к входу многоканального регистратора и к первому входк схемы сравнения, второй вход которой подключен к выходу аналого-цифрового преобразователя, тактовый вход блока регистров сдвига соединен с вторым входом синхронизатора, введены коммутатор, распределитель и каналы по числу исследуемых процессов, при этим йаЖдаЙ канал содержит два элемента И, выходы которых подключены к соотйетствующим входам триггера своего канала, выходы триггера калдаого канала через coot- ветствуюпдий формирователь своего подключены к соответствующе лу i nf tfWiOfOKaHanbH выё входы элементов И каждо.гр; канаиа объединены.и подключены к сботвётст в1,йщему вых6ду первой группы ёыШдав асЛредёлйтёля, вторые входы первых элёмёнтЪв и всех каналов объединены и подключены к первому выходу схемы сравнения, второй выход которой под 1 ЯЙчен с торый входам втбрых элементов И каждого канала, тактирующий вход раепре елйтёля подключён 1с первому выходу синхронизатора, а вторая группа выходов распределителя подклю чена к первой группе входов коммутаTppai, вторая группа входов которого являетря соответствующими входами анализатора, выход коммутатора соединен с информационним :ходом аналогоцифрового преобразователя. Структурная схема анализатора при ведена на чертеже. Устройство содержит коммутатор 1, распределитель 2, аналого-цифровой преобразователь 3, синхронизатор 4, блок 5 регистров сдвига (оперативной памяти), схему б сравнения (кодов), . элементы 7д,. . .7tn/ SQ, .. . , т эиг геры 90 ,... 9,, формирователи Юд ,, . . lOf, многоканальный регистратор 11. : Выход коммутатора 1 соединен со вхЪдом аналого-цифрового преобразователя (АЦП) 3, кодовые выходы которого присоединены к блоку 5 регистров сдв га и к одному из входов схемы сравнения кодов 6. Выход блока 5 подключен ко,входу многоканального регистратора 11,и ко второму входу схемы б сра нения Кодов. Выход синхронизатора 4 соединен с тактовым входом блока 5, другой выход синхронизат.ора подклю.чен ;к тактовом вход АЦП и распреде лителя 2, одни выходы которого прусо ёдйнены ко входам управления коммутатора Г дау йё выходы соёдинёпы с од ними из входов Объединенных попарно элементов 7 и 8 И, а. другие входы элементов 7 и 8 И прйсдедЙнёШ к соответствующим выходам схемы сравнени кодов. Выходы пар элементов 7 и 8 И соединены с установочными входами триггеров 9, выходы которых через формирователи 10 подключены к управляющим вхбдам, многоканальнбгб рёгйстратора 11.. Работа анализатбр а ОсувдествЛя ётся следующим образом. Набор исследуемых реализаций Х (t) , ),.. . V. (t)7T Xf,t) поступает через коммутатор 1 в очередности, задаваемой распределителем 2, на аналого-цифровой прёобразователь 3, где преобразуется в параллельный код. Частота задается синхронизатором 4 в сб твёТст вии с частотными характеристиками йНШ ЯуеЖ1Г сиТЪЖ6в ГТсроме joг сйнхрониз&тор осуществляет тактирование распределителя в моменты вмборки, а также запись и сдвиг слов в блок 5. Прйнцип выделения моментов появленияи Измерения значений экстремумов, в статист ическом анализаторе заключается в следующем. После каждого преобразования значения кодов с АЦП 3 записываются в Йлок регйстр6в сдвига 5 оперативной памяти. Число .ячеек Памяти т оответствует числу исследуемых процессов. Сле/1рвательно, на выходах АЦП 3 и блока 5 будут выдаваться коды соседних выборок одного и того же процесса, т. е. .j- (t) и X.-.j-. (t) , где i, j- соответствующие номера процесса и выборки. Значения кодов (t) и (t) одновременно подаются на схему сравнения (СС) б. Если (t) XY,J-. (t) (значения последующих выборок процесса превьтгайт значения предыдущих), т. е. значение реализации возрастает, то схема 6 по шине -видает сигналы логической единицы, а по шине - логического йуля. Если .j (t) (t), т. е. когда значение исследуемой реализаций уменьшается, по и1ине схема б сравнения выдает сигналы логической единицы, а по шине логического нуля. По шине сигналы схемы 6 сравнения поступают на элементы 7а/ ... по шине - на 8д,...8. Элементы И объединены попарно по числу процессов. Опрос пар элементов И производится импульсами распределителя в моменты времени, определяемые синхронизатором для каждого процесса но сдвинутым относительнр начала выборки на время, необходимое для окон.чания работы АЦП, В Зависимости от состояния элементов 7 и 8 И меняется и состояние триггера , установочные входы которого соёдинены с выходами элементов Я. При монотонном изменении сигнала схема б выдает управляющий потенциал по одной из шин, пропуская через соответствующий элемент И последовательность импульсов опроса, первым из которых осуществляется смена состояния триггера, причем моменты смены состояний соответствуют ilaкcимyмy или минимуму подключенного процесса. В эти моменты форг ирователи iO вырабатывают сигналы записи значения экстремума максимума или минимума соответстзвующего процесса в регистратор 11. Анализ заканчиваетсй после того, как синхронизатор выраеоатывает необходимое число интервалов, в результате в многоканальном регистраторе накапливается информация о плотности распределения ФIнимaльньlx (максимальных) значений всех исследуемых процессов. Таким образом, предложенный ана. лидатор позволяет определять ст ункции аспределения экстремумов нескольких

Авторы

Даты

1980-02-05—Публикация

1977-10-12—Подача