(54) СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ТЕКУЩЕГО КОНТРОЛЯ И СТАТИСТИЧЕСКОГО АНАЛИЗА РАЗМАХОВ КОЛЕБАНИЙ НАПРЯЖЕНИЯ | 1993 |

|

RU2075752C1 |

| Анализатор функций распределения экстремумов | 1982 |

|

SU1091176A1 |

| Система для передачи телеизмерительной информации | 1981 |

|

SU1037313A1 |

| Статистический анализатор условной функции распределения размахов колебаний напряжения | 1986 |

|

SU1365096A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ИНФОРМАЦИИ В АДАПТИВНЫХ ТЕЛЕМЕТРИЧЕСКИХ СИСТЕМАХ | 1995 |

|

RU2103745C1 |

| Статистический анализатор | 1979 |

|

SU832559A1 |

| Швоуловитель | 1982 |

|

SU1060725A1 |

| Устройство для селекции изображений | 1991 |

|

SU1837335A1 |

| Автоматизированная система тестового контроля | 1985 |

|

SU1278857A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ ТОЧНОГО ВРЕМЕНИ | 1990 |

|

RU2033640C1 |

1

Изобретение относится к измерению вероят ностных характеристик случайных процессов и может быть использовано при усталостнопрочностных испытаниях транспортных средств, судов, летательных аппаратов, буровых установок и других механических устройств, а также в ряде областей информационно-измерительной техники, в автоматизированных системах управления и контроля.

Известны методы проведения испытаний механических объектов на прочность и долговечность, одним из которых является метод полных циклов (парных размахов), заключающийся в подсчитывании последовательных изменений нагрузки, превосходящих по размерам заданные значения. Размахи подсчитываются пол

парно: в положительном и отрицательном направлениях. Каждая пара размахов образует полный цикл. На кривой процесса x(t) выделяются ближайшие друг к другу изменениянагрузки с амплитудой не менее заданного значения размаха (например, не менее четырех разрядов). Размахи, соответствующие установленному уровню хо, составляют полный цикл

(.RI j-R34 Xo). Значения промежуточных колебаний отбрасываются, если ощ меньше заданного уровня. Аналогичный подсчет выполняется для всех значений размахов Rg 1,2, ..., К-1} , где К - число дифференциальных коридоров (разрядов), на которые разбит диапазон процесса. Смысл этого метода заключается в том, что нерегулярный процесс изменения нагрузки рассматривается как состоящий из основных и промежуточных циклов, нало10женных на основные и имеющих амплитуду, меньшую, чем основные. Преимущества метода заключаются в том, что при систематизации нагрузок по полным циклам сохраняется определенная информация о последовательности на15гружения, результаты обработкн в малой степе ни зависят от принятого значения неучитьгеаемых циклов 1 и 2.

Известно устройство для анализа размаХов,

20 содержащее амшштудно-в ременный модулятор, вычитающее устройство, схему задержки, накопитель, амплитудно-временной преобразователь, усилитель-ограничитель, временной анализатор.

триггер, генератор тактовых, импульсов, схему антисовпадений 3.

Наиболее близfcим по технической сущности к предлагаемому является статистический анализатор для определения функций распределения размахов, содержащий преобразователь аналог-код, ключи записи максимумов, регистр максимумов, блок вычитания, блок задержки, регистр минимумов, ключи записи минимумов, блок выделения экстремумов, ждущий мультивибратор, злемент задержки, дешифратор, блок схем И, регистратор 4.

Общими недостатками указанных устройств являются ограниченные функциональные возможности, не позволяющие проводить анализ по методу полных циклов.

Цель изобретения - расширение функциональных возможностей устройства за счет систематизации нагрузок по методу полных циклов.

Поставленная цель достигается тем, что в статистический анализатор, содержащий блок задания опорных уровней, блок отображения, счетчик, схему сравнения, элемент И, аналогоплфровой преобразователь, информационный вход которого является входом анализатора, синхронизирующий вход соединен с первым вы ходом синхронизатора, а выход аналого-цифрового преобразователя соединен с входом блока выделе1шя экстремума, введены блок памяти, блок управления, триггер управления счетом, выход которого подключен к информационному входу элемента И, управляющий вход которого соединен с первым выходом синхронизатора, а выход элемента И подключен к первому входу счетчика, выход которого соединен с первым информационным входом схемы сравнения, синхронизирующий вход которой соеданен с вторым выходом синхронизатора, второй информационный вход схемы сравнения подключен к выходу блока задания опорных уровней и информационному входу блока памяти, выхо которого соеданен с входом блока отображения, а управляющий вход подключен к первому выходу блока управления, второй и третий входы которого подключены соответственно к управл5 ющему входу счетчика и первому входу триггера управления счетом, второй вход которого подключен к управляющему входу счетчика, а входы блока управления с первого по третий соединены соответственно с выходами блока выделения экстремума и выходом схемы сравнения.

Кроме того, блок управления состоит из элементов И, ИЛИ, триггера запрета, формирователей импульсов и триггера переключения, выходы которого через соответствующие формирователи импульсов подключены к входам триггера запрета, а ЕЛОД триггера переключения является первым выходом и третьим входом

блока и подключен к первому входу первого элемента ИЛИ, выход которого, а также выход второго элемента ИЛИ являются соответственно третьим и вторым выходами блока, при этом первый и второй входы первого элемента И и второй и третий входы второго элемента И соединены соответственно с выходами первого и второго, третьего и четвертого элементов И, первые входы первого и третьего, второго и четвертого элементов И попарно объединены и являются соответственно вторым и первым входами блока, вторые входы первого и четвертого, второго и третьего элементов И попарно объединены и подключены соответственно к первому и второму выходам триггера запрет та.

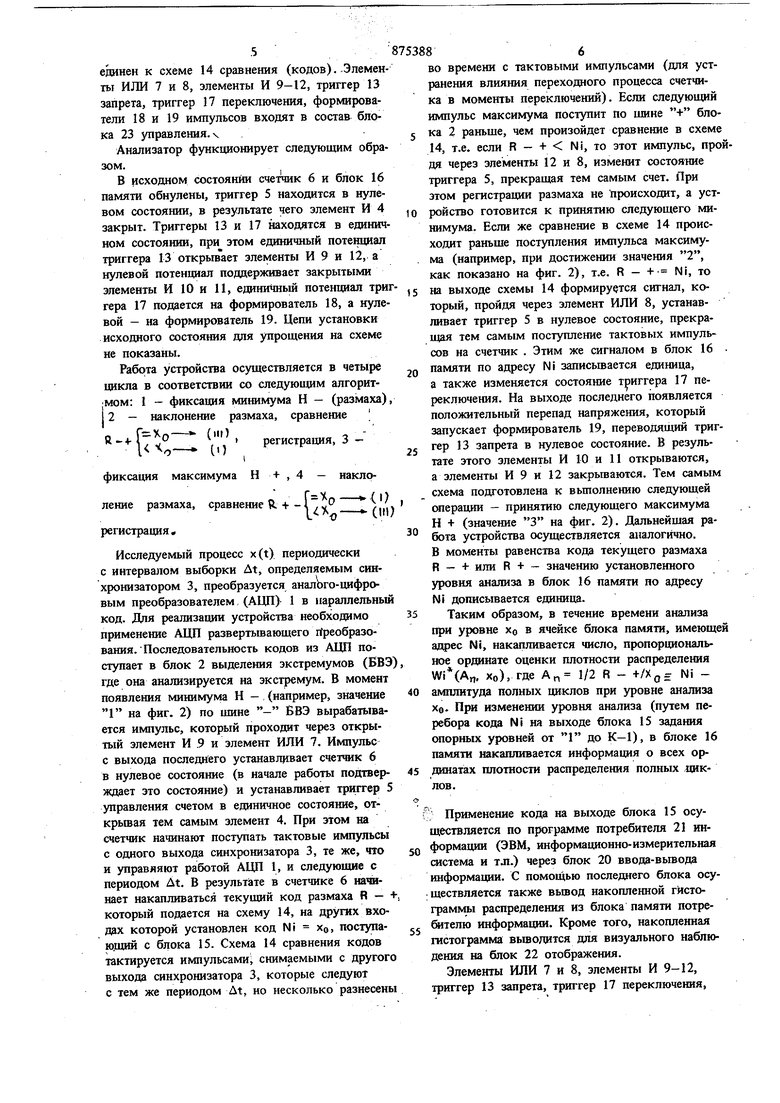

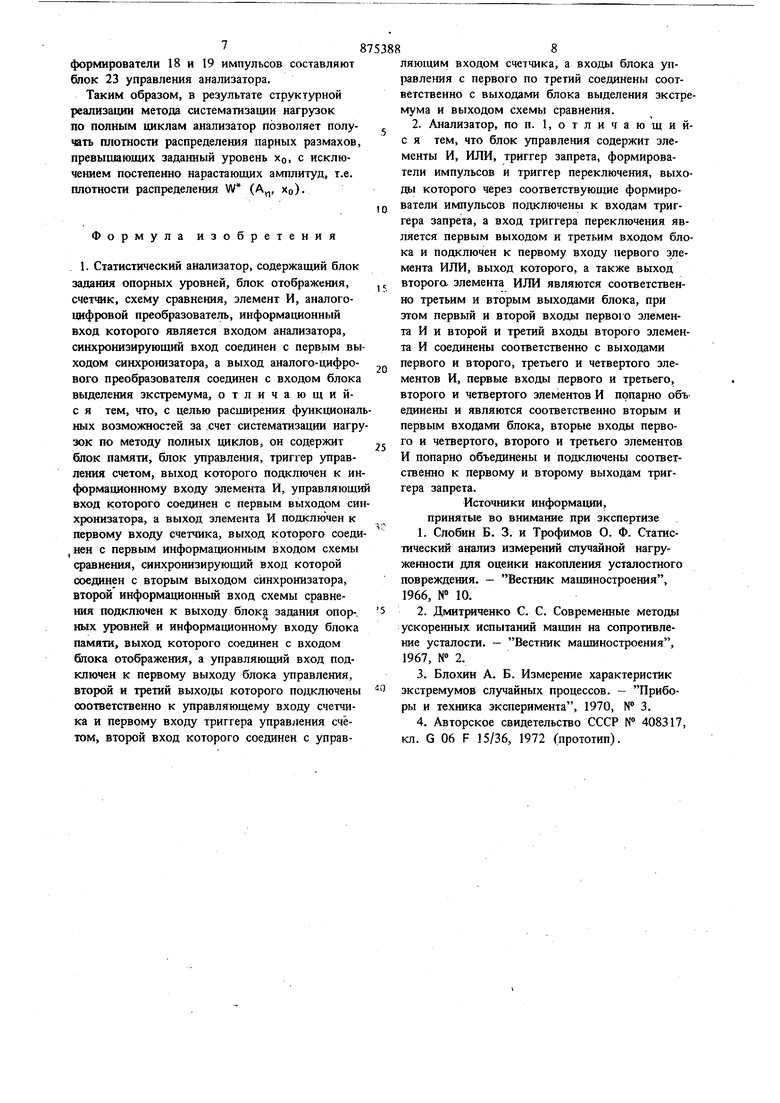

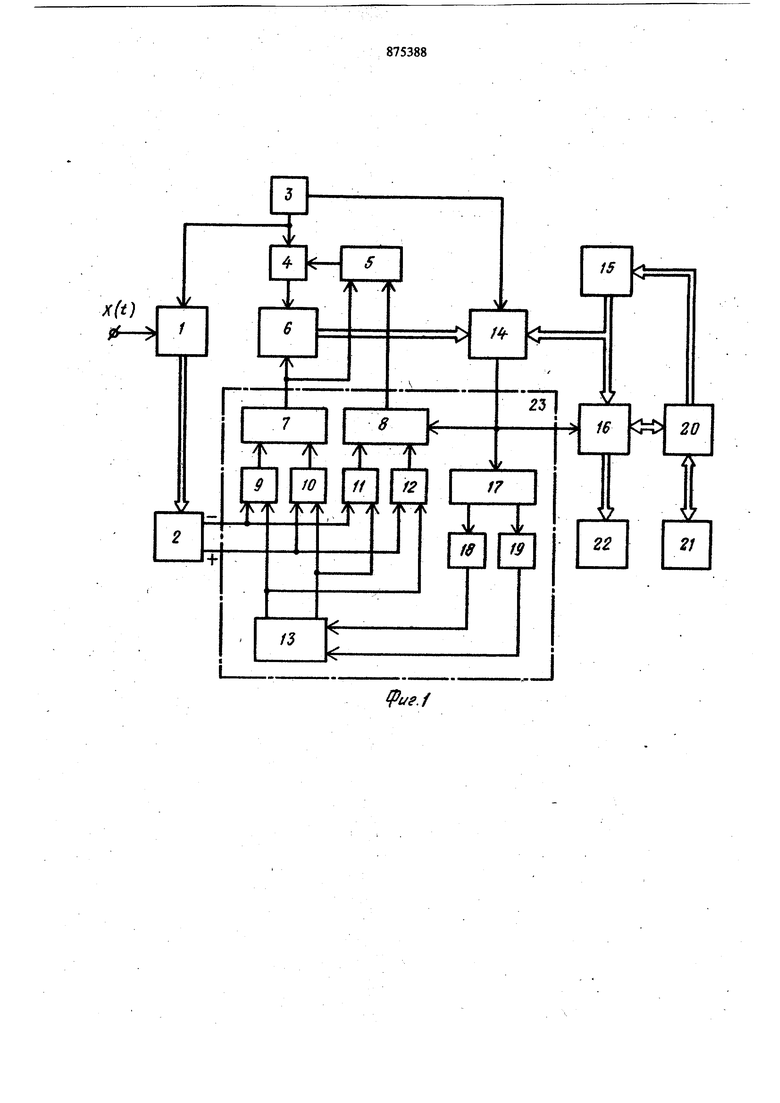

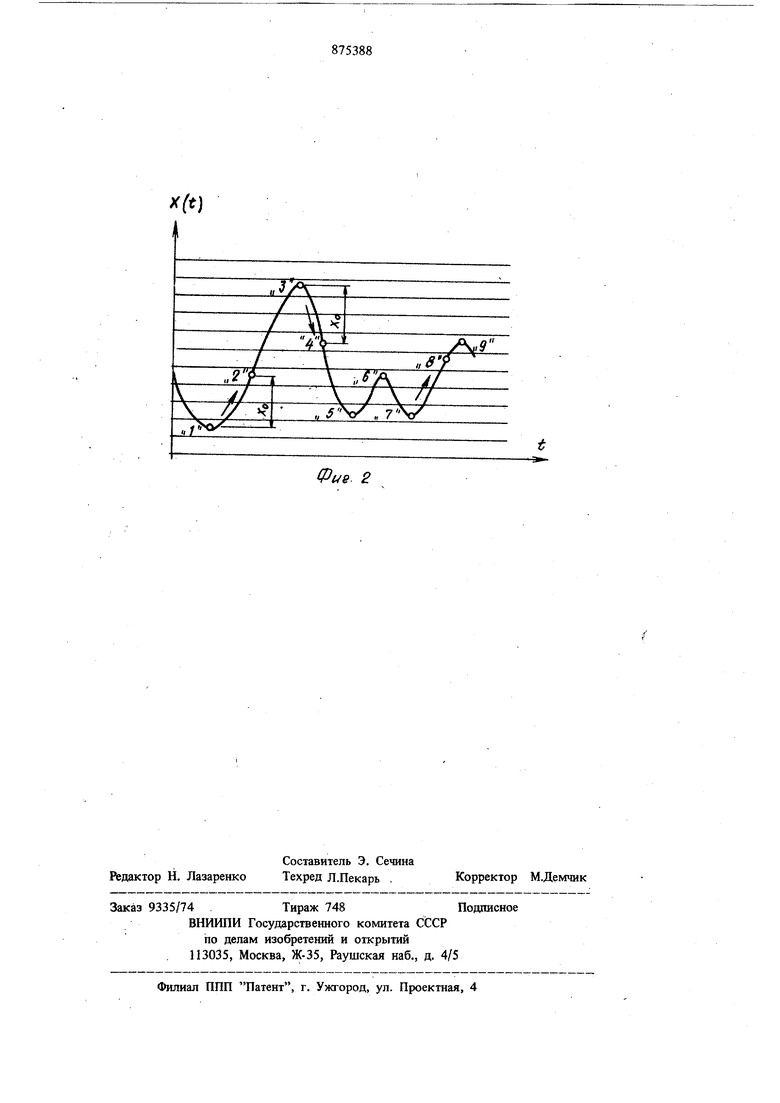

На фиг. 1 представлена схема статистического анализатора; на фиг. 2 - график размахов случайной величины.

В состав анализатора входят аналого-цифровой преобразователь . 1, блок 2 выделения экстремумов, синхронизатор 3, элемент И 4, триггер 5 зшравления счетом, счетчик 6, элементы 1Л1Ш 7 и 8, элементы И 9-12, триггер 13

запрета, схема 14 сравнения кодов, блок 15 задания опорных уровней, блок 16 памяти, триггер 17 переключения, формирователи 18 и. 19 импульсов, блок 20 ввода-вывода информации, потребитель 21 информации, блок 22 отображения, блок 23 управления.

Источник исследуемого сигнала подключен к входу аналого-цифрового преобразователя 1, . выходами подсоединенного к блоку 2 выделения экстремума, а другим входом - к синхронизатору 3 и элементу И 4. Другой вход последнего соединен с выходом триггера 5 управления счетом, а выход подключен к счетчику 6, другой вход которого подсоединен к элементу ИЛИ 7 ц одному входу триггера 5 управления счетом, причем его другой вход подключен к элементу ИЛИ 8. Выходы блока 2 выделения экстремумов соединены с первыми входами элементов И 9-12, другие входы которых подключены к выходам триггера 13 запрета. Выходы элементов 9 и 10 подсоединены к элементу ИЛИ 7, а выходы элементов И 11 и 12 - v к элементу ИЛИ 8. Выходы счетчика 6 соединены с одними входами схемы 14 сравнения, другие входы которой подключены к блоку 15 задания опорных уровней и блоку 16 памяти, а выход подсоединен к элементу ИЛИ 8, блоку 16 памяти и триггеру 17 пepekлючeIдая причем выходы последнего через формирователи 18 и 19 импульсов подключены к триггеру 13 запрета. Выходы блока 20 ввода-вывода инфор5 мации соединены с блоком 15, потребителем 21 информации и с блоком 16 памяти, выходы которого подключены к блоку 22 отображения. Второй выход синхронизатора 3 подсоединен к схеме 14 сравнения (кодов).-Элемен ты ИЛИ 7 и 8, элементы И 9-12, триггер 13 запрета, триггер 17 переключения, формирователи 18 и 19 импульсов входят в состав блока 23 управления.V Анализатор функционирует следующим образом. В исходном состоянии счетчик 6 и блок 16 памяти обнулены, триггер 5 находится в нулевом состоянии, в результате чего элемент И 4 закрыт. Триггеры 13 и 17 находятся в единичном состоянии, при этом единичный потенциал триггера 13 открывает элементы И 9 и 12, а нулевой потенциал поддерживает закрытыми элементы И 10 и 11, единичный потенциал три гера 17 подается на формирователь 18, а нулевой - на формирователь 19. Цепи установки исходного состояния для з/ттрощения на схеме не показаны. Работа устройства осуществляется в четыре цикла в соответствии со следующим алгорит;мом: I - фиксация минимума Н - (размаха) 2 - наклонение размаха, сравнение -ЧП л -:-о- ( регистрация, 3 - о- 10 фиксация максимума Н + , ление размаха, сравнение R + регистрация. Исследуемый процесс x(t) периодически с интервалом выборки At, определяемым синхронизатором 3, преобразуется аналого-цифровым преобразователем, (АЦП)- 1 в параллельный код. Для реализации устройства необходамо применение АЦП развертывающего йреобразования.Последовательность кодов из АЩ1 поступает в блок 2 выделения экстремумов (БВЭ) где она анализируется на экстремум. В момент появления минимума Н - , (например, значение 1 на фиг. 2) по щине - БВЭ вырабатывается импульс, который проходит через открытый элемент И .9 и элемент ИЛИ 7. Импульс с выхода последнего устанавл 1вает счетшк 6 в нулевое состояние (в начале работы подтверждает это состояние) и устанавливает триггер 5 управления счетом в единичное состояние, открывая тем самым элемент 4. При этом на счетчик начинают поступать тактовые импульсы с одного выхода синхронизатора 3, те же, что и управляют работой АЦП 1, и следующие с периодом At. В результате в счетчике 6 на нает накапливаться текущий код размаха R - + который подается на схему 14, на других входах которой установлен код Ni XQ, поступающий с блока 15. Схема 14 сравнения кодов тактируется импульсами снимаемыми с другого выхода синхронизатора 3, которые следуют с тем же периодом At, но несколько разнесены / I л . во времени с тактовыми импульсами (для устранения влияния переходного процесса счетчика в моменты переключений). Если следующий импульс максимума поступит по шине + блока 2 раньше, чем произойдет сравнение в схеме 14, т.е. если R - + Ni, то этот импульс, пройдя через элементы 12 и 8, изменит состояние триггера 5, прекращая тем самым счет. При этом регистрации размаха не происходит, а устройство готовится к принятию следующего минимума. Если же сравнение в схеме 14 происходит раньще поступления импульса максимума (например, при достижении значения 2, как показано на фиг. 2), т.е. R - + Ni, то на выходе схемы 14 формируется сигнал, который, пройдя через элемент ИЛИ 8, устанавливает триггер 5 в нулевое состояние, прекращая тем самым поступление тактовых импульсов на счетчик . Этим же сигналом в блок 16 . памяти по адресу Ni записьшается единица, а также изменяется состояние триггера 17 переключения. На выходе последнего появляется положительный перепад напряжения, который запускает формирователь 19, переводящий триггер 13 запрета в нулевое состояние. В результате этого элементы И 10 и 11 открываются, а элементы И 9 и 12 закрываются. Тем самым схема подготовлена к вьшолнению следующей операции - принятию следующего максимума Н + (значение 3 на фиг. 2). Дальнейщая работа устройства осуществляется аналогично. В моменты равенства кода текущего размаха R - + или R + - значению установленного уровня анализа в блок 16 памяти по адресу Ni дописывается единица. Таким образом, в течение времени анализа при уровне хо в ячейке блока памяти, имеющей адрес Ni, накапливается число, пропорциональное ординате оценки плотности распределения Wi(Ar,, Хо), где А 1/2 R - t/Xg N1 амплитуда полных циклов при уровне анализа XQ. При изменении уровня анализа (путем перебора кода Ni на выходе блока 15 задания опорных уровней от 1 до К-1), в блоке 16 памяти накапливается информация о всех ординатах плотности распределения полных дщклов. Применение кода на выходе блока 15 осуествляется по программе потребителя 21 инормации (ЭВМ, информационно-измерительная истема и тл.) через блок 20 ввода-вывода нформации. С помощью последнего блока осуествляется также вьтод накопленной гистораммы распределения из блока памяти потре1телю информации. Кроме того, накопленная истограмма вьшодится для визуального наблюения на блок 22 отображения. Элементы ИЛИ 7 и 8, элементы И 9-12, риггер 13 запрета, триггер 17 переключения. формирователи 18 и 19 импульсов составляют блок 23 управления анализатора. Таким образом, в результате структурной реализации метода систематизации нагрузок по полным циклам анализатор пЬзво яет получать плотности распределения парных размахов, превышающих зада1шый уровень XQ, с исключением постепенно нарастающих амплитуд, т.е. плотности распределения W (А,, XQ). Формула изобретения 1. Статистический анализатор, содержащий блок задания опорных уровней, блок отображения, счетчик, схему сравнения, элемент И, аналогоцкфровой преобразователь, информационный вход которого является входом анализатора, синхронизирующий вход соединен с первым вы ходом синхронизатора, а выход аналого-цифрового преобразователя соединен с входом блока выделения экстремума, отличающийс я тем, что, с целью расщирения функционал ных возможностей за ,счет систематизации нагр зок по методу полных циклов, он содержит блок памяти, блок управления, триггер управления счетом, выход которого подключен к ин формационному входу элемента И, управляющи вход которого соединен с первым выходом си хронизатора, а выход элемента И подключен к первому входу счетчика, выход которого соеди ,неи с первым информационным входом схемы сравнения, синхронизирующий вход которой соединен с вторым выходом синхронизатора, второй информационный вход схемы сравнения подключен к выходу блока задания опор-, ных уровней и информационному входу блока памяти, выход которого соединен с входом блока отображения, а управляющий вход подключен к первому выходу блока управления, второй и третий выхо;а.1 которого подключены соответственно к управляющему входу счетчика и первому входу триггера управления счётом, второй вход которого соединен с управляющим входом счетчика, а входы блока управле}шя с первого по третий соединены соответственно с выходами блока выделения экстремума и выходом схемы сравнения. 2. Анализатор, по п. 1, о т л и ч а ю щ и йс я тем, что блок зт1равления содержит элементы И, ИЛИ, триггер запрета, формирователи импульсов и триггер переключения, выходы которого через соответствующие формирователи импульсов подключены к входам триггера запрета, а вход триггера переключения является первым выходом и третьим входом блока и подключен к первому входу первого элемента ИЛИ, выход которого, а также выход второга элемента ИЛИ являются соответственно третьим и вторым выходами блока, при этом первый и второй входы первого элемента И и второй и третий входы второго элемента И соединены соответственно с выходами первого и второго, третьего и четвертого элементов И, первые входы первого и третьего, второго и четвертого элементов И попарно объ единены и являются соответственно вторым и первым входами блока, вторые входы первого и четвертого, второго и третьего элементов И попарно объединены и подключены соответственно к первому и второму выходам триггера запрета. Источники информации, принятые во внимание при экспертизе 1.Слобин Б. 3. и Трофимов О. Ф. Статистический анализ измерений случайной нагруженности для оценки накопления усталостного повреждения. - Вестник мапшностроения, 1966,№ 10. 2.Дмитриченко С. С. Современные методы ускоренных испытаний мапшн на сопротивление усталости. - Вестник мащиностроения, 1967,N 2. 3.Блохин А. Б. Измерение характеристик экстремумов случайных процессов. - Приборы и техника эксперимента, 1970, № 3. 4.Авторское свидетельство СССР N 408317, кл. G 06 F 15/36, 1972 (прототип).

ue.f

Авторы

Даты

1981-10-23—Публикация

1979-09-13—Подача