(54) СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сжатия и передачи телеметрической информации | 1983 |

|

SU1153336A1 |

| Устройство для определения площадей выбросов | 1979 |

|

SU877559A1 |

| СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 1991 |

|

RU2043659C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ВОССТАНОВЛЕНИЯ ТЕХНИЧЕСКИХ СРЕДСТВ МЕДИЦИНСКОГО НАЗНАЧЕНИЯ | 1992 |

|

RU2072788C1 |

| Анализатор спектра Фурье | 1985 |

|

SU1302293A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ИНФОРМАЦИИ В АДАПТИВНЫХ ТЕЛЕМЕТРИЧЕСКИХ СИСТЕМАХ | 1995 |

|

RU2103745C1 |

| Устройство для регулирования расхода жидкости | 1981 |

|

SU999025A1 |

| Многоканальное устройство для передачи информации с дельта-модуляцией | 1982 |

|

SU1166330A1 |

| Анализатор спектра Фурье | 1987 |

|

SU1387010A1 |

| Устройство для поворота вектора (его варианты) | 1982 |

|

SU1078431A1 |

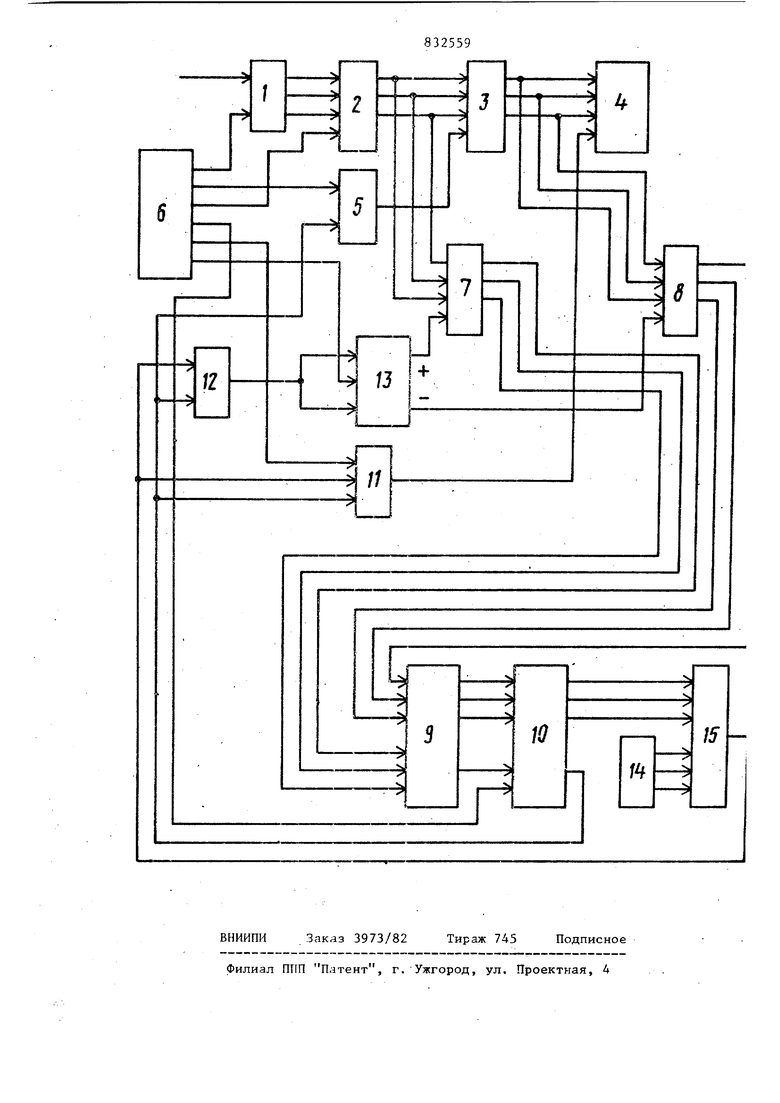

Изобретение относится к вычислительной технике и может найти применение при статистическом анализе случайных процессов. Известно устройство для определения максимального значения функции заданнойчисло-импульсilbiM кодом, которое содержит регистр максимального значения, входы которого связаны со счетчиком времени через вентили, управляющие входы вентилей соединены с выходом схемы И на три входа, вход которой соединены с выходами триггеров и с блоком управления, связанным также с одним входом схемы И на два входа, другой вход которой соединен с выходом одного из триггеров, выходы этого триггера связаны с регист ром максимального значения функции, со вспомо1ательным регистром через входные схемы И соответственно и со входом схемы И, выхоД которой соедине со входом установки О регистра времени максимального значения l. Недостаток этого устройства сос« тоит в том, что оно не определяет минимального значения функции. Наиболее близким по технической сущности к предлагаемому является статистический анализатор, содержащий синхронизатор, аналого-цифровой преобразователь, первый вход которого подключен ко входу статистического анализатора а второй вход - к первому выходу синхрон-изатора, блок элементов И, разрядные входы которого соединены с разрядными выходами аналогоцифрового преобразователя, регистр, входы которого подк.пючены к разрядным выходам блока элементов И, многоканальный регистратор, входы которого соединены с выходами регистра, блок сравнения кодов, первая группа входов которого соединена с разрядными выходами аналого-цифрового преобразователя, вторая группа входов,- с выходами регистра, а вход - со вторым выходом синхронизатора, триттер, вхо- ды которого подключены к выходам блока сравнения кодов, первый переключатель, выход которого подключен к входу блока элементов И, первый и второй входы - к третьему выходу синхронизатора, а третий и четвертый входы - ко входам триггера, второй переключатель, выход которого подключен к управляющему входу многоканального регистратора, первый и вто рой входы - к выходам триггера, а третий и четвертый входы - к четвертому выходу синхронизатора 2. Недостаток такого статистического анализатора - ограниченная точность анализа, обусловленная отсутствием возможности избирательного отбора экстремальных значений. Цель изобретения - повышение точности анализа. Указанная цель достигается тем, что в статистический анализатор, содержащий аналого-цифровой преобразователь, информационный вход которого является входом анализатора, а управ ляющий соединен с первым выходом син хронизатора, выходы аналого-цифрового преобразователя подключены к разрядным входам первого регистра памяти, управляклций вход которого соединен со вторым выходом синхронизатора, многоканальный регистратор, пе вый блок сравнения и триггер, введены второй и Т15етий блоки сравнения, элемент И, сумматор, блок хранения допусков, элементы ИЛИ и ИЛИ-НЕ, вто рой и третий регистры памяти, при этом разрядные выходы первого регист ра памяти подключены соответственно к разрядным входам второго блока сра нения и второго регистра памяти, раз рядные выходы которого соединены соответственно с разрядными входами тр тьего блока сравнения и многоканальнрго регистратора, управляющий вход которого подключен к выходу элемента ИЛИ, первый вход которого соединен с третьим выходом синхронизатора, чет, вертый выход которого подключен к управлякмцему входу третьего регистра памяти, знаковый вход которого подключен к знаковому выходу сумматора, а знаковый выход третьего регистра памяти соединен со вторым входом эле мента ИЛИ, первым входом элемента ИЛ НЕ и первым входом элемента И, второ вход которого подключен к пятому вых ду синхронизатора, шестой выход кото ого соединен с управляющим входом риггера, установочные входы которого объединены и подключены к выходу лемента ИЛИ-НЕ, второй вход которого бъединен с третьим входом элемента ЛИ и соединен с выходом первого лока сравнения, первая группа входов оторого соединена соответственно с ыходами блока хранения допусков, а вторая группа входов подключена соответственно к разрядным выходам третьего регистра памяти, разрядные вхоы которого соединены соответственно с выходами сумматора, первая и вторая группы разрядных входов которого соединены соответственно с выходами второго и третьего блоков сравнения, управляющие входы которых подключены соответственно к выходам триггера. На чертеже показана структурная схема статистического анализатора. Анализатор содержит аналого-цифровой преобразователь(АЩ1 )1, первый регистр 2 памяти, второй регистр 3 памяти, многоканальный регистратор 4, элемент И 5, синхронизатор 6, блоки 7 и 8 сравнеш1я, сумматор 9, третий регистр Ш памяти, элемент ШШ 11, элемент ШШ-НЕ 12, триггер 13, блок 14 хранения допусков, блок 15 сравнения кодов. На первый вход аналого-цифрового преобразователя I поступает аналого-. вый непрерывный во времени электрический сигнал, который с приходом синхроимпульса на второй квантуется по уронвю и преобразуется Б параллельный двоичньШ к.од,каждое дискретное значение которого на выходах АЦП выражает текущее значение отсчета. Синхронизатор 6 вырабатывает серию тактовьк импульсов. Для установления максимума и минимума, входного сигнала и определенияйих значений импульс с одного выхода синхронизатора 6 через элемент И 5 производит запись кода предьщзпдего значения отсчета из регистра 2 памяти в регистр 3 памяти, а импульс с другого выхода синхронизатора 6 производит перепись кода текущего значения отсчета с выходов АЦП в регистр. 2 памяти. Коды предыдущего и текущего значений отсчетов с выходов регистров 2 и 3 памяти поступают на входы блоков 7 и 8 сравнения. Операция вычитания осуществляется с помощью блоIKOB 7 и 8 сравнения и сумматора 9. Независимо от временных характеристик сигнала, отображающего исследуемый процесс(нарастающий или убываюП1ий) всегда из большего значения отсчета вычитается меньшее, при этом знак разности на знаковом выходе сумматора 9 - положительный, а разность в сумматоре - в обратном коде. При появлении экстремального значения знакю разности на знаковом выходе сумматора 9 становится отрицательным, а разность в сумматоре 9 - в прямом ко де. В соответствии с потенциалом на выходах триггера 13 прямой (обратный и обратный (прямой)коды с выходов бл ков 7 и 8 сравнения поступают на вхо ды сумматора 9. Импульс с соответствующего выхода синхронизатора 6 пере писывает значение разности предьруще го и текущего значений отсчетов и знак разности с выхода сумматора 9 в третий регистр.10 памяти. Определени разности предьщущего и текущего зна1чений отсчетов повторяется циклически, с частотой преобразования АЦП, д смены знака разности. Смена знака ра ности (с положительного на отрицатель ный)прои.зойдет при переходе функции через экстремум, закодированное значение которого хранится в регистре 3 памяти. Со знакового выхода регистра 10 памяти на один из входов элемента И 5 поступает потенциал, за пр акшщй запись последующих значени в регистр 3. На одну группу входов блока 15 сравнения(кодов}поступает код разности прёдьщущего и текущего значений отсчетов, на другую группу входов с выхода блока Н хранения допуска поступает значение заданного допуска. Если значение разности меньше значения установленного допуска, то на выходе блока 15 сравнения кодов появится потенциал, запр щающий поступление импульсов с соответствующих выходов синхронизатора через элемент ИЛИ II для запуска регистратора и через элемент ИЛИ-НЕ 12, запрещающий переклн)чение триггера 13. Сравнение разности.между зфанящимся значением отсчета в регистре 3 и значениями текупщх отсчетов,последовательно поступающих в регистр 2с выхода АЦП 1, со значением заданного допуска происходит в блоке 15 сравнения до тех пор, пока значение

.разности или не превысит значения заданного допуска или не изменится знак разности (с отрицательного на положительный) на знаковом выходе регистра 10. В первом случае на выходе блока 15 появится потенциал,разрешаю-, щий прохождение импульса с соответствующего выхода синхронизатора через элемент ШШ 11 на управляющий вход регистратора 4, а также устанавливающий на выходе элемента ИЛИ-НЕ 12 потенциал, разрешающий переключение триггера. 13 импульсом с выхода синхронизатора. При этом регистрируется экстремальное значение, хранящееся в регистре 3 и в соответствии с потенциалами на выходах триггера 13, с выходов блоков 7 и 8 сравнения обратньй (поямой) и прямой (обратный коды регистров 2 и 3. поступают на входы сумматора 9, что приводит к появлению положительного знака разности на знаковом выходе регистра 10 памяти. При этом определение следующего экстремального значения происходит в том же порядке. Во втором случае, когда значения разности между хранящимся значением отсчета в регистре 3 и значениями текущих отсчетов остается меньше заданного допуска, а знак разности изменяется на положительный, на выходе блока 15 сравнения сохраняется потенциал, запрещающий Iпрохождение импульсов с выхода синхронизатора через элемент ШШ 11 на , управлякящй вход регистратора 4 и переключение триггера 13. Пары соседних экстремальных значений,разность между которыми меньше заданного допуска, зарегистрирована не будет, положительный потенциал знака разности поступит на один из входов элемента И 5. в регистр 3 запишется новое (предыдущее)значение отсчета и процесс определения очередного экстремума продолжится по прежнему циклу. После обработки исследуемой еализации02(-Ь)в многоканальном регистраторе накапливается информация плотности распределения максимумов минимумов. Введение ,допол1штельных элементов схему статистического анализатора беспечивает возможность автоматичесого -последовательного определения и оследовательной регистрации значений аксимумов и минимумов случайного роцесса н исключения регистрации соседних экстремальных значений,разность между которыми меньше значения заданного допуска. Таким образом, .предлагаемый статистический анализатор позволяет производить отбор экстремальных значений по заданному допуску, что приводит к повышению точ ности анализа. Формула изобретения Статистический анализатор,содержащий аналого-цифровой преобразователь, информационный вход которого я ляется входом анализатора, а управляющий соединен с первым выходом синхронизатора, выходы аналого-цифро вого преобразователя подключены к разрядным входам первого регистра памяти, управляющий вход которого соединен со вторым выходом синхронизатора, многоканальный регистратор, первый блок сравнения и триггер, о т личающийся тем, что, с цел повьппения точности, он содержит второй и третий блоки сравнения, элемен И, сумматор, блок хранения допусков, элементы ИЛИ и ИЛИ-НЕ, второй и третий регистры памяти, при этом разрядные выходы первого регистра памяти подключены соответственно к раз рядным входам второго блока сравнения и второго регистра памяти, разрядные выходы которого соединены соответственно с разрядными входами третьего блока сравнения и многокана ного регистратора, управляющий вход которого подключен к выходу элемента ИЛИ, первый вход которого соединен с третьим выходом синхронизатора,четвертый выход которого подключен к управляющему входу третьего регистра памяти, знаковый вход которого подключен к знаковомувыходу сумматора, а знаковый выход третьего регистра памяти соединен со вторым входом элемента ИЛИ, первым входом элемента ИЛИ-НЕ и первым входом элемента И, второй вход которого подключен к пятому выходу синхронизатора, шестой выход которого соединен с управляющим входом триггера, установочные входы которого объединены и подключены к выходу элемента ИЛИ-НЕ, второй вход которого объединен с третьим входом элемента ИЛИ и соединен с выходом первого блока сравнения, первая группа входов которого соединена соответственно с выходами блока хранения допусков, а вторая группа входов подключена соответственно к разрядным выходам третьего регистра памяти, разрядные входы которого соединены соответственно с выходами сумматора, первая и вторая группы, разрядных входов которого соединены соответственно с выходами второго и третьего блоков сравнения, управляющие входы которых подключены соответственно к выходам триггера. Источники информации, принятые во внимание при экспертизе 1,Авторское свидетельство СССР № 236855, кл. 6 06 F 7/02, 1967. 2.Авторское свидетельство СССР № 506869, кл. G 06 F 15/36, 1974 (прототип).

Авторы

Даты

1981-05-23—Публикация

1979-07-20—Подача