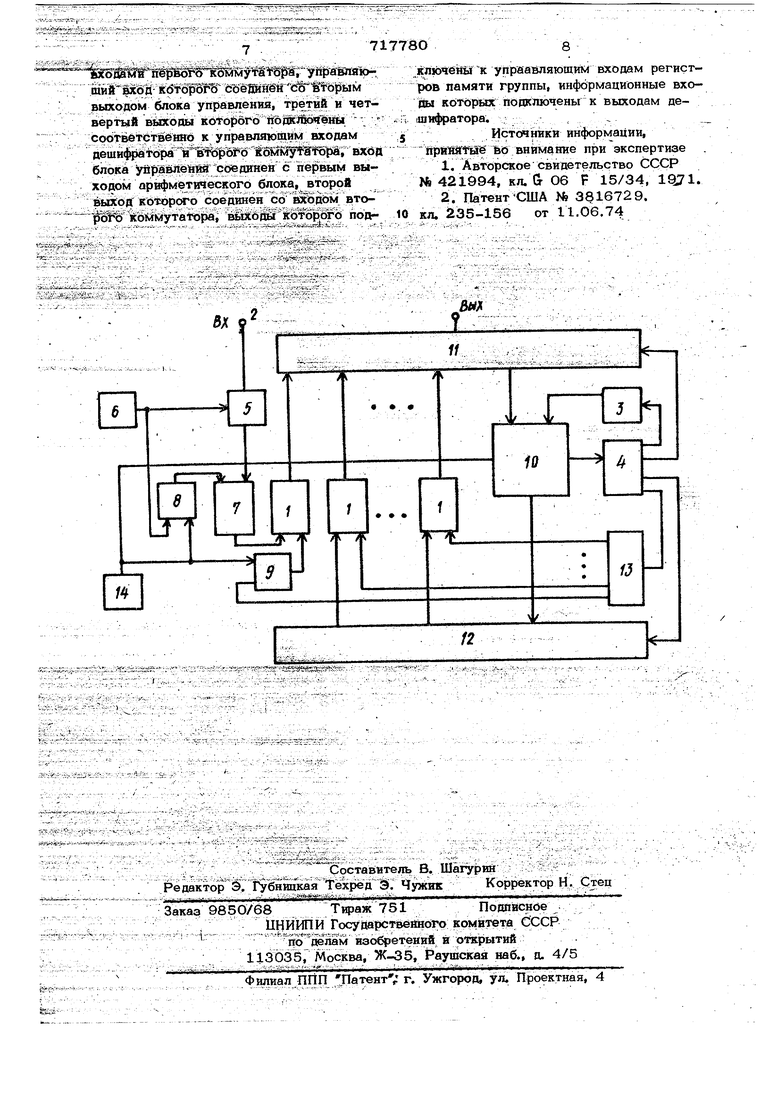

(54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ КОЭФФИЦИЕНТОВ ФУРЬЕ значение вектора nOBoppTff, хранящегося в постоянном запоминающем устройстве (ПЗУ). Выбор необходимого значения вектора поворота.осуществляется с помощью устройства управления. Сдвиг ин формации в регистрах пр6исхопит с частотой аналого-цифрового преобразовател (АЦП) при подаче На все регистры импульсов тактового генератора (ТГ) АЦП Принцип действия вычислителя предусматривает, что в течение первых -S- тактов ТГ, когда заполняется первый блок памяти, все блоки А У бездейiia протяжении - -тактов ствуют/ далее, на протяжении -д работает лишь первый блок АУ, обрабатывающий отсчеты, содержащиеся в первом блоке памяти. Затем в течение -§- тактов работают первый и второй блоки р аспределенного АУ и т.д. Все блоки АУ работают только в интервале между отсчетами входной реализации с номерами N - 1 и Ы . Примем на этом интервале АУ выполняет порядка N операций умножения и сложения комплек ных чисел, что ограничивает быстродействие устройства в реальнок} масштабе времени и требует значительных аппаратурных затрат. Таким образб1М, недостатком известного устройства является недостаточное быстродействие и значи тельное количество ащтаратуры. Цель предлагаемого изобретения заключается в устранении указаннЬйс не достатков, в увеличении быстродействия Цель изобретения достигается тем, что устройство содержит второй генератор импульсов, первый и второй переключатели, группу буферных регистров/ первый и второй коммутаторы и дешифратор, причем выход второго генератора импульсбв подключен к первым входам первого и второго переключателя и первому управляющему входу арифметического блока, второй вход первого переключателя соединен с ыходом первого генератора импульсов, выход - с управляющим входом группы буферньи регистров, информационных Вход которого сое динен с выходом аналогово-пифрового преобразователя, выход группы буферных регистров соединен со входом первого регистра памяти, управляющий вход которого соединен с выходом второго переключателя, второй вход которого подключен к первому выходу де- щи4 атора, выходы регистров памяти соединены со входами первого коммутатора, управляющий вход которого соединен со вторым выходом блока управления, третий и четвертый выходы которого подключены соответственно к управляющим вход.ам дешифратора и второго коммутатора, вход блока управления соединен с первым выходом арифметического блока, второй выход которого соединен со входом второго коммутатора, выходы которого подключены к управляющим входам регистров памяти группы, информационные входы которых подключены к выходам дешифратора. Структурная схема устройства вычисления коэффициентов Фурье дана на чертеже. Устройство содержит групп регистрЪв памяти 1, информационный вход устройства - 2, постоянный запоминающий блок(ПЗБ) -.3, блок управления- 4, аналогово-цифровой преобразователь (АДП) - 5, первый генератор импульсов 6, группа буферных регистров - 7, переключатели 8, 9, арифметический блок 10, коммутаторы 11, 12, дешифратор 13, генератор импульсов 14. Труппа буферных регистров 7 и первая группа регистров памяти 1 имеют количество регистров, равное числу разрядов кода на выходе АДП. Вторая группа регистров памяти 1 имеет две группы регистров, каждая из которых также содержит количество регистров, равное разряднбсти АЦП. В третьем блоке таких групп - четыре, в четвертом 8 и т. д. Длина буферных регистров и регистров первого блока памяти составляет N разрядов, причем, в регистрах первого блока имеется отвод от ячейки с номером-у . Длина регистров второго блока Д- , третьего - и т.д. Устройство работает следующим обра- зом. Входная реализация в аналоговой форме непрерывно поступает на вход АЦП 5. С выхода АЦП 5 дискретные отсчеты с частотой первого тактового генератора 6 в параллельном коде загружаются в буферные регистры, переключатель 8 при этом обеспечивает подачу сигналов первого тактового генератора 6 на синхронизирующий вход группы буферных регистров 7. В тот момент, когда на ёход группы буферных регистров по.ступает отсчет с номером N , срабатывают переключатели 8 и 9 и синхронизирующие входы блока буферных регист- ров первого блока памяти подключаются к выходу второго тактового генератора 14, частота которого выбирается с таким расчетом, чтобы в паузе межпу последни отсчетом предь1дущей реализации и первым отсчетом последующей реализации содержимое группы буферных регистров 7 переписалось в первый регистр памяти 1 После этого переключатель 8 вновь подключает С1шхронизирующие входы блока буферных регистров 7 к выходу тактового генератора и этот блок готов к приему из АЦП отсчетов слегзующей реализации. Одновременно переключатель 9 подсоединяет синхронизирующие входы первого блока регистров памяти 1 к выходу дешифратора 13, а блок управления формирует адрес коммутатора и ПЗБ, соответствующие первым операндам для вычисления. На первом этапе вычислений адрес коммутатора соответствует выходам первого блока регистров памяти и отводам от их ячеек с номерами - . Указанные операнды подаются через коммутатор 11 на входы АУ, которое с высокой скоростью, обусловленной частотой генератора 14 выполняет стандарт ную операцию умножения одного из операндов на вектор поворота и сложения произведения с другим операндом. После выполнения стандартной операции на синхронизирующем выходе АУ 1О формируется импульс управления (ИУ) , сигнализирующий о готовности АУ к следующе операции. Воздействием этого импульса АУ генерирует адрес мультиплексора, соответствующий входам блока регистров памяти и адрес дешифратора 13, с выхода которого поступает сигнал сдвига, на регистры второго блока памяти. Таким образом, в этот блок заносятся результаты вычислений арифметического блока. Одновременно БУ (4) формирует адреса коммутатора 11 и ПЗБ 3, а также адрес дешифратора для сдвига информации в первом блоке памяти 1. После этого на вход арифметического блока 10 поступают операнды для выполнения следующей стандартной операции. Описанная процедура выполняется -т- раз, пока не заполнятся регистры второго блока памяти. После этого А У аналогичным образом производит операции с данными, содержащимися в первом и втором блоках памяти, снимая соответствующие ; операнды с входов и вьосодов регистров. При этом результат стандартной операции над данными первого блока aaiioсится во второй блок, вытесняя хранящиеся в нем операнды, которые в свою очере поступают на арифметическпй блок, а результат вычислений над ними зпиосится в третий блок. После ,N интеграции в регистрах последнего блока п.-ьпяти содержатся N коэффициентов Фурье, которые могут быть последовательно извлечены с частотой генератора 14 за время равное гаузе между отсчетами входной реализации. При выборе элементной базы, обеспечивающей время умножения порядка 20О не. Описанное устройство способно в реальном масштабе времени выполнять преобразования Фурье от 1О24 точек за время порядка 2 мс. Для того, чтобы получить такое быстродействие в устройстве - прототипе, при равной сложности арифметического устройства необходимо использовать элементы, обеспечивающие время умножения менее 10 не, или пропорционально увепичить объем аппаратуры в А У. Формула изобретени5г Устройство для вычисления коэффициентов Фурье, содержащее аналоговодифровой преобразователь, информационный вход которого соединен со входом устройства, управляющий - с выходом первого генератора импульсов,Вptfj. групп регистров памяти, где N - количество коэффициентов Фурье, постоянный запоминающий блок, вход которого соединен с -первым выходом блока управления, выход - с первой группой входов арифметического блока, отличаюш е ее я тем, что, с целью повышения быстродействия устройства, оно содержит второй генератор импульсов, первый и второй переключатели, группу буферных регистров, первый и второй коммутаторы и дещифратор, причем выход второго генератора импульсов подключен к первым входам первого и второго переключателя и первому управляющему входу арифметическЬго блока, второй вход первого переключателя соединен с выходом первого генератора импульсов, выход - с управляющим входом группьт буферных регистров, информационный вход которого соединен с выходом аналого-цифрового преобразователя, выход группы буферных регистров соединен со входами первого регистра памяти, управляющий вход которогосоединен с выходом второго переключателя, второй вход которого подключен к первому выводу дешифратора, выходы регистров памяти соединены со

слзл1Ц :

:ешгкт-тш рог тш Ш Ш 8р1Гу

выходом блока управления, третий в четвертый выходы котордго itonKJilo4eiflii ° , соответственно к управляющим входамj

деши4 тора VTfixipoioKoMiayflrfopa, вход блока управлений соединен с первым выходом арифметического блока, второй выход которся о соединен со входом втоpot o KOMMyTatopa, вькоды которого под- 10

viisasssSi

- f -t - ---,-« fU:

клйчёйыЧс упраавляюшим входам регистров памяти группы, информационные входы которых подключены к выходам де1шнфратора.,

Источники информации, принятые Во внимание при экспертизе

1.Авторское свидетельство СССР

№ 421994, кл. & 06 F 15/34, 19J71.

2.ПатентСША № 3816729. кл. 235-156 от 11.06.74

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления коэффициентов фурье | 1976 |

|

SU643889A1 |

| Цифровой спектроанализатор | 1982 |

|

SU1092518A1 |

| Устройство для реализации двумерного быстрого преобразования фурье | 1983 |

|

SU1142845A1 |

| Устройство для вычисления - точечного преобразования фурье | 1978 |

|

SU746539A1 |

| Устройство для быстрого преобразования Фурье | 1985 |

|

SU1304034A1 |

| Процессор быстрого преобразования Фурье | 1986 |

|

SU1388892A1 |

| Вычислительное устройство | 1980 |

|

SU1022158A1 |

| Устройство для формирования адресов процессора быстрого преобразования фурье | 1987 |

|

SU1499373A1 |

| Устройство для реализации двухмерного быстрого преобразования Фурье | 1982 |

|

SU1164730A1 |

| Процессор быстрого преобразования Фурье | 1985 |

|

SU1247891A1 |

xfc SfS :i ffl:; S -a«:ass: : 9B

Авторы

Даты

1980-02-25—Публикация

1977-09-12—Подача