первый и второй выходы блока готовности операвдов соединеяы с информационными входами первогои второго триггеров прерывания соответственно, вьйсод первого триггера прерывания соединен с нулевым входом второго триггера прерывания и первым управлязошим входом коммутатора синхросигналов, выход второго триггера прерывания соединен с нулевым входом первого триггера прерывания и вторым управля эщим входом коммутатора синхросигналов, информационные входы которого соединены с первым и вторым выходами генератора синхросигналов, синхровходы первого и второго триггеров прерывания соединены с вторым и первым выходами генератора синхросигналов соответственно, информационные входы регистра множимого и фарных блоков памяти множителя и слагаемого соединены с информапионнЬй шиной устройства, выход буферного блока памяти слагаемого соединен с информационной шиной устройства, вторые адреные входы буферных блоков памяти множтеля и слагаемого соединены с адресной шиной устройства, входы управления вводом-вьшодом буферных блоков памяти множителя и слагаемого соединены с шиной запросов устройства, первый выход блока параллельного запроса операндов соединен с улравляюшим входом записи буферного блока памяти слагаемого, выходы коммутатора синхросигналов соединены с синхровходами регистров адреса и входом блока параллельного запроса операндов.

2. Устройство по п. 1, о т л и ч а ю щ е е с я тем, что, блок меток операндов содержит дешифраторы, регистры, триггеры, элементъ И и ИЛИ, причем входы первого, второго и третьего дешиф раторов соединены с пятым, вторым и третьим входами блока, выходы первого н второго дешифраторов соединены с первыми входами элементов И первой и второй групп, вторые входы которых соед1шены с седьмым и первым входами блока соответственно, выходы элементов И первой и второй групп соединены нулевыми и единичными установочными входами разрядов первого регистра соответственно, выходы которого соединены с первыми входами элементов И третьей группы, вторые входы которых соединены с выходами третьего дешифратора, Бьрсоды элементов И третьей группы соединены с входами первого элемента , выход которого соединен с первым в укодом блока, входы четвертого и пятого дешифраторов соединены с шестым и вторым входами блока .соответственно, выходы которых соединены с первыми входами элементов И четвертой и пятой групп соответственно, вторые входы которых соеаиненыг соответственно с седьмьм и первым входами блока, выходы элементов И четвертой и пятой групп соединены с нулевыми и единичнымк установочными входами разрядов второго регистра соответственно, выхода которого соединены с первыми входами элементов И шестой и седьмой групп, выходы которых подключены к входам второго и третьего элементов ИЛИ соответственно, выходы которых соединены соответственно с вторым выходом блока . и первым входом блока, нулевой и единичный входы триггера подключены к седьмому и первому входу блока соответст венно, а выход - к третьему выходу блока и первому входу блока, вторые входы : элементов И шестой группы соединены с выходами шестого дешифратора, входы которого соединены с четвертъ1М входом блока, вторые вхо.аы элементов И седьмой группы соединены с вько,аами пятого дешифратора.

3.Устройство по п. 1, о т л и - чающееся тем, что блок параллельного запроса операщюв содержит счетчик, дешифратор микроопераций и четыре триггеры, информационные входы которых соединены с выходами дешифратора микроопераций, пятый выход которого подключен к пятому выходу блока, входы дешифратора микроопераций соединены с выходами счетчика, вход которого соединен с входом блока и синхровходами

-триггеров, выходы которых соединены с соответствующими выходами блока.

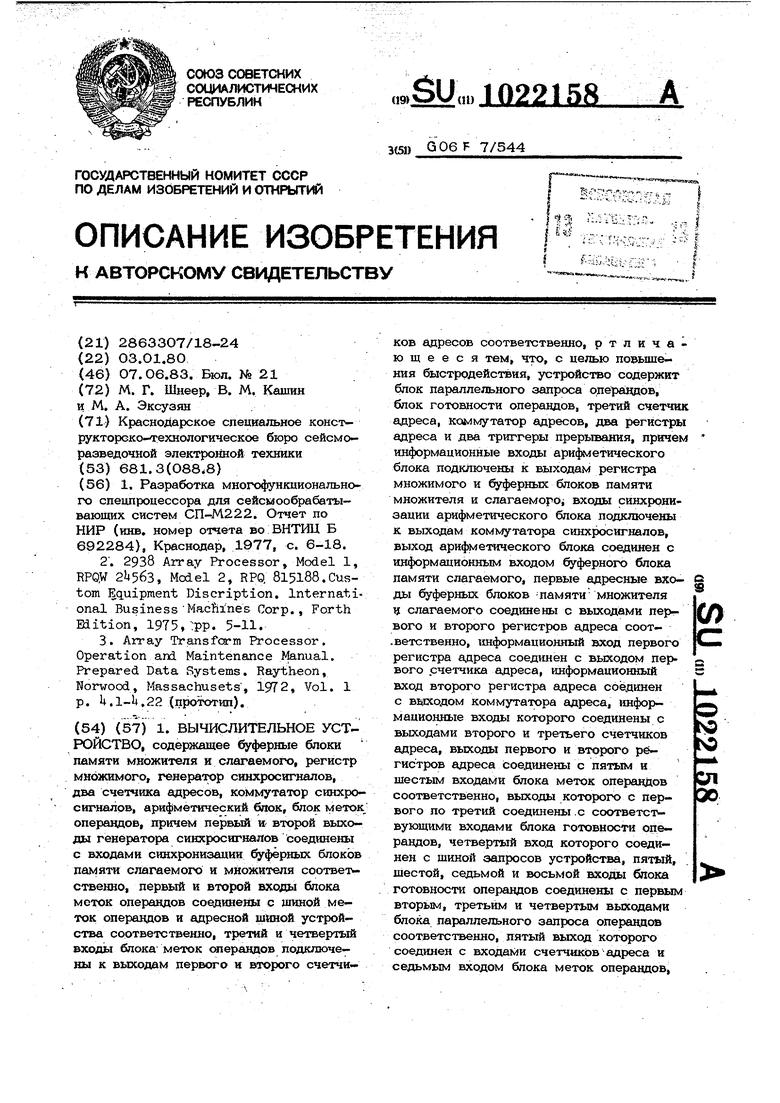

4.Устройство по п. 1, о т л и ч а ю щ е е с я тем, что блок готовности операвдов содержит элементы И и ИЛИ, причем входы первого элемента ИЛИ соединены с выходами элементов И с первого по третий, а выход соединен с первым выходом блока, входы второго лемента ИЛИ соединены с выходами

Элементов И с четвертого по шестой, а выход соединен с вторым выходом блока, первые входы первого, второго и третьего элементов И соед1шены соответственно с пятым, шестым и седьмым входами блока, первые входь четвертого, пятого и шестого элементов И соединены соответственно с шестым, седьмым и восьмым входами блока, вторые входа первого и пятого элементов И соеди-ментов И соединены соответственно с

нены с четвертым входом блока, вторыепервым, вторым и третьим входами бповходы второго, третьего и шестого эле- . ка.

1022158

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Устройство управления последовательностью операций цифрового вычислителя | 1984 |

|

SU1198521A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Специализированный процессор для вычисления элементарных функций | 1985 |

|

SU1330627A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1559340A1 |

| Устройство для вычисления матрицы направляющих косинусов | 1983 |

|

SU1233142A1 |

| Устройство для умножения | 1984 |

|

SU1176325A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для буферизации команд | 1991 |

|

SU1789982A1 |

| Устройство для вычисления полиномов | 1986 |

|

SU1432509A1 |

1. ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО, содержащее буферные блоки памяти множителя н слагаемого, регистр множимого, генератор синхросигналов, два счетчика адресов, коммутатор синхросигналов, арифметический блок, блок меток опера1здов, причем первый к второй выходы генератора синхросигналов соединены с входами синхронизации фёрньк блоков памяти слагаемого и множителя соответственно, первый и второй входы блока меток операндов соединены с шиной меток операндов и адресной шиной устройства соответственно, третий и четвертый входы блока меток сятерандов подключены к выходам первого и второго счетчиков адресов соответственно, р т л и ч а ю ш е е с я тем, что, с целью noBbmieния быстродействия, устройство содержит блок параллельного запроса опёраэдов, блок готовности операндов, третий счетчик адреса, коммутатор адресов, два регистры адреса и два триггеры прерьшания, причем шф)рмационные входы арифметического блока подключены к выходам регистра множимого и буферных блоков памяти множителя и слагаемого входь синхронизации арифметического блока подключены к выходам коммутатора синхросигналов, выход арифметического блока соединен с информационным входом буферного блока памяти слагаемого, первые адресные входы буферных блоков -памяти множителя Ч слагаемого соединены с выходами первого и второго регистров адреса соот.ветственно, тшформационный вход первого регистра адреса соединен с выходом первого счетчика адреса, информационный вход второго регистра адреса соединен с выходом коммутатора адреса, инфорО мационные входы которого соединены с э д выходами второго и третьего счетчиков адреса, выходы первого и второго регистров адреса соединены с пятым и СП шестым входами блока меток опера1одов 90 соответственно, выходы которого с первого по трютий соединены .с соответствующими входами блока готовности операндов, четвертый вход которого соединен с шиной запросов устройства, пятый, шестой, седьмой и восьмой входы блока готовности операндов соединены с первым вторым, третьим и четвертым выходами блока параллельного запроса операщюв соответственно, пятый выход которого соединен с входами счетчиков адреса и седьмым входом блока меток операндов.

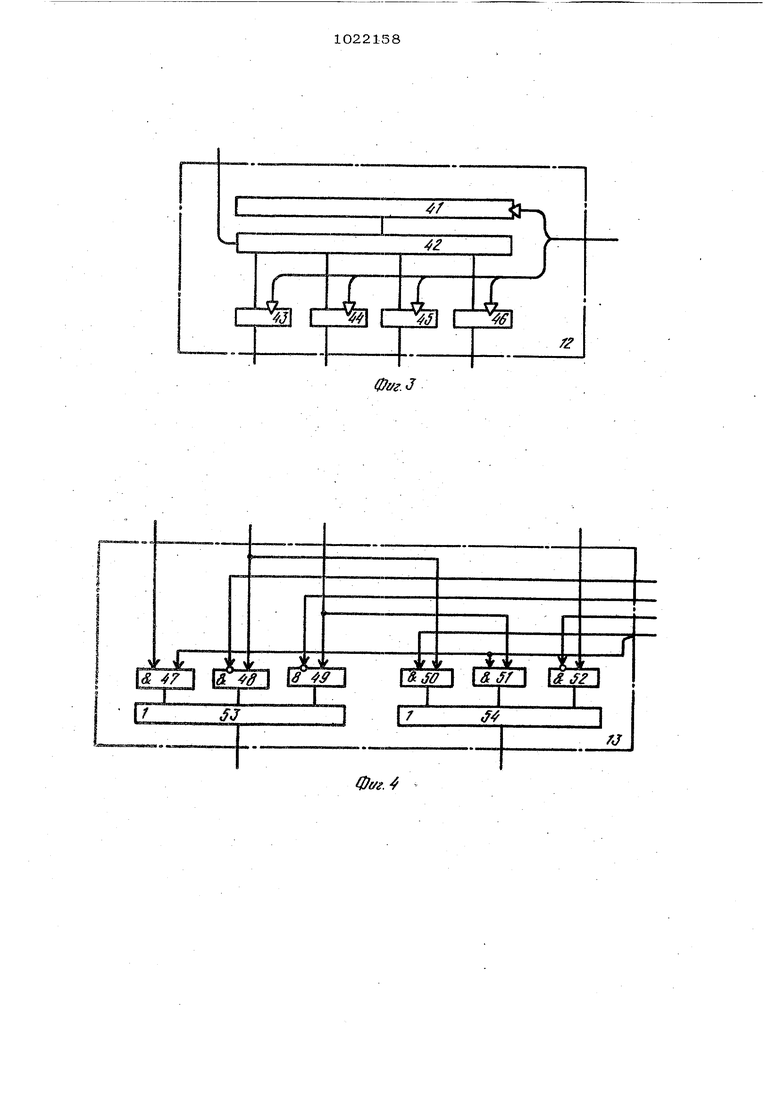

Изобретение относится к вычислитель ной технике и может найти применение в специализированных цифровых вычисли тельных машинах. Известны вычислительные устройства ориентированные на выполнение парной операции по формуле 7. U -v Y, где X - множитель, U - множимое и ( - слагаемое. Такие устройс-гаа соедержат буферные блоки памяти множителя и слагаемого, счетчики адресов, регистр множимого, арифметический блок (последовательного или параллельного действия) и генератор синхросигналов 1 и 2. Однако в этих устройствах арифметические блоки начинают функционировать после ввода группы множителей и слагае мых в ферные блоки памяти по поступ нию операнда в регистр множимого, что не позволяет полностью совместить во времени обработку с вводом операндов. Наиболее близким к предлагаемому является устройство, содержащее буферн блоки памяти множителя и слагаемого, регистр множимого, счетчики адресов, генератор синхросигналов:, коммутатор синхросигналов, ари4метический блок и блок меток операндов, подключенный к вьссодам счетчиков адресов 3. Недостатком известного-устройства является то, что последовательный анализ меток операндов, не совмещенный с работой арифметического блока, 1фиводит к потерям времени. Цель изофетения - повышение быстродействия устройства. Поставленная цель достигается тем, что в устройство, содержащее буферные блоки памяти множителя и слагаемого, регистр множимого, генератор синхросигналов, два счетчика адресов, коммутатор синхросигналов, ари4я«1етический блок, блок меток операндов, причем первый и второй выходы генератора синх росиг::алов соединены с входами синхро низации буферных блоков памяти слагаемого и множителя соответственно, первый и второй входь блока, меток операндов соединены с игайой меток операндов и адресной щиной устройства соответственно, третей и четвертый входы блока меток операндов подключены к выходам первого и второго счетчиков ресов соответственно, введены блок параллельного запроса операндов, блок готовности операндов, третий счетчик адреса, коммутатор а,цресов, два регистры адреса и два триггеры прерывания, причем информационные входы ари4«иетяческого блока подключены к выходам регистра множимого и буферных блоков памяти множителя и слагаемого, вкооы сийхрони&ации ; арифметического блока подключены к вь1ходам коммутатора синхросигнале выход арифметического блока соединен с {информационным входом у рвого блока памяти слагаемого, первые адресные входы буферных блоков памяти множителя и слагаемого соединены с. выходами iпервого и второго регистров адреса соответственно, информационный вход первого регистра адреса соединен с выходом первого счетчика адреса, информационный вход второго регистра адреса соединен с выходом коммутатора адреса, информационные входы которого соединены с выходами второго и третьего счетчиков адреса, выходы первого и второго регистров адреса сое щшены с пятым и шестым входами блока меток операндов соответственно выходы которого с первого по третий соедшюны с соответствующими входами блока готовности операндов, четвертый вход которого соединен с шиной запросов устройства, пятый, шестой седьмой и восьмой входы блока готовности сшераддов соединены с первым, вторым, третьим и четвертым выходами блока параллельного запроса операндов соответственно, пятый выход которого соединен с входами счетчиков адреса и седьмым входом блока меток операндов, первый и второй выходы блока готовности операндов соединены с информационными входами первого и второго триггеров прегяьшания соответственно, выход первого триггера прерывания соединен с нулевым входом второго триггера прерьгоания и первым управляющим входом коммутатора синхросигналов, выход второго триггера прерьюания соединен с нулевым входом первого триггера прерьшания и вторым управляющим входом коммутатора синхросигналов, информационные входы которого соединены с первым и вторым вькодами генератора синхросигналов, синхровходы первого и второго триггеров прерывания соединены с вторым и первым выходами генератора синхросигналов соответственно, информационные входы регистра множимого и ферных блоков памяти множителя и слагаемого соеданены с информационной шиной устройства, выход буферного блока памяти слагаемого соединен с информационной шиной устройства вторые адресные входы буферньюс блоков множителя и слагаемого соединены с адресной шиной устройства, входы управленш вводом-выводом буферных блоков памяти множителя и слагаемого соединены с шиной запросов устройства, первый выход блока параллельного запроса операндов соединен с управляющим входом записи ферного блока памяти слагаемого, выходы комклутатрра синхросигналов соединены с синхровходами регистров адреса и входом блока параллель ного запроса операндов. Кроме того, блок меток операндов содержит дешифраторы, регистры, тригге ры, элементы И и ИЛИ, причем входы первогО| второго и третьего дешифраторов соединены с пятым, вторым и треть им входами блока, выходы первого и вто рого деши торов соедннены с первыми входами элементов И первой и второй групп, вторые входы которвдх соединены с седьмым и первым входами блока cooi ветственно, взыходы элементов И первой и второй групп средвнены с нулев1 1ми и единичными устаж вочными входами разрщюв nepfioro регистра соответственно, выходы которого соединены с первыми входами эл лентов И третьей грутшы вторые входы которых соединены с вы- ходами третьего дедп ратора, выходы элемента И третьей группы соеданены с входами нер&ого элемента ИЛИ, выход KoTopoix) сосуЕШНея с первым вызсодом блока, входы четверпяго и пятого раторов соедннены с шестым и BTopidM входами блока соответственно, выходь которых соединены с первыми входами элементов И четверткой и пятой групп соответственно, вторые входы которых соединены соответственно с седьмым и первым входами блока, выходы элементов И четвертой и пятой групп соединены с нулевыми и. единичными установочными входами разрядов второго регистра соответственно, выходы которого соединены с входами элементов И шестой и седьмой групп, выходы которых подклкмены к входам второго и третьего элементов ИЛИ соответственно, выходь которьа соединены соответственно с вторым ы 1ходом блока и первым входом блока, нулевой и единичный входы триггера подключены к седьмому и первому входу блока соответственно, а выход - к третьему выходу блока и первому входу блока, вторые входы элементов И шестой группы соединены с выходами шестого дешифратора, входь которого соединены с четвертым входом блока, вторые входы элементов И седьмой группы соединены с выходами пятого деши4 тора. Причем блок параллельного запроса операндов содержит счетчик, дешифратор микроопераций и четыре триггеры, информационные Bxojubi которых соединены с выходами дешифратора микроопераций, пятый выход которого подключен к пятому выходу блока, выходы дешифратора микроопераций соединены с вькодами счетчика, вход которого соединен с входом блока и синхровходами триггеров, выходы которых соединены с соответствующими выходами блока. При этом блок готовности операндов содержит элементы И и ИЛИ, причем вход1 1 первого элемента ИЛИ соеданены с выходами элементов И с первого по третий, а выход соединен с первым выходом блока: входы второго элемента ИЛИ соединены с выходами элементов И с четвертого по шестой, а выход с оединен с вторым выходом блока, первые входы первого, второго и третьего элементов И соединены соответственно с пятым, шестым и седьмым входами блока, nefSbie входы четвертчих), пятого и шестого элементсш И соединены соответственно с шестым, седьмым и восьмым входами блока, вторые входы nepiBoro в пятого элементов И соедвневы о четверпдм входом блока, вторые входы второго, третьего и шестого элементчж И доедннены соответственно с первым, вторым и третьим вэсодами блока. На фиг. 1 показана схема вычислительного устройства; на фйг. 2 - то же блока меток операндов; на фиг- 3 - то же, блока параллельного .запроса операн дов; на фиг. 4 - то же, блока готовностй операндов; на фиг. 5 - временная диаграмма работы устройства. Вычислительное устройство (фиг. 1) содержит буферные блоки памяти множителя 1 и слагаемого 2, регистр 3 множимого, генератор 4 сщссросигнапов два счетчика 5 и 6 адресов, коммутатор 7 синхросигналов, арифметический блок 8, блок 9 меток операвдов, шину 1 меток операндов, адресную шину 11 уст ройства, блок 12 параллельного запроса операндов, блок 13 готовности операндов, третий счетчик 14 адреса, коммутатор 15 адреса, два ретист1ил 16 и 17 адреса, два триггеры 18 и 19 пре- рьтания, информационную шину 20 устройства и шину 21 запросов устройства. Блок 9 меток операндов {фиг. 2) содержит шесть дешифраторов 22-27, два регистры 28 к 29, семь групп элементов И ЗО-36, три элемента ИЛИ 37-39 и триггер 40. Блок 12 параллельного запроса операндов (фиг, 3) содержит счетчак 41, дешифратор 42 микроопераций и четыре триггеры 43-46. Блок 13 готовности операндов содержит шесть элементов И 47-52 и два элемента ИЛИ 53 и 54. Устройство работает следующим образом. Опёрад{Ш в вычислительное устройство поступают по информацисжным входам регистра 3 мнозкимого и буферных блоков памяти множителя I и слагаемого 2. Результаты вычислений выводятся по информационной шине 2О устройства, соединенной с выходом блока памяти слагаемого, в котором накапливаются результаты вычислений арй етического блока 8. Ввод операндов и вывод резуль татов осуществл5потся по сигналам, поступающим по шине 21 запросов устройства, связанной с управляющими входами буферных блоков памяти множителя 1 и слагаемого 2. Ввод операндов сопровохдзаефся уста новкой меток операндов по сигналам, поступающим по шунаправленной шине 10 меток операндов, причем к:аждому вводимому операнду соответствуют свои метки. При установке метки множителя вводимого операнда сигнал по адресной шине 11 поступает в бпо«: 9 ва ъ-юрой 1дешифратср 23, а при установке метки слагаемого - на пятый дешифратор 26, Открываются соответствующие адресу, операнда элементы И второй 31 и пятой 34 , через которые сигнал записи метки операнда поступает на единичные входы первого и второго регистров |28 и 29. В случае установки метки множимого запись метки производится в триггер 4О без дешифровки адреса, кай регистр 3 рассчитан на один ;операнд. Ввод операндов производится асинхооно с работой вычислительного устройств ва. Для синхронизации блоков устройства служит генератор 4 синхросигналов, который вырабатывает четыре последовательности синхросигналов: две некомму тируемые и две проходящие через коммутатор 7 синхросигналов. , Период следования синхросигналов определяет длительность парной операции в ари(метическом блоке 8 (фиг. 5), который имеет конвейерн5гю структуру, ив нем одновременно выполняется перемножение двух операндов и подсумми|ювание слагаемого к произведению Полученного в предыдущем периоде. Некс лмутируемые синхросигналы первого и второго выходов генератора 4 синхросигналов соединены с входами синхронизации буферных блоков памяти множителя 1 и слагаемого 2 и используютуся для обслужтзания циклов чтения и записи операндов.. Буферные блоки 1 и 2 памяти допускают два обращения на чтение или запись операвиюв в течение периода парной операции, причем чтение операндов осуществляется во второй половине периода, а запись результатов ft буферный блок 2 памяти слагаемохх) - в первой половине периода. Это распределение времени в течение периода не распространяется на ввод и вьшод операндов по информационной шине устройства. Синхросвгналы с выхода .коммутатора 7 синхросигналов поступают ва синхровход счетчика 41 блока 12 параллельного запроса операндов и изменяют его состояние. о состоянии счетчика 41 поступает на вход дешифратс в 42 мшфо (шерацнй, в котором, в зависш«ости от шлполняемой процедуры, запрограммяро- ващ, Бакие и операндов требуются ддя . вшюлнення спедукшей паркой операции. Установка запросов на множитель, слагаемое и множимое осуществляется на втором, третьем к четъертом триггерах , соответствевно, а первый триггер 43 служит для установки аапрсхза на запись результатов в.блок 2 буферной памяти слагаемого. Причем установка первого, второго и третьего триггеров 4345 происходит по одному сшссросигналу, а триггера 4 другому синхросигналу. Проверка наличия требуемых операндов в вычислительном устройстве, а также незанятость соответствукмаего ферного блока памяти, осуществляется в блоке 13 готовности операндов по сигналам запросов от блока 12 и прочитанным меткам операндов из блока 9 меток операндов. Считывание меток множителя и слагае мо1) происходит путем дешифрирования адресов множителя и слагаемого, поступающих на третий и шестой дешифраторы 24 и 27 блока 9 от первого 5 и второго 6 счетчиков адреса соответственно. Открываются соответствующие адресам элементы И третьей 32 и шестой 35 групп, через которые метки операндов с выходов первого и второго регистров 28 и 29 поступают на входы первого и второго элементов ИЛИ 37 и 38 на первый и второй выходы блока 9, сое диненные с первь0и и вторым входами блока 13, Метка множимого с выхода триггера 40 поступает на третьи входы блока 9 и блока 13.. На элемент И 47 поступают сигналы Збшроса на запись результата с первого выхода блока 12 и сигнал запроса по шине 21 на обслуживание буферным блоком 2 памяти слагаемохх). На элемент И 48 поступает сигнал запроса на чтение множителя с второго выхода блока 12 и метка множителя с первого выхода блока 9; На элемент И 49 посту- пает сигнал запроса на чтение слагаемого с третьего выхода блока 12 и метка слагаемого с второго выхода блока 9. На элемент И 50 поступает сигнал за- проса на чтение множителя от блока 12 и сигнал запроса по шине 21 на обслуживание буферным блоком 1 множителе. На элемент И 51 поступает сигнал запроса на чтение слагаемого от блока 12 и сигнал запроса по шнне 21 на обслуживание буферным блоком 2 памяти слагаемого. На элемент И 52 поступает сигнал запроса на множимое с четаертого выхода блока 12 и метка множимого с третьего выхода блока 9. В случае, когда любой из выходов (с первого по ..Четвертый) блока 12 находится в акт«внскм состоянии, но гребу&мъЛ операнд не обеспечен меткой, т.е. он еще не поступил в вычислительное устройство, или буферный блок памяти имеет запрос на обслуживание по шине 21, имеющей более высокий приоритет, то срабатывают соответствукицие элементы И 47-52, и через элементы ИЛИ 53 и 54 сигналы поступают на первый и второй выходы блока 13 готовности стерандов и далее на информационные входы первого и второго триггеров 18 и 19 прерывания, синхровходы которых соединены с некоммутируемыми выходами генератора синхросигналов. В моменты времени, определяемые синхросигналами, триггеры 18 и 19 при наличии сигнала на информационном входе устанав ливаются в состояние прерывания выполняемой процедуры путем подачи запрещающих сигналов на управляющие входы коммутатора 7 синхросигналов. Этим блокируется поступление коммутируемых, синхросигналов ко всем блокам устройства и обеспечивается режим хранения информбшии во всех блоках. В состоянии прерывания функционируют только буферные блоки 1 и 2 памяти, которые могут в это время обслуживать запмюы по шине 21. . Для предотвращения установки второго (первого) триггера 19 (18) в состояние прерывания в то время, когда первый (второй) триггер 18 (19) уже находался в этом состоянии, выход первого триггера 18 соединен с нулевым входом второго триггера 19, а выход последнего с нулевым входе первого триггера 18. Как только причина, вызвавшая прерывание будет уст инёна, т.е. появится требуемый операнд или освободится мый буферный блок памяти, триггеры прерывания 18 и 19 по очередному некоммутируемому синхросигналу переключаются и снимают запрет на прохождение к {мутируемых сиюфосигналов хо всем блокам, в том числе ш.к счетчику 41 блока 12, обеспечивая дальнейщее продвижение по алгоритму выполняемой процедуры. По сигналам дешИ|} тора 42 микроопераций, поступающих на пятый блока 12 параллельного запрора операндов, переключаются первый, второй и третий счетчики 5, 6 и 14 адреса, а содержимое счетчиксж адреса переписывается в первый,и втчфой регистры 16 и 17 адреса, причем во второй регистр 17 адреса через коммутатор 15 адреса, который во второй поповиве периода парной операции пропускает ajqpec от счетчика 14 на запись результата в буферный блок 2 памяти слагаемого, а в nepiaofl половине - адрес от счетчика 6 на чтение слагаемого. Запрос на обслуживание записи резуль тата поступает с первого гаыхода блока 12 на управлякяций вход записи буферного блока 2 памяти слагаемого. Запросы в буферные блоки памяти на чтение операвдов для арифметического блока 8 не подаются, так как при отсутствии запроса на запись выполняется чтение операндов. Адреса оперзддов, вводимых и выводимых по инфо1мационной шине 2О устройсо ва, подак тся по адресной шине 11 на вторые ащюсные входы буферных блоков памяти множителя 1 и слагаемого 2 а адреса операндов для арифметического блока 8 - на першле адресные входы блоков i и 2. Сюда же поступает адрес записываемого результата в буферный блок 2 памяти слагаемого. Приоритетные схемы блоков 1 и 2 памяти при наличии запросов по шине 21 пер к,шочают адрес с первых адресных входов на вторые. При выполн@1ии чтовия операнда из буферного блока 1 naMsrra множителя и регистра 3 множимого по сигналу от бпо ка 12 параллельного запроса операндов, поступающему на седьмой вход блока 9 меток шерандов происходит сбрею меток читаемых операндов в первом регистре 28 и триггере 4О, причем в регистре 28 только в. ячейке выфанной по нулевому входу элементом И первой группы ЗО выбранной) в свок очередь, первым дешифратором по адресу, постзшйвшему на пятый вход блока 9 от первого регистра 16 адреса. В сштачие от сфрса меток множителя и множимого, сброс метки слагаемого осуществляется не в момент чтения операнда а во время запи си результата. Пря этсиу адрес поступает во втором регистре 17 адреса на четвертый д оифратор блока 9, срабатыва соответствующий элемент четвертой группы 33 и обнуляется ячейка второго регистра 29. При запросе на вьшод операнда из вычислительного устройства по шине 20 адрес операнда поступает на пятый де- ши4чратор 26, и метка результата через : соответствующий элемент И. седьмой группы 36 и третий элемент ИЛИ 39 поступает на двунаправленную шИну 1О меток операндов. Сюда же поступает метха множимого с выхода триггера 40. По состоянию меток результата и м11ржим.ого внешнее устройство, осуществляющее ввод и вывод операндов, организует работу по выгрузке результатов и загрузке очередных множимых. Предлагаемое техническое решение позволяет совместить во времени выполнение а1%фметичес|сих операций над некоторой совокупностью операндов для одной парной операции с анализом готовности следукицей группы операндов для другой парной операции. Кроме того, экономия времени в предлагаемом устройстве продсхояит за счет того, что потери времени на синхронизацию в случае него.товности операндов или буферных запоминающих устройств сведены к минимуму : проведением анализа готовности операндов к двум моментам времени в течение периода паркой операции. Быстродействие помышается в 1,2-2 ра- . за по сравнению с известными технически:ми решени$олк, что снижает йатраты : машинного времени ушверсальной ЭВМ . в кшшлексе, с которой работает специализированный процессор. Экономия машинного времени универсальной ЭВМ особенно важна при обработке сейсмической И1 Ьрмации,|:,- характеризующейся большими массивами данных и .временными процедурами обработКЕ (например, свертка, быстрое лреобра. зование Фурье, ревурсивная фильтрация в щ.).

pAI /

/

fff

Фиг. 1 .

Ф&г.1

Фаг.

Фег.

e,7ff vfff/ f /ff/ff &yv eff / f /7ife ff

/7fat/od

ffffff ffjf fffffjffff y

фуг.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Камневыбирательная машина | 1921 |

|

SU222A1 |

| Отчет по НИР (инв | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| International BusinessMacfiines Corp., Forth mition, 1975, :pp | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Operation ani Maintenance Manual | |||

| Prepared Data Systems | |||

| Raytheon, Norwood, Massachusets, 1972, Vol | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1983-06-07—Публикация

1980-01-03—Подача