которого соединен со вторым информационным входом вычитателя, информационный выход которого соединен с ииформадионным входом преобразователя двоичного кода в число-импульсный, информационный выход которого соединен со входом запуска первого генератора импульсов, выход которого соединен с управляющим входом второго блока памяти, выход переполнения второго сумматора соединен с первым входом третьего сумматора, входом запуска первого генератора импульсов, первым входом элемента И, входом элемента задержки и входом запуска второго генератора импульсов, выход которого соединен с управляющими входами регистров группы, информационные выходы которьх подключены ко второму информационному входу второго сумматора, управляющий вход которого соединен с выходом элемента И, второй вход которого соединен с выходом элемента задержки, выход блока выбора максимального числа соединен со вторым входом третьего сумматора, выход которого является выходом порядка спектроанализатора, девятый выход распределителя импульсов соединен со входом четвертого дешифратора адреса, выход которого соединен с адресным входом блока регистро вой памяти, десятый, одиннадцатый, венадцатый, тринадцатый и четырнада1ый выходы распределителя импульсов соединены соответственно с тактовым входом сдвигового регистра, тактовым входом блока выбора максимального числа, управляющим входом вычитателя, тактовым входом преобразователя двоичного кода в числоимпульсный и третьим входом элемента И.

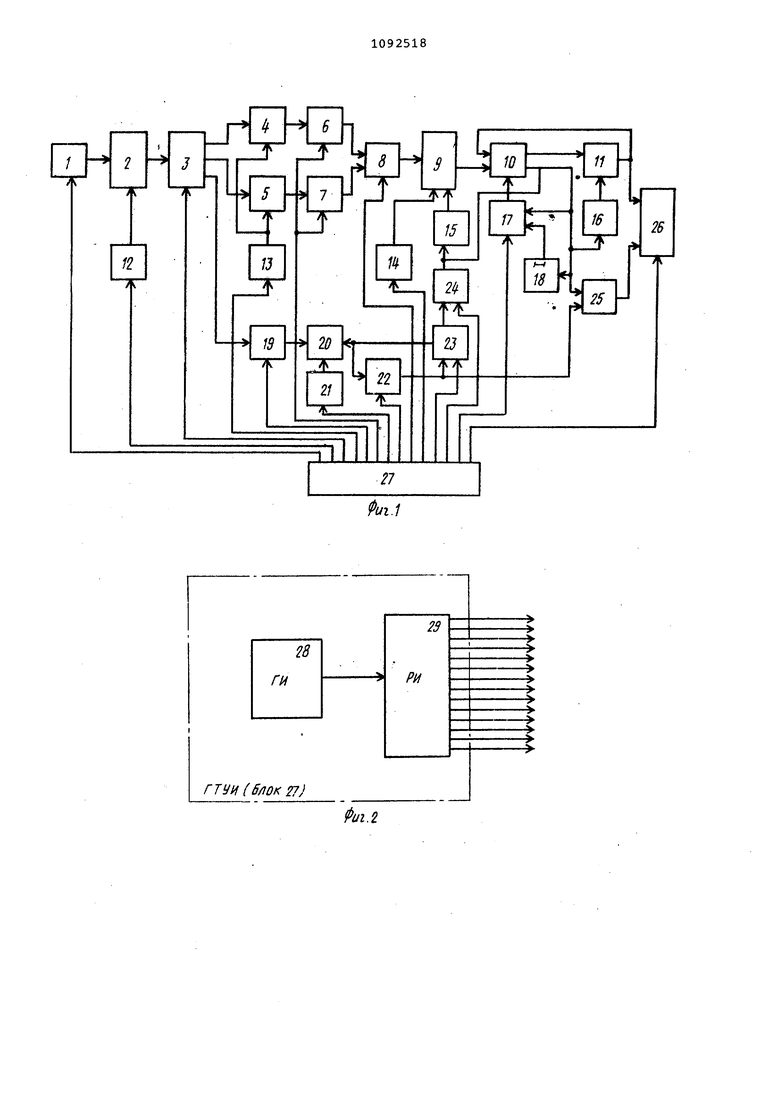

2. Спектроанализатор по п. 1, отличающийся тем, что блок выбора максимального числа с держит узел сравнения, элемент И и регистр, информационный выход которого является выходом блока выбора максимального числа и соединен с первым входом узла сравнения, выход которого подключен к первому входу элемента И, выход которого соединен с управляющим входом регистра, информационный вход которого объединен со вторым входом узла сравнения и является входом блока выбора максимального числа, второй вход элемента И является тактовым входом блока выбора максимального числа.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления коэффициентов дискретного преобразования Хаара | 1982 |

|

SU1061151A1 |

| ПРОЦЕССОР С МАКСИМАЛЬНО ВОЗМОЖНОЙ ПРОИЗВОДИТЕЛЬНОСТЬЮ ДЛЯ БЫСТРОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 2005 |

|

RU2290687C1 |

| Устройство для деления в системе остаточных классов | 1983 |

|

SU1141400A1 |

| Модулярное устройство вычисления систем линейных алгебраических уравнений | 2015 |

|

RU2611963C1 |

| Вычислительная система "Антикон" для предотвращения столкновения судов | 1983 |

|

SU1136178A1 |

| УСТРОЙСТВО ПЛАНИРОВАНИЯ ТОПОЛОГИИ ЛОГИЧЕСКИХ ИНТЕГРАЛЬНЫХ СХЕМ | 2012 |

|

RU2530275C2 |

| Цифровой измеритель несимметричности сигналов | 1990 |

|

SU1725179A1 |

| Устройство для решения системы линейных уравнений | 1987 |

|

SU1411776A1 |

| Генератор случайного процесса | 1988 |

|

SU1656527A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1988 |

|

SU1640709A1 |

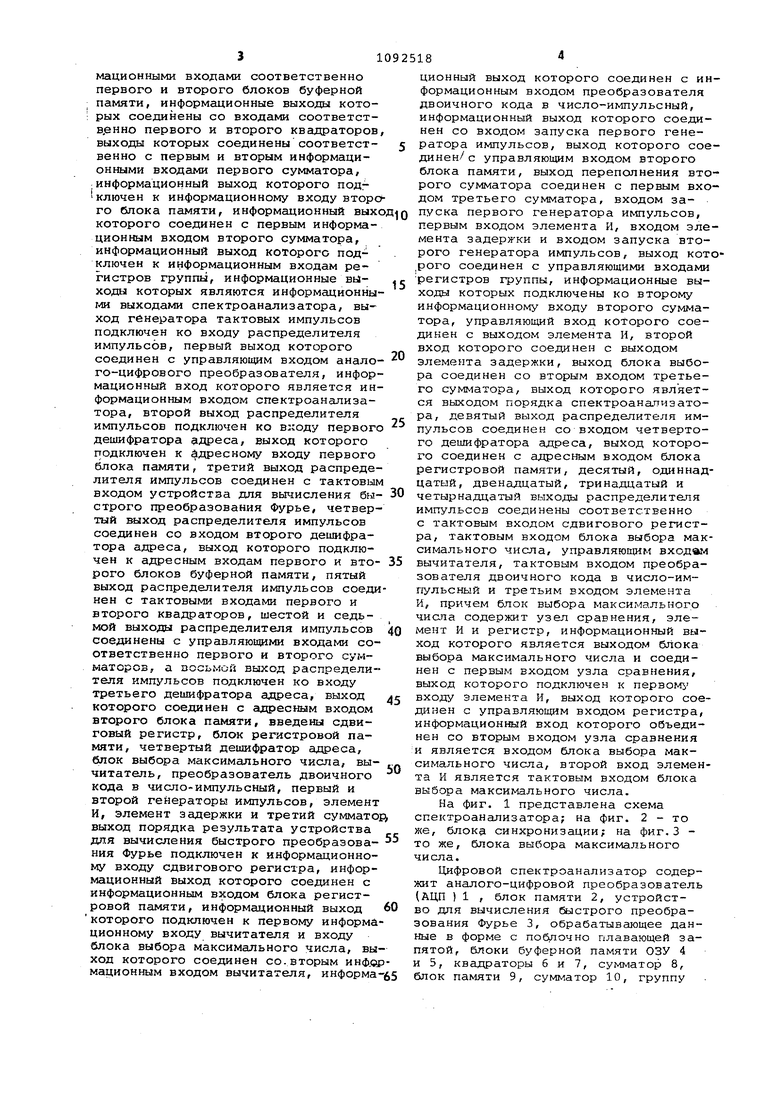

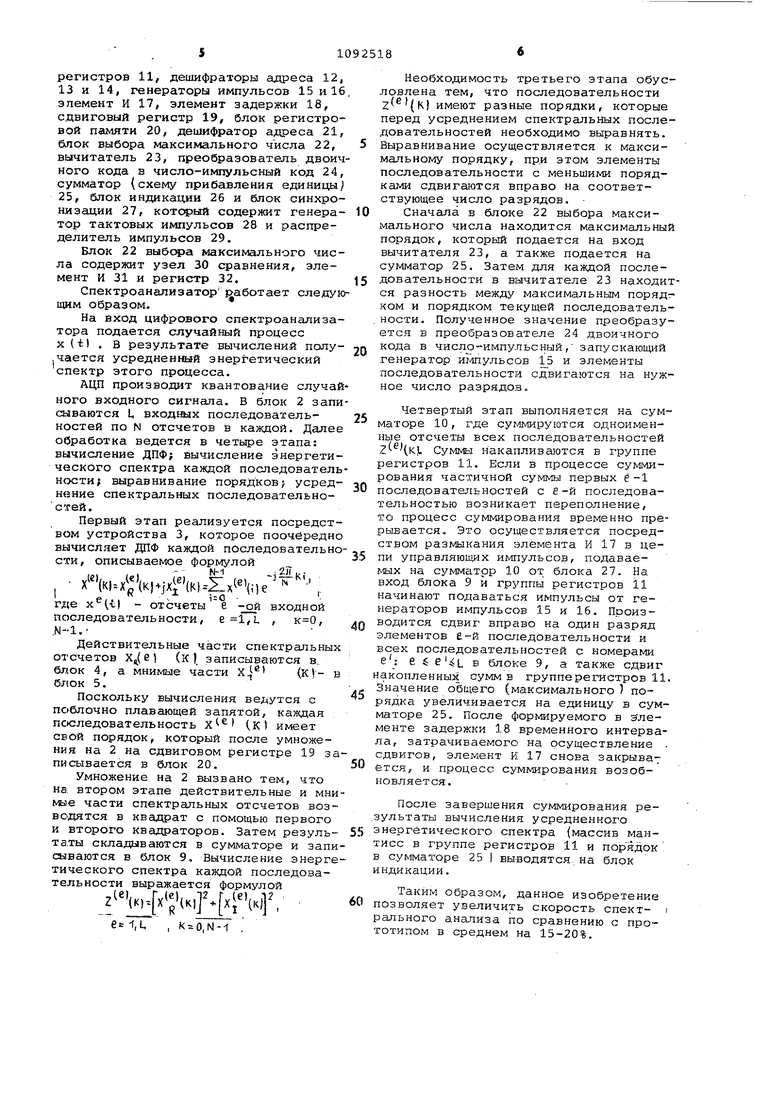

Изобретение относится к области радио- и вычислительной техники, а более конкретно к цифровым устройствам, предназначенным для выполнения спектрального анализа случайных электрических сигналов (цифрового спектрального анализа ). Известен спектроанализатор, в котором используются вычислительные блоки, основанные на арифметике плавагацей запятой tl3. Недостаток этого процессора низкое быстродействие. Наиболее близким по технической сущности к изобретению является цифровой Спектроанализатор, содержащий аналого-цифровой преобразователь, два блока памяти, два блока буферной памяти, три блока формирования адреса, устройство для вычисления быстро го преобразования Фурье, два квадратора и два сумматора, а также генератор тактовых импульсов и распределитель импульсов t21. Недостатком данного устройства является большое время, требуемое дл для получения усредненного по времени энергетического спектра. Это вызвано тем, что БПФ, cyмIvшpoвaниe квадратов и усреднение выполняется при представлении чисел в форме плавающей запятой. При такой форме представления операндов в процессе выполнения каждой арифметической операций приходится обрабатывать не только мантиссы, но и порядки чисел (например, при сложении необходимо выравнивать порядки операндов сдвигом вправо мантиссы числс1 с меньшим порядком). Кроме того, необходимо нормализовать результаты каждой арифметической операции, что также требует больtifflx затрат времени. Цель изобретения - повышение быстродействия. Поставленная цель достигается тем, что в цифровой Спектроанализатор, содержащий аналого-цифровой преобразователь, выход которого подключен к информационному входу первого блокапамяти, информационный выход которого подключен к информационному входу устройства для вычисления быстрого преобразования Фурье, выходы реальной и мнимой части результата которого соединены с информационными входами соответственно первого и второго блоков буферной памяти, информационные выходы которых соединены со входами соответств.енно первого и второго квадраторов выходы которых соединены соответственно с первым и вторым информационными входами первого сумматора, информационный выход которого подг включен к информационному входу второ го блока памяти, информационный вых которого соединен с первым информационным входом второго сумматора, информационный выход которого подключен к информационным входам регистров группы, информационные выходы которых являются информационны 1ИИ выходами спектроангьлизатора, выход генератора тактовых импульсов подключен ко входу распределителя импульсов, первый выход которого соединен с управляющим входом анало го-цифрового преобразователя, инфор мационный вход которого является ин формационным входом спектроанализатора, второй выход распределителя импульсов подключен ко входу первог дешифратора адреса, выход которого подключен к Адресному входу первого блока памяти, третий выход распреде лителя импульсов соединен с тактовы входом устройства для вычисления бы строго преобразования Фурье, четвер тый выход распределителя импульсов соединен со входом второго дешифратора адреса, выход которого подключен к адресным входам первого и вто рого блоков буферной памяти, пятый выход распределителя импульсов соеди нен с тактовыми входами первого и второго квадраторов, шестой и седьмой выходы распределителя импульсов соединены с управляющими входами со ответственно первого и второго сумматсроз, а восьмой выход распределителя импульсов подключен ко входу третьего дешифратора адреса, выход которого соединен с адресным входом второго блока памяти, введены сдвиговый регистр, блок регистровой памяти, четвертый дешифратор адреса, блок выбора максимального числа, вычитатель, преобразователь двоичного кода в число-импульсный, первый и второй генераторы импульсов, элемент И, элемент задержки и третий суммато выход порядка результата устройства для вычисления быстрого преобразования Фурье подключен к информационному входу сдвигового регистра, информационный выход которого соединен с информационным входом блока регистровой памяти, информационный выход которого подключен к первому информа ционному входу вычитателя и входу блока выбора максимального числа, вы ход которого соединен со.вторым инфо мационным входом вычитателя, информа ционный выход которого соединен с информационным входом преобразователя двоичного кода в число-импульсный, информационный выход которого соединен со входом запуска первого генератора импульсов, выход которого соединен/ с управляющим входом второго блока памяти, выход переполнения второго сумматора соединен с первым входом третьего сумматора, входом запуска первого генератора импульсов, первым входом элемента И, входом элемента задержки и входом запуска второго генератора И1 тульсов, выход кото,рого соединен с управляющими входами регистров группы, информационные выходы которых подключены ко второму информационному входу второго сумматора, управляющий вход которого соединен с выходом элемента Н, второй вход которого соединен с выходом элемента задержки, выход блока выбора соединен со вторым входом третьего сумматора, выход которого является выходом порядка спектроаналиэатора, девятый выход распределителя импульсов соединен со входом четвертого дешифратора адреса, выход которого соединен с адресным входом блока регистровой памяти, десятый, одиннадцатый, двенадцатый, тринадцатый и четырнадцатый выходы распределителя импульсов соединены соответственно с тактовым входом сдвигового регистра, тактовым входом блока выбора максимального числа, управляющим входам вычитателя, тактовым входом преобразователя двоичного кода в число-импульсный и третьим входом элемента И, причем блок выбора максимального чис-ла содержит узел сравнения, элемент И и регистр, информационный выход которого является выходом блока выбора максимального числа и соединен с первым входом узла сравнения, выход которого подключен к nepBOMi входу элемента И, выход которого соединен с управляющим входом регистра, информационный вход которого объединен со вторым входом узла сравнения и является входом блока выбора максимального числа, второй вход элемента И является тактовым входом блока выбора максимального числа. На фиг. 1 представлена схема спектроанализатора; на фиг. 2 - то же, блока синхронизации; на фиг.3 то же, блока выбора максимального числа. Цифровой спектроанализатор содержит аналого-цифровой преобразователь (АЦП ) 1 , блок памяти 2, устройство для вычисления быстрого преобразования Фурье 3, обрабатывающее данные в форме с поблочно плавающей запятой, блоки буферной памяти ОЗУ 4 и 5, квадраторы 6 и 7, сумматор 8, блок памяти 9, сумматор 10, группу регистров 11, дешифраторы адреса 12, 13 и 14, генераторы импульсов 15 и 16 элемент И 17, элемент задержки 18, сдвиговый регистр 19, блок регистровой памяти 20, дешифратор адреса 21, блок выбора максимального числа 22, вычитатель 23, преобразователь двоич ного кода в число-импульсный код 24, сумматор (схему прибавления единицы; 25, блок индикации 26 и блок синхронизации 27, который содержит генератор тактовых импульсов 28 и распределитель импульсов 29. Блок 22 выбега максимального числа содержит узел 30 сравнения, элемент И 31 и регистр 32. Спектроанализатор работает следую щим образом. На вход цифрового спектроанализатора подается случайный процесс x(t) . В результате вычислений получается усредненный энергетический спектр этого процесса. АЦП производит квантование случай ного входного сигнала. В блок 2 запи сываются L, входных последовательностей по N отсчетов в каждой. Далее обработка ведется в четыре этапа: вычисление ДПФ; вычисление энергетического спектра каждой последователь ности; выравнивание порядков усреднение спектральных последовательностей. Первый этап реализуется посредством устройства 3, которое поочередно вычисляет ДПФ каждой последовательно сти, описываемое формулой N-1 ; 2Л ,,,. I ().jxf( . где x(-l) - отсчеты е -ой входной последовательности, ,1 , , .N-1.Действительные части спектральных отсчетов Хц(е1 (к ) записываются в.. блок 4, а мнимые части (К)- в блок 5. Поскольку вычисления ведутся с поблочно плавающей запятой, каждая последовательность (К) имеет СБОЙ порядок, который после умножения на 2 на сдвиговом регистре 19 за писывается в блок 20. Умножение на 2 вызвано тем, что нa втором этапе действительные и мни мые части спектральных отсчетов возводятся в квадрат с помощью первого и второго квадраторов. Затем результа.ты складываются в сумматоре и запи сиваются в блок 9, Вычисление энерге тического спектра каждой последовательности выражается формулой (K,-{x;HK,f. 2 . ,М-1 Необходимость третьего этапа обусловлена тем, что последовательности (Kl имеют разные порядки, которые перед усреднением спектральных последовательностей необходимо выравнять. Выравнивание осуществляется к максимальному порядку, при этом элементы последовательности с меньщими порядками сдвигаются вправо на соответствующее число разр5эдов. Сначала в блоке 22 выбора максимального числа находится максимальный порядок, который подается на вход вычитателя 23, а также подается на сумматор 25. Затем для каждой последовательности в вычитателе 23 находится разность между максимальным порядтком и порядком текущей последовательности. Полученное значение преобразуется в преобразователе 24 двоичного кода в число импульсный, запускающий генератор импульсов 15 и элементы последовательности сдвигаются на нужное число разрядов. Четвертый этап выполняется на сумматоре 10, где сугФшруются одноименные отсчеты всех последовательностей 2(К.. Суммы накапливаются в группе регистров 11. Если в процессе суммирования частичной суммы первых €-1 последовательностей с е-и последовательностью возникает переполнение, то процесс суммирования временно прерывается. Это осуществляется посредством размыкания элемента И 17 в цепи управляющих иг/тульсов, подаваемых на сумматор 10 от блока 27. На вход блока 9 и группы регистров il начинают подаваться импульсы от генераторов импульсов 15 и 16. Производится сдвиг вправо на один разряд элементов -й последовательности и всех последовательностей с номерами е i eUl в блоке 9, а также сдвиг накопленных сумм в группе регистров 11. Значение общего (максимального 5 порядка увеличивается на единицу в сумматоре 25. После формируемого в элементе задержки 18 временного интервала, затрачиваемого на осуществление . сдвигов, элемент И 17 снова закрыва7 ется, и процесс суммирования возобновляется. После завершения суммирования результатьз вычисления усредненного энергетического спектра (массив мантисс в группе регистров 11 и порядок в сумматоре 25 | выводятся, на блок индикации. Таким образом, данное изобретение позволяет увеличить скорость спект- i рального анализа по сравнению с прототипом в среднем на 15-20%.

Dm Шт 27 Фиг. 2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цветков Э.И.Нестационарные случайные процессы и их анализ | |||

| М., Энергия, 1973 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Мизин И.А., Матвеев А.А | |||

| Цифровые фильтры, М., Связь, 1979, с | |||

| Питательный кран для вагонных резервуаров воздушных тормозов | 1921 |

|

SU189A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1984-05-15—Публикация

1982-10-01—Подача