I

Изобретение относится к вычислительной технике и может быть использовано для формирования прямоу1 ольных импульсов в устройствах автоматики и телемеханики.

Известен формирователь импульсов, содержащий п -потенциальных инверторов, соединенных между собой последовательно, параллельно одному из которых подключен времязадающий конденсатор, два логических элемента И-НЕ транзисторнотранзисторной логики, каждый из которых содержит два выхода, эмиттерный и коллекторный, и один вход, причем, логические элементы И-НЕ соединены таким образом, что представляют собой четырехвходовый логический элемент неравнозначности ClD.

Недостаток этого устройства - разброс неравенство длительности импульсов, формируемых по переднему и заднему фронту входных импульсов вследствие различия постоянных времени заряда и разряда конденсатора, подключенного параллельйо одному из потенциальных инверторов.

Наиболее близким техническим реше- 51ием,к данному изобретению является формирователь импульсов, содержащий элемент равнозначности и два триггера, выход второго триггера соединен с одним из входов элемента равнозначности

t2J.

Недостаток известного формирователя невозможность получения стабильных по длительности импульсов, сформированных по переднему и заднему фронту ,входного импульсй.

Цель изобретения - повышение ста5биЛьности длительности формируемых импульсов.

Поставленная цель достигается тем, что в формирователь импульсов, содержащий элемент неравнозначности и триггер,

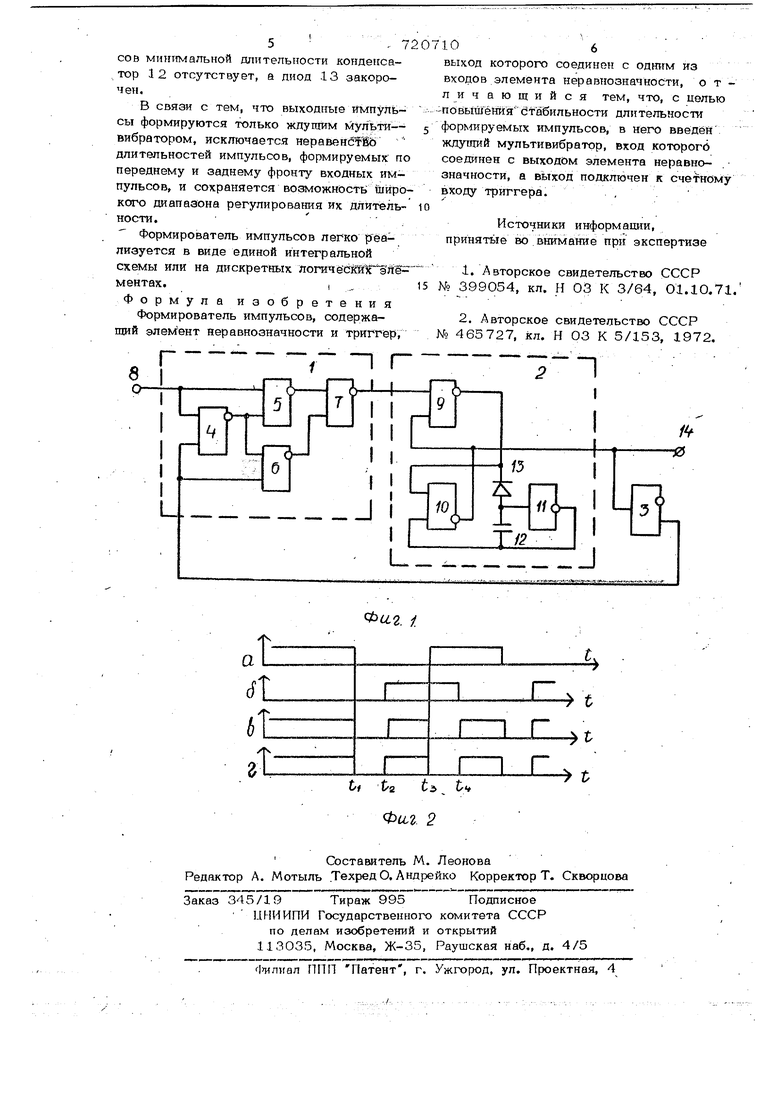

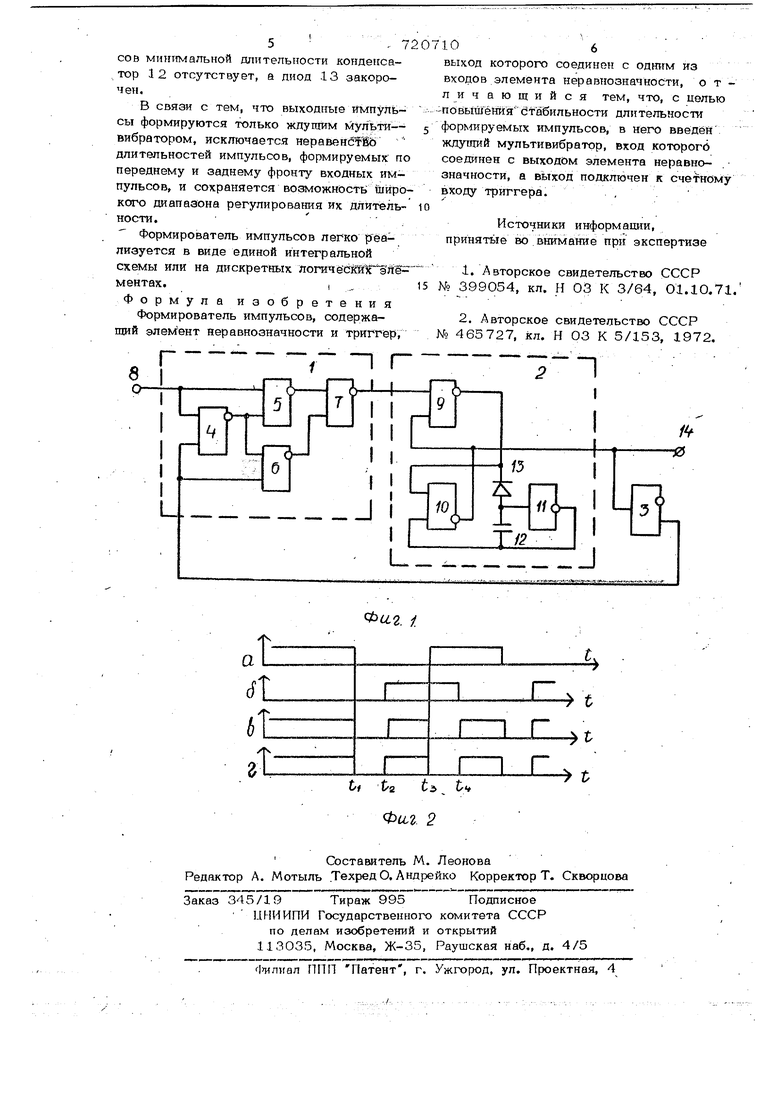

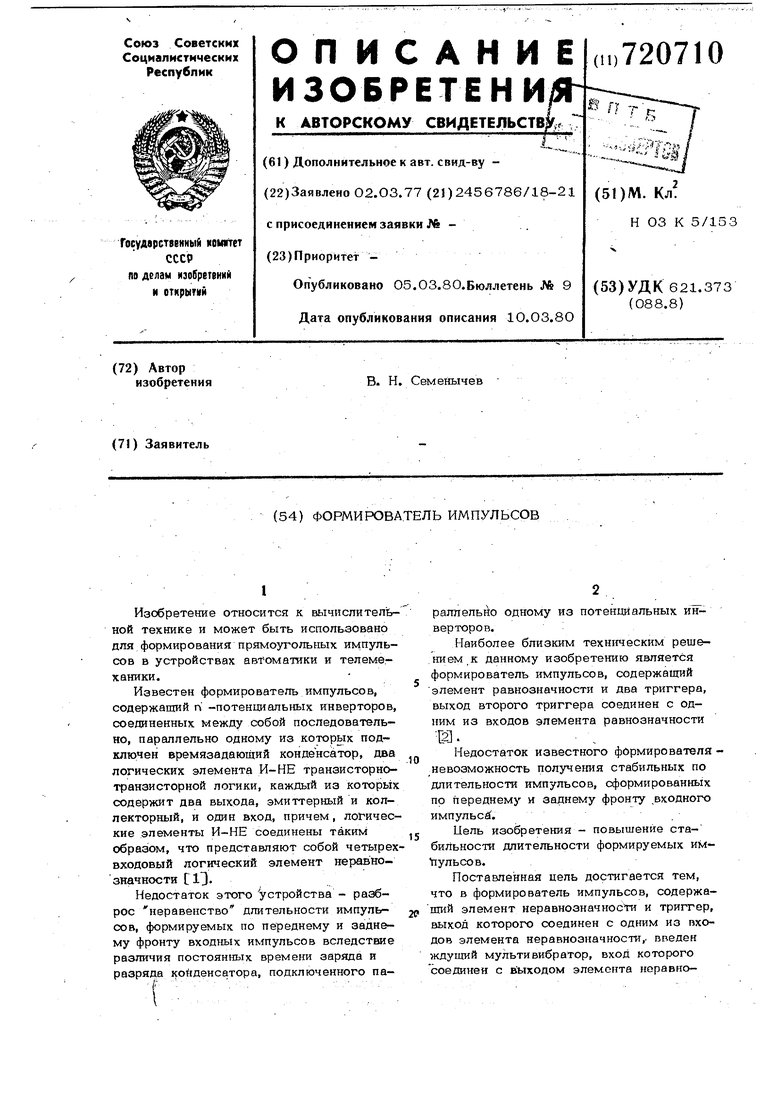

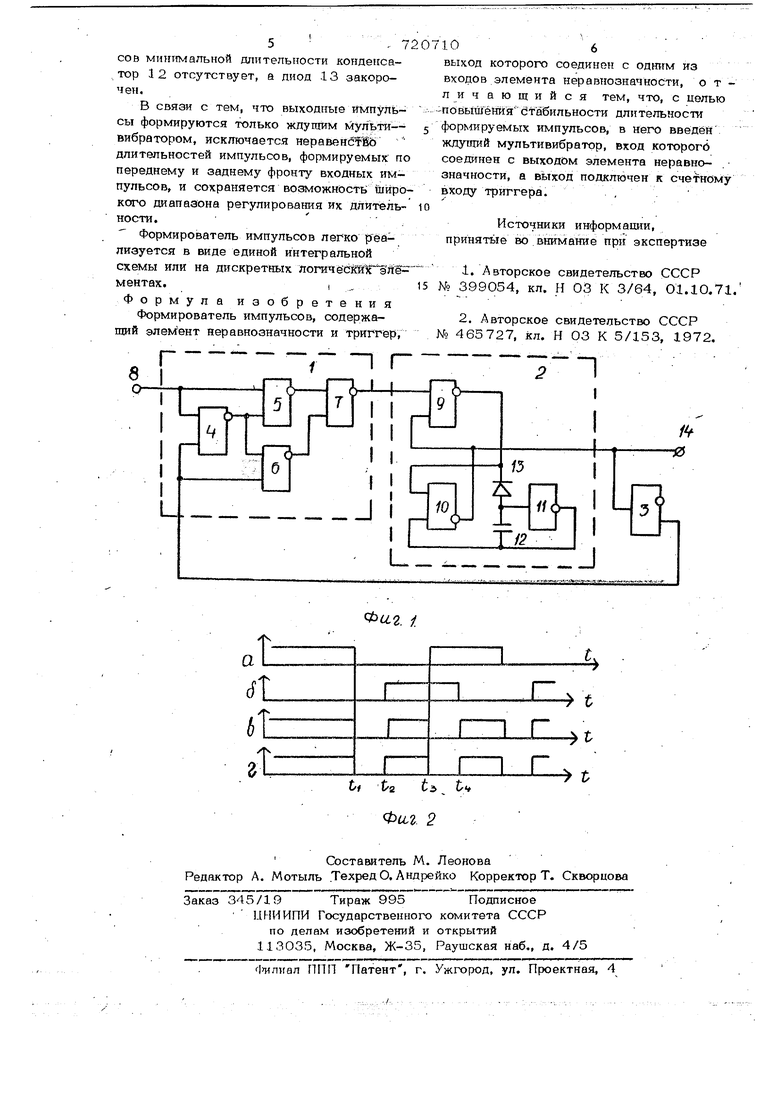

f выход которого соединен с одним из входов элемента неравнозначности,, введен ждущий мультивибратор, вход которого соединен с Выходом элемента неравнозначности, а выход подключен к счётномвхоДу триггера. На фиг. 1 предстаншена схема формироватепя импульсов; на фиг. 2 - диаграммынапряжений в различных точках схемы. Формирователь импульсов содержит элемент неравнозначности 1, ждущий мультивибратор 2, триггер 3 со счетным входом. Первый вход элемента неравнозначности 1, выполненного на потенциаль ных Логических элементах И-НЕ 4-7, соединен со входным зажимом 8. Выход элемента неравнозначности 1, т. е. выходйогическргр элемента И-Г1Е 7, соед;инен со входом ждущего мультивибратора 2, вьтполненнрго на потенциальных лоТическйх элементах Й-НЕ 9-11, конденсаторе 12, диоде 13. Счетный вход триггер а 3 соединен с выходом ждущего мультивибратора 2, т. е. с выходом логического элемента И-НЕ 1О, и с выход ным зажимом 14 формирователя импульсов. Прямой выход триггера 3 соединен со Bfbpbiivi входом элемента неравнозначности 1. Формирователь импульсов работает следующим образом. В исходном состоянии после подачи напряжения питания, если на первый вход элемента неравнозначности 1 со входного заткима 8 поступает высокий уровень логической 1 (фиг. 2а), а с прямого выхода триггера 3 на второй вход элеме та неравнозначности 1 поступает низкий уровень логического О (фиг. 26), то на вь1хрде логическрго элемента И-НВ 7 устанрвится высокий уровень логической I, (фиг. 2в - интервал времен 1 -1, ) На выходе ждущего мультивибратора 2, т. е. на выходе логического элемента H-}iE 16, при этом установится уррвень логической 1 (фиг. 2 г), на выхРде логического элемента И-НЕ 9 - уровень лргического О. Указанное состояние Moxcet поддерживаться на протяжении длительного времени, и все элементы пр йтрм Сохраняют свОе состояние. При изменении входного сигнала от высокого уровня к низкому на выходе элемента неравнозначности 1 УСТанавЛи- вается уровень логического О (фиг. 2в момент времеш1 t. ). Появлент5е логического О на выходе элемёнта неравнозн чностй 1 приводит к запуску ждущего мультивибратора 2, на выходе ко т6рогЬ7т.е. на йыходТ логического элемента И-НЕ Ю, форШруется мпульс логического О заданной длиельности (фиг. 2г, интервал времени -)В момент изменения выходного сигна- а ждущего мультивибратора 2 (фиг. 2г, омент времени t ) опрокидывается риггер 3, на прямом выходе которого ри этом-устанавливается логическ.ая 1 (фиг. 26, момент времени t ). Этим заканчивается формирование выходного импульса по переднему фронту входного импульса низкого уровня и ус тановка формирователя импульсов для формирования выходного импульса по заднему фронту входного импульса, при этом на выходе элемента неравнозначности 1 устанавливается уровень логической 1 и заверщаются переходные процессы в ждущем мультивибраторе 2. Уровень логической 1 на выходе логического элемента неравнозначности 1 сохраняется до момента Изменения входного сигнала до высокого уровня логической (фиг. 2а, момент времени t ). При изменении уровня входного сигнала с низкого на высокий на выходе лргического элемента неравнозначности 1 устанавливается уровень логического О (фиг. 2в, момент времени I- ), которым внрвь запускается ждущий мультивибратор 2, на выходе которого формируется импульс логического О заданной длительности (фиг. 2г - интервал времени Ч-tJЗадним фронтом импульса низкого уровня с выхода ждущего мультивибратора 2 вновь опрокидывается триггер 3, на прямом выходе которого устанавливается уровень логического О (фиг. 26, момент времени t ), а формирователь импульсов устанавливается в исходное состояние для формирования выходного импульса по переднему фронту входного импульса. Если при включении напряжения питани на прямрм выходе триггера 3 установится уровень логической 1, то формирование выходных импульсов начинает ся с заднего фронта входных импульсов. Таким образом, по переднему и заднему фронту входных импульсов на выходе формирователя импульсов, на .выходном зажиме 14, формируются импульсы лргического О, а на выходе логическо- го элемента 9 И-РШ - импульсы лотческой . Длительность выходных импульсрв можно изменить с помоптю конденсатора 12. В сттучае получения iiMiiy;ib5. 7 СОЙ минтгмальной длительности кондексатор 12 отсутствует, а диод 13 закорочен, В связи с тем, что выходные ймпу-л{зсы формируются только ждущим вибратором, исключается неравенб Шй длительностей импульсов, формируемых по переднему и заднему фронту входных импульсов, и сохраняется возможность широ кого диагтазона регулирования их длительности.. Формирователь импульсов легко реализуется в виде единой интегральной схемы или на дискретных логичёСЖх л1е ментах.i . Формула изобретения Формирователь импульсов, содержащий элемент неравнозначности и триггер. ,10б выход которого соединен с одним из входов элемента неравнозначности, о т личающийся тем, что, с целью повышенияСтабильности длительности формируемых импульсов, в него введен ждугдий мультивибратор, вход которогб соединен с выходом элемента неравнозначности, а выход подключен к счетному входу триггера., Источники информашга, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 399054, кл. И 03 К 3/64, 01.10.71. 2.Авторское свидетельство СССР 465727, кл. Н 03 К 5/153, 1972,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство задержки | 1978 |

|

SU790214A1 |

| Умножитель частоты следования импульсов | 1977 |

|

SU750714A1 |

| Умножитель частоты следования импульсов | 1977 |

|

SU705661A1 |

| Мультивибратор | 1978 |

|

SU738106A1 |

| Селектор импульсов по частоте следования | 1977 |

|

SU655072A1 |

| Селектор импульсов по частоте следования | 1986 |

|

SU1378035A1 |

| Умножитель частоты | 1977 |

|

SU621075A1 |

| Фазовый дискриминатор | 1985 |

|

SU1285559A1 |

| Многофазный мультивибратор | 1979 |

|

SU788350A1 |

| Измеритель времени установления выходного напряжения цифроаналоговых преобразователей | 1984 |

|

SU1236612A1 |

.г. i

Авторы

Даты

1980-03-05—Публикация

1977-03-02—Подача