(54) УСТРОЙСТВО ЗАДЕРЖКИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Селектор импульсов по частоте следования | 1977 |

|

SU655072A1 |

| Умножитель частоты следования импульсов | 1977 |

|

SU705661A1 |

| Устройство для выделения одиночного импульса | 1978 |

|

SU744935A1 |

| Формирователь импульсов | 1977 |

|

SU720710A1 |

| Умножитель частоты следования импульсов | 1977 |

|

SU750714A1 |

| Селектор импульсов по длительности | 1979 |

|

SU849475A1 |

| Фазовый дискриминатор | 1985 |

|

SU1285559A1 |

| Устройство задержки прямоугольных импульсов | 1986 |

|

SU1385278A1 |

| Устройство для задержки импульсов | 1988 |

|

SU1575296A1 |

| Одновибратор | 1978 |

|

SU790123A1 |

1

Изобретение относится к импульс- , ной технике и может быть испоЛьзовано при построении систем автоматики и вычислительной техники.

Известно устройство задержки прямоугольных импульсов с регулируемым временем задержки, содержащее входной и выходной ключевые элементы и времязадающую цепь 1.

Это устройство обладает низкой точностью воспроизведения задержанного импульса из-за влияния остаточного заряда на конденсаторе времязадающей цепи и разницы в постоянных времени заряда и разряда конденсатора времязадающей цепи.

Известно устройство задержки, содержащее входной элемент задержки и формирователь выходных импульсов, выполненный на основе триггера, охваченного цепью обратной связи через элемент задержки. В зтом устройстве схема совпсщения соединена выходом со входом элемента задержки цепи обратной связи, а входами - с выходом триггера и выходом входного элемента задержки соответственно. Входной элемент задержки и элемент . задержки цепи обратной связи пред.ставляет собой элементы задержки переднего фронта входного импульса 2.

В известном устройстве задержка переднего фронта выходного импульса

5 формируется входным элементом задержки, задержка заднего фронта элементом задержки цепи обратной связи, вследствие чего это устройство обладает значительной цогреш10 ностью в восстановлении длительности задержанного импульса до длительности входного импульса. Кроме того, известное устройство не обладает способностью самокоррекции при вклюt5 чении источника питания. Так, если при уровне логического О на входе триггер при включении напряжения питания установится в единичное состояние, то это состояние сохраняется

20 до начала второго входного импульса. Таким образом, первый входной импульс не проходит на выход устройства. Известное устройство не позволяет также получать импульсы удвоенной

25 (частоты.

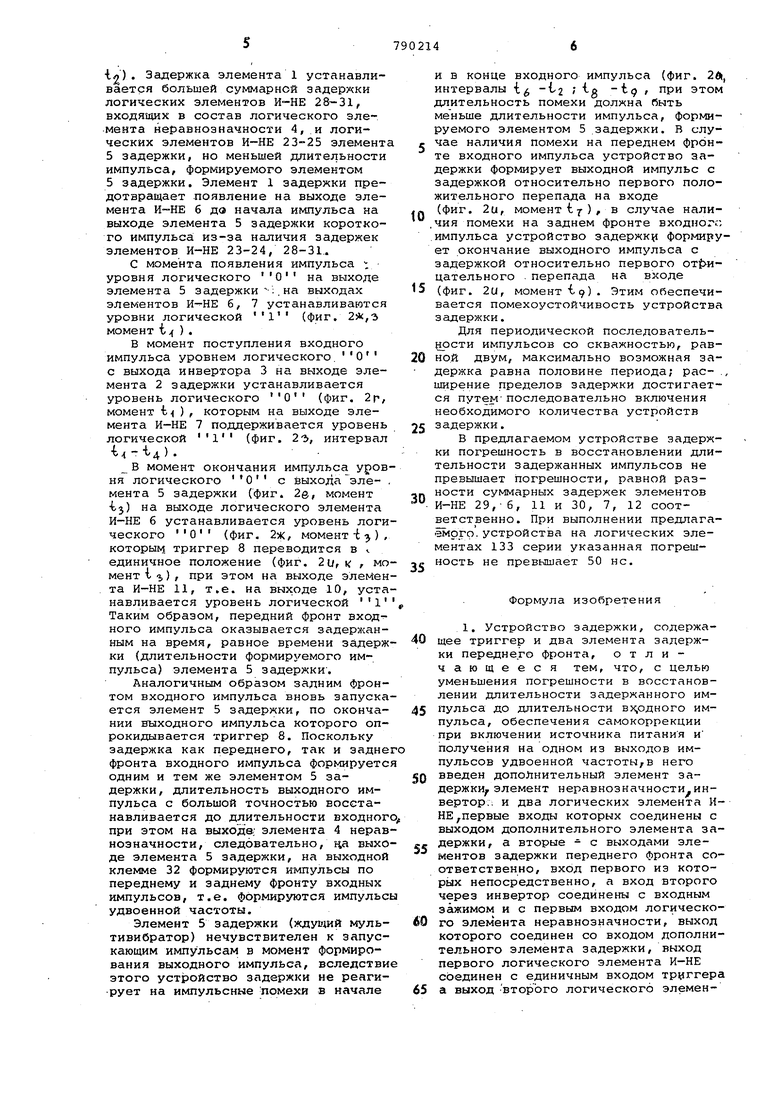

Цель изобретения - уменьшение погрешности в восстановлении длитель.ности задержанного импульса до дли30 тельности входного импульса, обеспечение самокоррекции при включении источника питания и получение на однс}м из выходов импульсов удвоенно . Указанная,- цель достигается тем, что в устройство задержки, содержащее триггер и два элемента задержки переднего фронта, введен дополнител ный элемент задержки, элемент нерав нозначности, инвертор и два логичес ких элемента И-НЕ, первые входы которых соединены с выходом дополнительного элемента задержки, а вторые - с выходами элементов задержки -переднего фронта соответственно, вх первого из которых непосредственно, а вход второго через инвертор соеди нены с входным зажимом и с первым входом логического элемента неравно значности, выход которого соединен со входом дополнительного элемента задержки, выход первого логического элемента И-НЕ соединен с единичным входом триггера, а выход второго логического элемента И-НЕ - с нулевым входом триггера, нулеЪой выход которого подключен ко второму входу логического элемента неравнозначности, На фиг, 1 изо6ра51 ена схема предлагаемого устройства; на фиг. 2 временная диаграмма, поясняющая принцип его действия. Устройство содержит элементы 1 и 2 задержки переднего фронта, инвертор 3, логический элемент 4 неравнозначности, элемент 5 задержки, логические элементы И-НЕ 6 и 7, .. триггер 8, входную клемму 9 и выход ную клемму 10 устройства. Вход элемента 1 задержки непосредственно, а вход элемента 2 задержки через инвертор 3 соединены со входной клеммой 9 устройства и с первым вхо дом логического элемента 4 неравнозначности, выход которого подключен ко входу элемента 5 задержки. Первые входы логических элементов И-НЕ 6, 7 соединены с выходом элемента 5 задержки. Второй вход логического элемента И-НЕ б соединен с выходом элемента 1 задержки, а, второй вход логического элемента И-НЕ 1-е выходом элемента 2 задержки. Выходы логических элементов И-НЕ б- и 7 сое динены с единичным и нулевым входом триггера 8 соответственно, нулевой выходкоторого подключен ко второму входу логического элемента 4 нерав.нозначности. TpjHrrep 8 . выполнен на логических элементах 11 и 12, элементы задержки переднего фронта - на логических элементах 13-18, конденсаторах 19 и 20, диодах 21-22, дополнительный элемент задержки - на логических элементах 23-25, диоде 26 конденса торе 27; элемент неравнозначности содержит логические элементы 2В 31.. Кроме того, устройство содержит выходную клемму 32. Устройство задерхки работает следующим образом. Если в момент включения напряжения источника питания (фиг. 2, момент ijj ) при уровне логического О на входе 9 триггер 8 устанавливается в единичное положение (на выходе элемента И-НЕ 11 - уровень логической , на выходе элемента И-НЕ 12 - уровень логического О), то на выходе логического элемента 4 неравнозначности устанавливается уровень логического О (фиг. 2), вследствие чего на выходе элемента 5 задержки, даже если конденсатор 27 предварительно заряжен, с течением времени вследствие его разряда устанавливается уровень логической Ч (фиг.-2 б , момент ig ) При уровне логического О входной клемме 9 на выходах логических элементов И-НЕ 13, 15 устанавли-вается уровень лог-оческой , вследствие чего на выходе элемента И-НЕ 14 также устанавливается вень логической (фиг. 25), так как с выхода инвертора 3 на входы элементов И-НЕ 16, 18 поступает сигнал уровня логической i (фиг. 25) и при этом элемент 2 задержки принимает исходное состойние, при котором на выходе элемента И-НЕ 17, устанавливается уровень логической . Вследствие того, что на входах элемента И-НЕ 7 - , уровни логической , на его выходе устанавливается уровень логического (фиг. 2ъ), которым триггер 8 переводится в нулевое положение, при этом на выходе элемента И-НЕ 11 устанавливается уровень логического О (фиг. 2 у, момент-ig), т.е. устройство задержки самокорректируется и принимает исходное состояние после включения напряжения источника питания. Прямоугольный импульс уровня логической 1 (фиг. 2а, момент t), поступающий на входную клемму 9, вызывает появление на выходе логического элемента 4 неравнозначности уровня логического О (фиг. 2tJ, момент i,j ) , которым запускается элемент 5 задержки, представляющий собой ждущий мультивибратор, выполненный на логических элементах И-НЕ 23-25, диоде 26 и конденсаторе 27. На выходе логического элемента 5 задержки формируется импульс уровня логического установленной длительности (фиг. 26, интервал i/ ij). Входной импульс (фиг. 2а, момент i. ) запускает также элемент 1 задержки, который задерживает передний фронт входного импульса уровня логического О (фиг. 2Ь, момент

ig). Задержка элемента 1 устанавливается большей суммарной задержки логических элементов И-НЕ 28-31, входящих в состав логического элемента неравнозначности 4, и логических элементов И-НЕ 23-25 элемента 5 задержки, но меньшей длительности импульса, формируемого элементом 5 задержки. Элемент 1 задержки предотвращает .появление на выходе элемента И-НЕ 6 до начала импульса на выходе элемента 5 задержки короткого импульса из-за наличия задержек элементов И-НЕ 23-24, 28-31..

С момента появления импульса -, уровня логического О на выходе элемента 5 задержки:,на выходах элементов И-НЕ 6, 7 устанавливаются уровни логической (фиг. 2,3 момент t ) .

В момент поступления входного импульса уровнем логического.О с выхода инвертора 3 на выходе элемента 2 задержки устанавливается уровень логического О (фиг. 2р, момент t ), которым на выходе элемента И-НЕ 7 поддерживается уровень логической Ч (фиг. 2-ь, интервал ).

В момент окончания импульса уровня логического О с выхода эле- . мента 5 задержки (фиг. 2е, момент ) на выходе логического элемента И-НЕ б устанавливается уровень логического (фиг. 2ж, момент i 3 ) которым триггер 8 переводится в v единичное положение (фиг. 2Ur к , момент i г) при этом на выходе элемента И-НЕ 11, т.е. на выходе 10, устанавливается уровень логической Таким образом, передний фронт входного импульса оказывается задержанным на время, равное времени задержки (длительности формируемого импульса) элемента 5 задержки .

Аналогичным образом задним фронтом входного импульса вновь запускается элемент 5 задержки, по окончаНИИ выходного импульса которого опрокидывается триггер 8. Поскольку задержка как переднего, так и заднег фронта входного импульса формируется одним и тем же элементом 5 задержки, длительность выходного импульса с большой точностью восстанавливается до длительности входного при этом на выхода элемента 4 неравнозначности, следовательно, ц,а выходе элемента 5 задержки, на выходной клемме 32 формируются импульсы по переднему и заднему фронту входных импульсов, т.е. формируются импульсы удвоенной частоты.

Элемент 5 задержки (ждусяий мультивибратор) нечувствителен к запускающим импульсам в момент формирования выходного импульса, вследствие этого устройство задержки не реагирует на импульсные помехи в начале

и в конце входного импульса (фиг. 2А интервалы i ;ig -tp, при этом длительность помехи должна быть меньше длительности импульса, формируемого элементом 5 задержки. В случае наличия помехи на переднем фронте входного импульса устройство задержки формирует выходной импульс с задержкой относительно первого положительного перепада на входе (фиг. 2и, момент {у), в случае наличия помехи на заднем фронте входного импульса устройство зaдepжк формирует окончание выходного импульса с задержкой относительно первого от ицательного .перепада на входе (фиг. 2ц, момент 9 Этим обеспечивается помехоустойчивость устройства задержки.

Для периодической последовательности импульсов со скважностью, равной двум, максимально возможная задержка равна половине периода; расширение пределов задержки достигается путемпоследовательно включения необходимого количества устройств задержки.

В предлагаемом устройстве задержки погрешность в восстановлении длительности задержанных импульсов не превышает погрешности, равной разности суммарных задержек элементов И-НЕ 29,-6, 11 и 30, 7, 12 соответственно. При выполнении предлагаемого, устройства на логических элементах 133 серии указанная погрешность не превышает 50 не.

Формула изобретения

Авторы

Даты

1980-12-23—Публикация

1978-10-26—Подача