15

20

Изобретение относится к импульсной технике и может быть использовано для измерения фазовых сдвигов импульсных сигналов, в системах им- пульсно-фазовой автоподстройки часто- 5 ты, в устройствах автоматики и телемеханики .

Цель изобретения - увеличение помехоустойчивости.

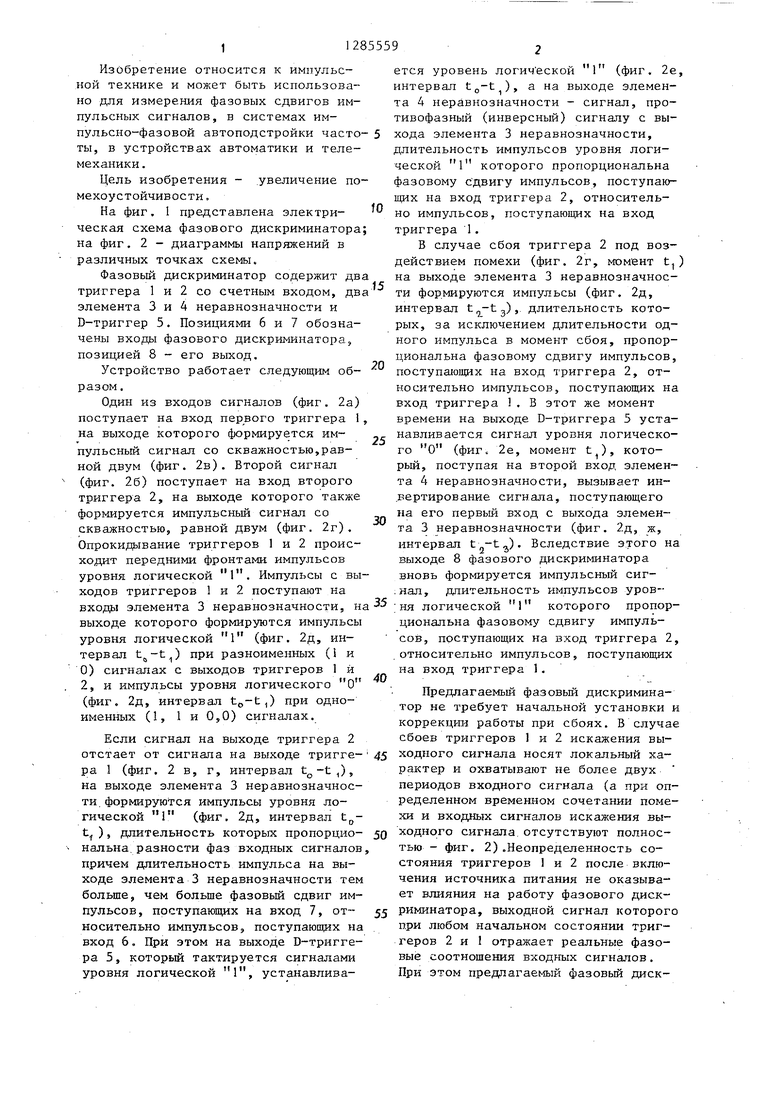

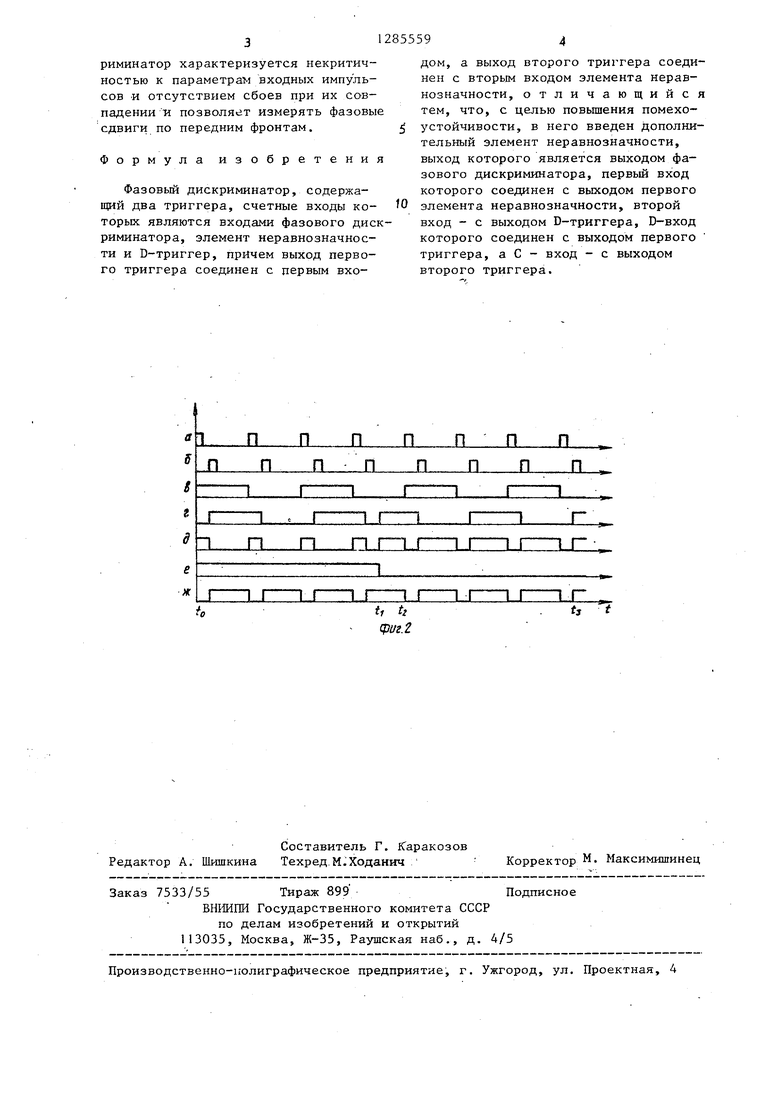

На фиг. 1 представлена электри- ческая схема фазового дискриминатора; на фиг. 2 - диаграммы напряжений в различных точках схемы.

Фазовый дискриминатор содержит два триггера 1 и 2 со счетным входом, два элемента 3 и 4 неравнозначности и D-триггер 5. Позициями 6 и 7 обозначены входы фазового дискриминатора, позидией 8 - его выход.

Устройство работает следующим образом .

Один из входов сигналов (фиг. 2а) поступает на вход первого триггера 1, на выходе которого формируется импульсный сигнал со скважностью,равной двум (фиг. 2в). Второй сигнал (фиг. 26) поступает на вход второго триггера 2, на выходе которого также формируется импульсный сигнал со скважностью, равной двум (фиг. 2г). Опрокидывание триггеров 1 и 2 происходит передними фронтами импульсов уровня логической 1. Импульсы с выходов триггеров 1 и 2 поступают на входы элемента 3 неравнозначности, на выходе которого формируются импульсы уровня логической 1 (фиг. 2д, интервал ) при разноименных (i и 0) сигналах с выходов триггеров 1 и 2, и импульсы уровня логического О (фиг. 2д, интервал ,) при одноименных (1, 1 и 0,0) сигналах.

Если сигнал на выходе триггера 2 отстает от сигнала на выходе тригге- ра 1 (фиг. 2 в, г, интервал ,), на выходе элемента 3 неравнозначности, формируются импульсы уровня логической 1 (фиг. 2д, интервал

ется уровень логич еской интервал tj,-t).

(фиг. 2е а на выходе элемен25

30

35

40

45

toта 4 неравнозначности - сигнал, противофазный (инверсный) сигналу с выхода элемента 3 неравнозначности, длительность импульсов уровня логической 1 которого пропорциональна фазовому с двигу импульсов, поступающих на вход триггера 2, относительно импульсов, поступающих на вход триггера 1.

В случае сбоя триггера 2 под воздействием помехи (фиг. 2г, момент t, на выходе элемента 3 неравнозначности формируются импульсы (фиг. 2д, интервал ),. длительность которых, за исключением длительности одного импульса в момент сбоя, пропорциональна фазовому сдвигу импульсов, поступающих на вход триггера 2, относительно импульсов, поступающих на вход триггера 1. В этот же момент времени на выходе D-триггера 5 устанавливается сигнал уровня логического О (фигс 2е, момент t), который, поступая на второй вход элемента 4 неравнозначности, вызывает инвертирование сигнала, поступающего на его первый вход с выхода элемента 3 неравнозначности (фиг. 2д, ж, интервал t -t ,). Вследствие этого на выходе 8 фазового дискриминатора вновь формируется импульсный сиг- ;нал, длительность импульсов уров ня логической 1 которого пропорциональна фазовому сдвигу импульсов, поступающих на вход триггера 2, относительно импульсов, поступающих на вход триггера 1.

Предлагаемьш фазовый дискриминатор не требует начальной установки и коррекции работы при сбоях. В случае сбоев триггеров 1 и 2 искажения выходного сигнала носят локальный характер и охватывают не более двух периодов входного сигнала (а при определенном временном сочетании помехи и входных сигналов искажения выt), длительность которых пропорцио- 50 зсодного сигнала отсутствуют полностью - фиг. 2).Неопределенность состояния триггеров 1 и 2 после включения источника питания не оказывает влияния на работу фазового диск- 55 риминатора, выходной сигнал которого при любом начальном состоянии триггеров 2 и 1 отражает реальные фазовые соотношения входных сигналов. При этом предлагаемый фазовый дискнальна. разности фаз входных сигналов, причем длительность импульса на выходе элемента 3 неравнозначности тем больше, чем больше фазовый сдвиг импульсов , поступающих на вход 7, относительно импульсов, поступающих на вход 6, При этом на выходе D-триггера 5 , который тактируется сигналами уровня логической 1, устанавлива

ется уровень логич еской интервал tj,-t).

(фиг. 2е, а на выходе элемен

та 4 неравнозначности - сигнал, противофазный (инверсный) сигналу с выхода элемента 3 неравнозначности, длительность импульсов уровня логической 1 которого пропорциональна фазовому с двигу импульсов, поступающих на вход триггера 2, относительно импульсов, поступающих на вход триггера 1.

В случае сбоя триггера 2 под воздействием помехи (фиг. 2г, момент t,) на выходе элемента 3 неравнозначности формируются импульсы (фиг. 2д, интервал ),. длительность которых, за исключением длительности одного импульса в момент сбоя, пропорциональна фазовому сдвигу импульсов, поступающих на вход триггера 2, относительно импульсов, поступающих на вход триггера 1. В этот же момент времени на выходе D-триггера 5 устанавливается сигнал уровня логического О (фигс 2е, момент t), который, поступая на второй вход элемента 4 неравнозначности, вызывает инвертирование сигнала, поступающего на его первый вход с выхода элемента 3 неравнозначности (фиг. 2д, ж, интервал t -t ,). Вследствие этого на выходе 8 фазового дискриминатора вновь формируется импульсный сиг- ;нал, длительность импульсов уров ня логической 1 которого пропорциональна фазовому сдвигу импульсов, поступающих на вход триггера 2, относительно импульсов, поступающих на вход триггера 1.

Предлагаемьш фазовый дискриминатор не требует начальной установки и коррекции работы при сбоях. В случае сбоев триггеров 1 и 2 искажения выходного сигнала носят локальный характер и охватывают не более двух периодов входного сигнала (а при определенном временном сочетании помехи и входных сигналов искажения вызсодного сигнала отсутствуют полностью - фиг. 2).Неопределенность состояния триггеров 1 и 2 после включения источника питания не оказывает влияния на работу фазового диск- риминатора, выходной сигнал которого при любом начальном состоянии триггеров 2 и 1 отражает реальные фазовые соотношения входных сигналов. При этом предлагаемый фазовый дискриминатор характеризуется некритичностью к параметрам входных импульсов и отсутствием сбоев при их совпадении и позволяет измерять фазовые сдвиги но передним фронтам.

Формула изобретения

Фазовый дискриминатор, содержащий два триггера, счетные входы которых являются входами фазового дискриминатора, элемент неравнозначности и D-триггер, причем выход первого триггера соединен с первым вхоСоставитель Г. Каракозов Редактор А. Шишкина Техред.М.Ходанич

Заказ 7533/55 Тираж 899Подписное

БНИИГШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

дом, а выход второго триггера соединен с вторым входом элемента неравнозначности, отличающийся тем, что, с целью повьппения помехоустойчивости, в него введен дополнительный элемент неравнозначности, выход которого является выходом фазового дискриминатора, первый вход которого соединен с выходом первого элемента неравнозначности, второй вход - с выходом D-триггера, D-вход которого соединен с выходом первого триггера, а С - вход - с выходом второго триггера.

Корректор - Максимишинец

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации импульсов | 1985 |

|

SU1322434A1 |

| Устройство для передачи сигнала с частотной манипуляцией | 1985 |

|

SU1256235A1 |

| Фазовый дискриминатор | 1975 |

|

SU534031A1 |

| Умножитель частоты следования импульсов | 1977 |

|

SU750714A1 |

| Частотный манипулятор | 1981 |

|

SU985966A1 |

| Преобразователь кода во временной интервал | 1987 |

|

SU1474848A1 |

| Устройство задержки | 1978 |

|

SU790214A1 |

| Формирователь импульсов | 1977 |

|

SU720710A1 |

| Частотный манипулятор | 1985 |

|

SU1256234A2 |

| Устройство синхронизации кодовой последовательности | 1988 |

|

SU1555893A1 |

Изобретение относится к импульсной технике и может использоваться в системах импульсно-фазовой автоподстройки частоты, в устр-вах автоматики и телемеханики. Цель изобретения - увеличение помехоустойчивости. Триггеры 1, 2 из соотв. входных сигналов формируют импульсные сигналы со скважностью, равной двум. Опрокидывание триггеров 1,2 происходит передними фронтами импульсов уровня логической . Элемент неравнозначности (ЭН) 3 при разноименных сигналах с выходов триггеров 1, 2 формирует импульсЫ;уровня логической 1, длительность которых пропорциональна разности фаз входных сигналов. D- триггер 5 тактируется сигналами уровня логической 1 с триггеров 1, 2. При сбое триггеров 1, 2 под воздействием помехи на его выходе устанавливается сигнал уровня логического О. В результате ЭН 4 инвертирует сигнал, поступающий на его вход с ЭН 3. При этом искажения выходного сигнала носят Локальный характер и охватывают не более двух периодов входного сигнала. 2 ил. (Л to 00 СП ел СП (UD ФигЛ

| Частотно-фазовый детектор | 1980 |

|

SU1040591A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Патент США № 4267514, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-01-23—Публикация

1985-01-04—Подача