Изобретение относится к электросвязи и может использоваться в системах обмена дискретной информацией.

Известно устройство передачи информации с каскадным кодом, содержащее последовательно соединенные блок кодирования внешнего кода, блок кодирования внутреннего кода, канал связи, декодер внутреннего кода и декодер внешнего кода 1.

Однако известное устройство имеет недостаточную помехоустойчивость и недостаточную эффективность пропускной способности.

Цель изобретения - повышение помехоустойчивости и скорости передачи информации.

Для этого в устройство передачи информации с каскадным кодом, содержащее последовательно соединенные блок кодирования внешнего кода, блок кодирования внутреннего кода, канал связи, декодер внутреннего кода, декодер внешнего кода, введены буферный блок, блок управления, а также последовательно соединенные дискриминатор повторяющихся комбинаций внутреннего кода и блок адаптации структуры декодера внешнего кода, выходы которого подключены к управляющим входам декодера внешнего кода, а к входу дискриминатора повторяющихся комбинаций внутреннего кода подсоединен выход декодера внутреннего кода. При этом выход блока управления подключен к управляющим входам блока кодирования внешнего кода и буферного блока, выход которого подсоединен к информационному входу блока кодироваHiiH внешнего кода.

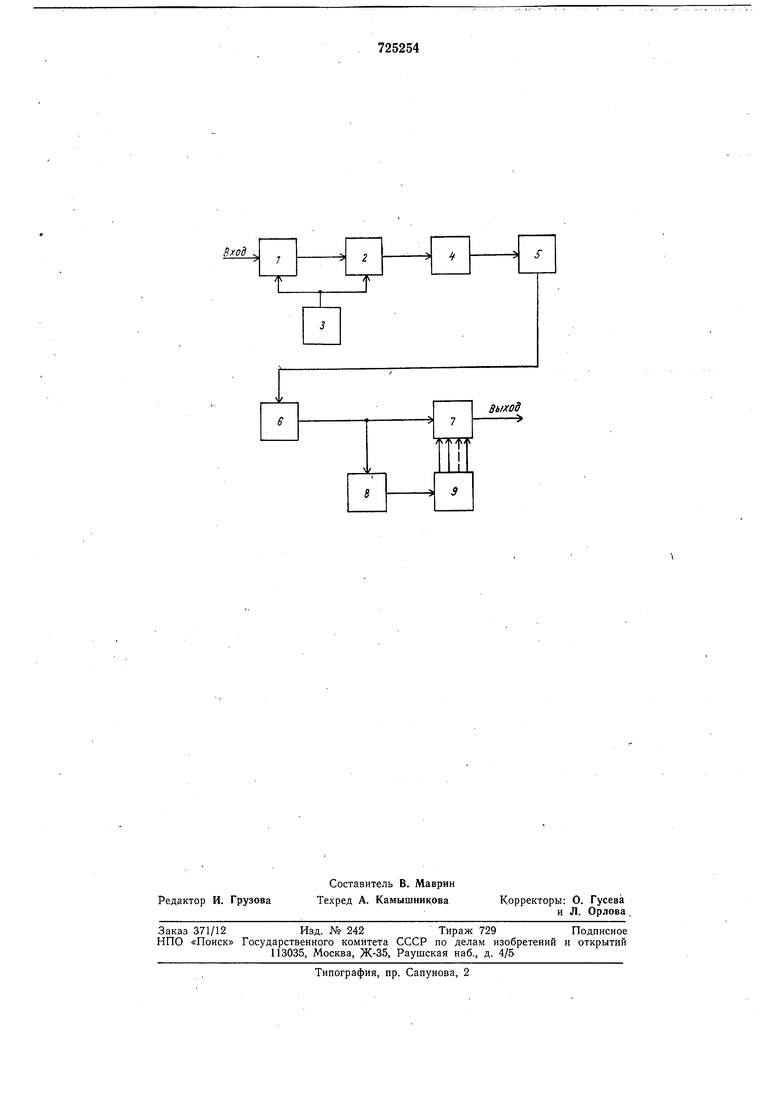

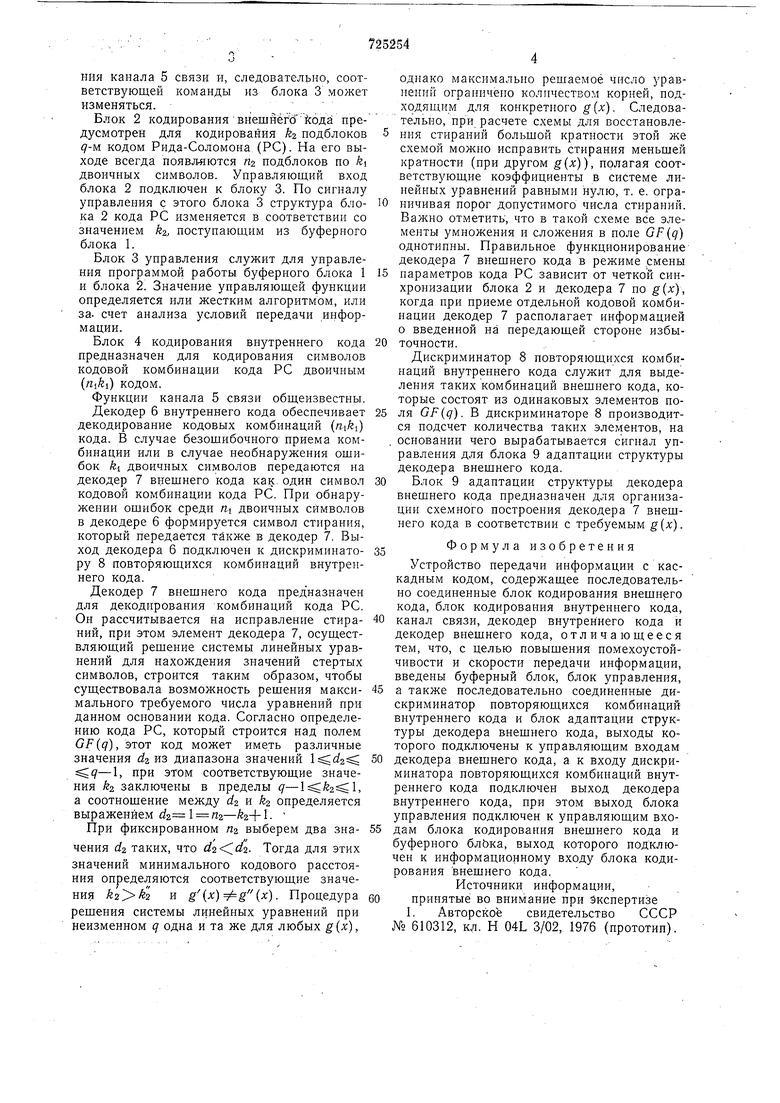

На чертеже приведена структурная электрическая схема предложенного устройства.

Устройство передачи информации содержит буферный блок 1, блок 2 кодирования внешнего кода, блок 3 управления, блок 4 кодирования внутреннего кода, канал 5 связи, декодер 6 внутреннего кода, декодер 7 внешнего кода, дискриминатор 8 повторяющихся комбинаций внутреннего кода, блок 9 адаптации структуры декодера внещнего кода.

Работает устройство следующим образом.

Буферный блок 1 предназначен для регулирования потока информационных подблоков, которые поступают на блок 2 кодирования внешнего кода. Вход буферного блока 1 является информационным входом устройства. Управляющий вход блока 1 связан с блоком 3. По сигналам управления из блока 3 с выхода буферного блока 1 на блок 2 кодирования внешнего кода поступают 2 подблоков по ki двоичных символов в каждом. Значение kz в зависимости от состояния канала 5 связи и, следовательно, соответствующей команды из блока 3 может изменяться.

Блок 2 кодирования внешнего йода предусмотрен для кодирования 2 нодблоков -м кодом Рида-Соломона, (PC). На его выходе всегда появляются П2 нодблоков но ki двоичных символов. Унравляющий вход блока 2 подключен к блоку 3. По сигналу унравления с этого блока 3 структ фа блока 2 кода PC изменяется в соответствии со значением kz, поступающим из буферного блока 1.

Блок 3 управления служит для унравления программой работы буферного блока 1 и блока 2. Значенпе управляющей функции определяется или жестким алгоритмом, или за. счет анализа условий нередачи информации.

Блок 4 кодирования внутреннего кода предназначен для кодирования символов кодовой комбинации кода PC двоичным (niki) кодом.

Функции канала 5 связи общеизвестны.

Декодер 6 внутреннего кода обеснечивает декодирование кодовых комбинаций () кода. В случае безошибочного приема комбинации или в случае необнаружения ошибок ki двоичных символов передаются на декодер 7 внещнего кода как. один символ кодовой комбинации кода PC. При обнаружении ошибок среди «1 двоичных символов в декодере 6 формируется символ стирания, который передается также в декодер 7. Выход декодера 6 подключен к дискриминатору 8 повторяющихся комбинаций внутреннего кода.

Декодер 7 внешнего кода предназначен для декоднрования комбинаций кода PC. Ои рассчитывается на исправление стираНИИ, при этом элемент декодера 7, осуществляющий рещение системы линейных уравнений для нахождения значений стертых символов, строится таким образом, чтобы существовала возможность рещения максимального требуемого числа уравнений при данном основании кода. Согласно онределению кода PC, который строится над полем GF(q), этот код может иметь различные значения 2 из диапазона значений (7-1, при этом соответствующие значения kz заключены в пределы , а соотнощение между 2 и kz оиределяется выражением dz 1 .

При фиксированном «2 выберем два значения Й2 таких, что . Тогда для этих значений минимального кодового расстояния онределяютсЯ соответствующие значения И g(x)). процедура решения системы линейных уравнений при неизменном q одна и та же для любых g(x),

однако максимально решаемое число уравнений ограничено количеством корней, нодходящим для конкретного (л). Следовательно, при расчете схемы для восстановления стираний большой кратности этой же схемой можио исправить стирания меньшей кратности (при другом g(x)), полагая соответствующие коэффициенты в системе лннейных уравненнй равными нулю, т. е. ограничивая порог допустимого числа стираний. Важно отметить, что в такой схеме все элементы умножения и сложения в поле GF(q) однотипны. Правильное функционирование декодера 7 внещнего кода в режиме .смены нараметров кода PC зависит от четкой синхронизации блока 2 и декодера 7 по g(x), когда при приеме отдельной кодовой комбииации декодер 7 раснолагает информацией о введенной на передающей стороне избыточности.

Дискриминатор 8 повторяющихся комбинаций внутреннего кода служит для выделения таких комбинаций внещнего кода, которые состоят из одинаковых элементов поля GF(q). В дискриминаторе 8 производится подсчет количества таких элементов, на основании чего вырабатывается сигнал управления для блока 9 адаптации структуры декодера внещнего кода.

Блок 9 адаптации структуры декодера внешнего кода предназначен для организации схемного построения декодера 7 внещнего кода в соответствии с требуемым g(x).

Формула изобретения

Устройство нередачи информации с каскадным кодом, содержащее носледовательно соединенные блок кодирования внещнего кода, блок кодирования внутреннего кода, канал связи, декодер внутреннего кода и декодер внешнего кода, отличающееся тем, что, с целью повыщения номехоустойчивости и скорости передачи информации, введены буферный блок, блок управления, а также последовательно соеднненные дискриминатор новторяющихся комбинаций внутреннего кода и блок адаптации структуры декодера внещнего кода, выходы которого подключены к управляющим входам декодера внешнего кода, а к входу дискриминатора повторяющихся комбииаций внутреннего кода подключен выход декодера внутреннего кода, при этом выход блока управления подключен к управляющим входам блока кодирования внешнего кода и буферного блЬка, выход которого подключен к информационному входу блока кодирования внешнего кода.

Источники информации, принятые во внимание при Экспертизе 1. Авторское свидетельство СССР №610312, кл. Н 04L 3/02, 1976 (прототип).

Вход

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ РАДИОВЕЩАТЕЛЬНОЙ ПЕРЕДАЧИ ЦИФРОВЫХ СООБЩЕНИЙ | 1994 |

|

RU2110148C1 |

| СПОСОБ КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ В СИСТЕМАХ ПЕРЕДАЧИ ДАННЫХ | 2005 |

|

RU2310273C2 |

| МЯГКИЙ ДЕКОДЕР ПОСЛЕДОВАТЕЛЬНОГО ТУРБОКОДА | 2013 |

|

RU2538331C2 |

| ЛЕКСИКОГРАФИЧЕСКИЙ ДЕКОДЕР КАСКАДНОГО КОДА | 2015 |

|

RU2619533C2 |

| СПОСОБ КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ КАСКАДНОЙ КОДОВОЙ КОНСТРУКЦИИ В СИСТЕМАХ ПЕРЕДАЧИ ДАННЫХ | 2009 |

|

RU2420870C1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ОШИБОК | 1991 |

|

RU2037271C1 |

| СПОСОБ КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ В СИСТЕМАХ ПЕРЕДАЧИ ДАННЫХ | 2014 |

|

RU2562435C1 |

| Способ обнаружения и исправления стираний при приеме дискретной информации | 2015 |

|

RU2611235C1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ С ЖЕСТКИМИ И МЯГКИМИ РЕШЕНИЯМИ ДЛЯ ДВУХСТУПЕНЧАТОГО КАСКАДНОГО КОДА И МОДУЛЯЦИИ ПО ТИПУ СТЫКА С1-ФЛ | 2024 |

|

RU2834891C1 |

Авторы

Даты

1980-03-30—Публикация

1978-08-04—Подача