Изобретение относится к вычислительной технике и может быть использовано в системах помехозащищенного кодирования и декодирования, в частности в оптических дисковых запоминающих устройствах.

Известна система, корректирующая ошибки [1] Она содержит генератор синдромов, блок оперативной памяти, генератор локаторов и вычислительное устройство, включающее арифметико-логический блок, сумматор по модулю два, регистры обмена, мультиплексоры, ПЗУ логарифмов и антилогарифмов, схему управления. Система производит вычисление и исправление до двух ошибок в кодовом слове. Ее основным отличительным признаком является генератор локаторов, выполняющий функцию вычисления локаторов ошибок и обратной величины суммы этих локаторов методом последовательной подстановки их значений в следующие уравнения:

f(x) x2 + λ 1x + λ 2 0 и

Sm αϕ ( αi + αj) α32m, где λ 1 αi + αj;

λ 2 αi˙ αj;

Sm модифицированный синдром ошибок.

Однако системе присущи следующие недостатки: она не позволяет корректировать стирания, т. е. непригодна для процедуры кодирования, сложность генератора локаторов и вычислительного устройства, большое количество шагов при нахождении обратного элемента.

Известна схема декодера Рида-Соломона [2] Она содержит генератор синдромов, генератор локаторов стираний, ПЗУ логарифмов, антилогарифмов и корней квадратного уравнения, ПЗУ команд, блок оперативной памяти, схему управления и вычислительное устройство, включающее арифметико-логический блок, регистры обмена и мультиплексоры. Схема производит вычисление и исправление любых комбинаций ошибок и стираний, удовлетворяющих следующему неравенству:

2 ν + 1 ≅ d l, где d кодовое расстояние Хемминга;

ν количество ошибок в кодовом слове;

l количество стираний в кодовом слове.

Однако схеме присущи следующие недостатки: вычислительное устройство содержит ПЗУ с большой избыточностью, операции сложения и умножения-деления несовмещены, что приводит к применению ПЗУ команд емкостью более 1 кбайта, процесс коррекции при декодировании выполняется за большое количество шагов, декодер требует сложной схемы управления.

Известна система, корректирующая ошибки [3] являющаяся наиболее близким техническим решением к изобретению по принципу действия и достигаемому результату. Она предназначена для использования в помехозащищенных цифровых системах, работающих с применением кодов Рида-Соломона. Система содержит генератор синдромов, блок оперативной памяти, детектор нулевого сигнала, ПЗУ логарифмов и антилогарифмов локаторов, контроллер флагов, схемы управления, генератор адреса команд со схемой управления, ПЗУ команд, регистр обмена коррекции, генератор локаторов, счетчик стираний, вычислительное устройство, включающее арифметико-логический блок, оперативные регистры, ПЗУ логарифмов и антилогарифмов (или ПЗУ обратного элемента, если в качестве арифметико-логического блока используется быстрый умножитель) и сумматор по модулю два.

Система по вычисленным синдромам ошибок и по сопровождающим кодовые слова флагам выполняет операции вычисления локаторов ошибок и стираний, значений ошибок и коррекцию символов. Причем исправляющая возможность системы ограничена выражением 2 ν + l ≅ d l. Все выше указанные операции в данной системе выполняются не более чем за 100 шагов и требуют для этого объем ПЗУ команд в 384 слова (каждое слово содержит не менее 9 бит).

Однако системе присущи следующие недостатки: большое количество ПЗУ-таблиц, необходимых для преобразований в поле Галуа (28), сложность контроллера флагов и схемы управления генератором адреса команд, нерациональное использование объема ПЗУ команд.

Целью изобретения является повышение информационной емкости устройства и его упрощение.

Цель достигается тем, что в устройство, включающее генератор синдромов, первый буферный блок, первый регистр флага, счетчик стираний, первый блок памяти локаторов, буферный блок локаторов, буферный блок флагов, блок памяти команд, регистр команд, блок оперативной памяти и детектор нулевого сигнала, арифметико-логический блок, первый компаратор, информационную шину, операционную шину и шину флаговых сигналов, введены блок синхронизации, первый-пятый регистры, буферный регистр, буферный блок обмена, второй и третий буферные блоки, генератор локаторов, мультиплексор локаторов, контроллер адреса локаторов, контроллер флага, второй регистр флага, преобразователь команд, блок памяти констант, сумматор, регистр анализа, шифратор, второй компаратор и первый-пятый мультиплексоры, при этом управляющие входы блока памяти констант, арифметико-логического блока, блока оперативной памяти, первого-пятого мультиплексоров, третьего-пятого регистров, регистра анализа, третьего буферного блока, первого и второго компараторов и шифратора объединены и подключены к управляющей шине, управляющий выход преобразователя команд подключен к управляющей шине, адресный выход преобразователя команд соединен с адресным входом блока оперативной памяти, выход которого подключен к информационным входам первого и третьего мультиплексоров, выход арифметико-логического блока подключен к второму информационному входу третьего мультиплексора, второй информационный вход которого соединен с выходом арифметико-логического блока, выход которого подключен к адресному входу блока памяти констант, выход которого соединен с первым информационным входом второго мультиплексора, второй информационный вход которого объединен с вторым информационным входом первого мультиплексора и подключен к выходу пятого мультиплексора, выход второго мультиплексора подключен к входу блокировки сумматора и к информационным входам третьего и четвертого регистров, выходы которых соединены соответственно с первым и вторым входами арифметико-логического блока и информационными входами первого и второго компараторов, выходы которых подключены к блокирующим входам сумматора, первый вход которого соединен с выходом третьего регистра, а выход подключен к информационному входу блока оперативной памяти, первому информационному входу четвертого мультиплексора и входу детектора нулевого сигнала, выход которого соединен с входом регистра анализа, выход которого подключен к второму информационному входу четвертого мультиплексора, выход которого соединен с входом третьего буферного блока, выход которого подключен к операционной шине, выход первого буферного блока, первый информационный вход пятого мультиплексора, выход буферного блока локаторов, первый вход мультиплексора локаторов, первый вход контроллера флагов и первый вход-выход буферного блока обмена подключены к операционной шине, второй вход-выход буферного блока обмена соединен с входом буферного регистра и выходом первого регистра, вход которого объединен с выходами буферного регистра и второго буферного блока, с входом второго регистра и подключен к информационной шине устройства, выход второго регистра соединен с входами второго буферного блока и генератора синдромов, выход которого подключен к входу первого буферного блока, управляющий вход которого объединен с управляющими входами генератора синдромов, буферного блока локаторов, шифратора, контроллера флага, преобразователя команд и выходом регистра команд, вход которого подключен к выходу блока памяти команд, управляющий вход которого подключен к первому управляющему выходу контролера флага, второй управляющий выход которого подключен к управляющему входу контроллера адреса локаторов, третий управляющий выход является управляющим выходом устройства, управляющий выход преобразователя команд подключен к управляющему входу контроллера флага, вход флага которого подключен к выходу второго регистра флага, а выход флага является контрольным выходом устройства и соединен с входом буферного блока флага, выход которого, а также входы первого и второго регистров флага подключены к шине флагового сигнала устройства, выход первого регистра флага соединен с управляющими входами первого блока памяти локаторов и счетчика стираний, выход которого подключен к второму информационному входу контроллера флага и адресному входу первого блока памяти локаторов, информационный вход которого соединен с выходом генератора локаторов, а выход подключен к второму входу мультиплексора локаторов, выход которого соединен с информационным входом второго блока памяти локаторов, адресный и управляющий входы которого подключены к соответствующим выходам контроллера адреса локаторов, а информационный выход соединен с информационным входом буферного блока локаторов и является выходом адреса коррекции устройства, выход шифратора подключен к второму информационному входу пятого мультиплексора, управляющий вход блока синхронизации является входом устройства, управляющий и адресный выходы блока синхронизации подключены к шине синхронизации и адресному входу блока памяти команд.

Сопоставительный анализ с прототипом показывает, что заявляемое устройство отличается измененными связями элементов схемы, а также наличием новых элементов, а именно блока синхронизации, первого-пятого регистров, буферного регистра, буферного блока обмена, второго и третьего буферных блоков, генератора локаторов, мультиплексора локаторов, контроллера адреса локаторов, контроллера флага, второго регистра флага, преобразователя команд, блока памяти констант, сумматора, регистра анализа, шифратора, второго компаратора и первого-пятого мультиплексоров.

Новая совокупность признаков позволяет применить модифицированный алгоритм декодера Рида-Соломона, который описан далее. За счет этого в заявляемом устройстве по сравнению с прототипом удалось уменьшить количество таблиц преобразований в поле Галуа(28) и объем ПЗУ команд, а также упростилась процедура анализа результатов промежуточных вычислений. Все указанное выше позволяет повысить эффективность устройства и упростить его реализацию.

Сравнение заявленного технического решения с прототипом позволило установить соответствие критерию "новизна". При изучении других известных технических решений в данной области техники признаки, отличающие изобретение от прототипа, не были выявлены, поэтому они обеспечивают заявляемому техническому решению соответствие критерию "существенные отличия".

На фиг. 1 изображена диаграмма процедуры кодирования; на фиг. 2 диаграмма процедуры декодирования; на фиг. 3 структурная схема CIRC-декодера; на фиг. 4 алгоритм вычисления ошибок; на фиг. 5 алгоритм вычисления стираний; на фиг. 6 структурная схема заявляемого устройства, корректирующего ошибки; на фиг. 7 структура командного слова.

На фиг. 1 и 2 представлен один из вариантов реализации процедуры кодирования и декодирования для перекрестно-перемежаемых кодов Рида-Соломона (CIRC).

В CIRC-кодере, процедура обработки информации в котором изображена на фиг. 1, выполняется двойное кодирование посредством применения кодов Рида-Соломона. Для этого к 24 информационным символам Wi, прошедшим через перемежитель 1, добавляются в кодере 2 четыре проверочных символа Q0.Q3. Далее вновь организованное кодовое слово, пропущенное через перемежитель 3 (D кратность величины задержки информации), повторно кодируется в кодере 4, в результате чего к информации добавляется еще четыре проверочных символа P0. P3. Выходным кодовым словом является слово, полученное в результате прохождения закодированной в кодере 4 информации через перемежитель 5.

В CIRC-декодере, процедура обработки информации в котором изображена на фиг. 2, происходит обратное перемежение кодового слова соответственно в перемежителях 6, 8, и 10. Одновременно с этим производится двойное декодирование CIRC-кода в декодерах 7 и 9, в результате чего корректируются возможные ошибки. После коррекции соответствующие проверочные символы отбрасываются. На выходе декодера получают исходные информационные символы Wi.

Структурная схема кодека, обеспечивающая вышеуказанные процедуры кодирования и декодирования, представлена на фиг. 3. CIRC-кодек состоит из контроллера 14 управления, контроллера 16 памяти, блока 17 оперативной памяти и заявляемого устройства 15, корректирующего ошибки. По входу 11 кодека поступают синхросигналы, поддерживающие его работу и обеспечивающие согласованную работу кодека с внешними устройствами. При этом контроллер 14 управления формирует на выходах 18 и 19 сигналы приема и передачи информации, пересылаемой через входы-выходы 12 и 13 между внешними устройствами и внутренними шинами (информационной BD и флага BFL). Контроллер управления формирует также необходимые сигналы управления для устройства 15 и контроллера 16 памяти. Процедуры обработки информации производятся в блоке 17 оперативной памяти по специально сформированным адресам и управляющим сигналам, поступающим из контроллера 16 памяти. Для каждой из элементов процедуры обработки в блоке 17 памяти организованы соответствующие области памяти. Пересылка информации из области в область памяти поддерживается по шинам BD и BFL устройством 15. Одновременно устройство 15 выполняет функции кодеров 2 и 4 (см. фиг. 1) и декодеров 7 и 9 (см. фиг. 2), для чего оно производит обработку информации, поступающей по шинам BD и BFL. В результате устройство 15 вычисляет значения ошибок и их локаторов. По вычисленным значениям локаторов, поступающих на адресный вход контроллера 16 флага, вызываются из блока 17 памяти соответствующие месту этих локаторов ошибочные символы. После коррекции их в устройстве 15 исправленные символы заносятся в исходное место блока 17 памяти. Одновременно происходит изменение состояния сопровождающих кодовое слово флагов посредством выдачи на шину BFL во время перезаписи информации в блоке 17 памяти соответствующего значения флага.

В заявляемом устройстве, корректирующем ошибки, режим кодирования соответствует режиму декодирования с коррекцией стираний, т.е. ошибок с заранее известными значениями локаторов. Таким образом в заявляемом устройстве функции кодера 4 и декодера 7 выполняет декодер CI, совмещенный с декодером СII, выполняющим функции кодера 2 и декодера 9. Отличие декодеров СI и CII заключается в длине обрабатываемого кодового слова.

Работа заявляемого устройства будет понята из следующего описания.

Все операции в устройстве производятся над полем Галуа GF(28). В устройстве используется код Рида-Соломона длиной, удовлетворяющей следующему неравенству:

n ≅ (28 1). причем число информационных символов в коде соответствует следующему значению:

k n 2t, где 2t количество проверочных символов в кодовом слове.

Для расстояния Хемминга данного кода

d 2t + 1 исправляющая возможность заявляемого устройства ограничена следующим неравенством:

2 ν + l ≅ d l, где ν количество ошибок;

l количество стираний.

Порождающий многочлен имеет вид

g(x) (x+ αmo) (x+ αmo+1) (x+ αmo+2).

(x+ αmo+2+1).

Кодовое слово, представленное в полиномиальном виде,

V(x) Vo + V1x +V2x2 + +Vn-1xn-1, делится на g(x), т.е.

V(x) (mod g(x)) 0.

Принятое слово, подлежащее декодированию, можно представить как

С(x) Co + C1x + C2x2 + +Cn-1 xn-1, причем

С(x) (mod g(x)) [V(x) + E(x)] (mod g(x)) E(x).

При этом полином ошибок E(x) для ошибок можно представить в виде

E(x) ejxij (0≅j≅n-1)

ejxij (0≅j≅n-1)

Из полинома ошибок E(x) получают синдромы ошибок Sm в виде

Sm- C( )= E(

)= E( )

) e

e (0≅ m≅ 2t-1).

(0≅ m≅ 2t-1).

В общем виде полином синдромов имеет вид

S(x)  Sixi

Sixi

Через полученные синдромы в процессе декодирования вычисляют коэффициенты многочлена локаторов (х), имеющего вид

Λ(x)  (1+Xjx)

(1+Xjx) xj, где Xj локатор ошибок или стираний.

xj, где Xj локатор ошибок или стираний.

Коэффициенты могут быть вычислены из выражения

Sm+ν + λ1 Sm+ν-1+ + λν-1 Sm+1 + λν Sm 0, (1) где m 0.( ν -1).

Значения локаторов ошибок X находят при решении уравнения

λ (x) 0.

После вычисления локаторов ошибок значения самих ошибок находят из решения следующего уравнения:

Ω(x) S(x) Λ(x) (mod x2+) ejX

ejX (1+Xix) где e значение ошибки, которое можно представить в виде

(1+Xix) где e значение ошибки, которое можно представить в виде

ej λ (Xj) * Xj-mo+1 /λ (Xj) для каждого конкретного локатора.

Для случая t=2 и m=0 имеют порождающий многочлен

g(x) (x+1) (x+ α) (x+ α2) (x+ α3).

Тогда уравнение (1) можно представить в виде

для ν 1

S1+ λ 1*S0 0;

S2+ λ 1*S1 0;

S3+ λ 1*S2 0, откуда следует, что

λ 1=S1/S0=S2/S1=S3/S2;

для ν2

S2+ λ 1*S1+ λ 2*S0=0;

S3+ λ 1*S2+ λ 2*S1=0, откуда следует, что

λ 1=a/c=X1+X2;

λ 2=d/c=X1*X2, (2) где

a=S0*S3+S1*S2;

f=S1*S3+S

c=S

Для решения системы (2) используется общеизвестный способ решения квадратного уравнения через табличную функцию с переменной ( λ 2/( λ 1)2. Корень этого уравнения (y) используется для нахождения локаторов ошибок

X1= λ 1*y;

X2=X1+ λ 1.

Если принять за основу утверждение, что

z*0= z/0= 0/z=0/0=0, (3) то выражение для λ 1 в системе (2) можно представить, как

λ 1= S1/S0+(c*S1/S0+a)/c, тогда для двух и одной ошибок можно использовать одинаковый алгоритм декодирования (так называемый модифицированный алгоритм декодирования ошибок). Это приводит к повышению эффективности и сокращению программного обеспечения декодера.

Модифицированный алгоритм вычисления ошибок представлен на фиг. 4.

Алгоритм вычисления стираний (см. фиг. 5) для известного массива локаторов стираний [Xi] приведен, исходя из решения системы линейного уравнения для синдромов с учетом ранее принятого утверждения (3).

Процесс исправления информации заключается в следующей операции:

Vi=Ci+ei.

Структурная схема заявляемого устройства представлена на фиг. 6. Оно содержит первый регистр 20, буферный регистр 21, буферный блок 22 обмена, второй регистр 23, второй буферный блок 24, генератор 25 синдромов, первый буферный блок 26, первый регистр 27 флага, счетчик 28 стираний, первый блок 29 памяти локаторов, генера- тор 30 локаторов, мультиплексор 31 локаторов, контроллер 32 флага, контроллер 33 адреса локаторов, второй блок 34 памяти локаторов, второй регистр 35 флага, буферный блок 36 флагов, буферный блок 37 локаторов, детектор 38 нулевого сигнала, регистр 39 анализа, четвертый мультиплексор 40, третий буферный блок 41, блок 42 оперативной памяти, сумматор 43, пятый регистр 44, третий мультиплексор 45, арифметико-логический блок 46, третий регистр 47, четвертый регистр 48, первый мультиплексор 49, первый компаратор 50, второй компаратор 51, второй мультиплексор 52, блок 53 памяти констант, пятый мультиплексор 54, шифратор 55, преобразователь 56 команд, блок 57 синхронизации, блок 58 памяти команд, регистр 59 команд, операционную шину 60, информационную шину 12, шину 13 флага, управляющий вход 61, выход 62 адреса коррекции, управляющий выход 63, контрольный выход 64, шину 65 синхронизации, шину 66 управления.

Устройство, корректирующее ошибки, работает следующим образом.

По управляющему входу 61 производятся начальная установка и последующий запуск блока 57 синхронизации, который вырабатывает установочные импульсы, сигналы обмена, адреса команд и тактовую частоту для внутренних компонентов устройства.

Обработка кодового слова производится сразу по двум декодерам CI и CII за два кадра (длительностью 588 тактов каждый). В первом кадре производится вычисление синдромов в генераторе 25, для чего в регистр 23 последовательно заносятся символы корректируемого кода, по которым генератор 25 синдромов производит следующую рекурсию:

Sk Ci Sk* αk. где k 0, 1, 2, 3;

i 0.(N-1). причем для CI N=32, а для CII N=28.

Обработанные символы корректируемого кода выдаются на шину 12 через буферный блок 24 для записи в область CI или CII внешней памяти. Одновременно вычисляются количество стираний и их локаторы. Для этого флаги стираний с шины 13 фиксируются в регистре 27. В случае соответствия флага уровню логической "1" происходит изменение состояния счетчика 28 и генератора 30 локаторов, при этом предыдущая информация из генератора локаторов записывается в блок 29 памяти. Обработанный флаг регистр 27 выдает на шину 13 для записи в область CI или CII внешней памяти.

По завершении обработки первого кодового слова вычисленные значения синдромов перезаписываются во внутреннюю память генератора 25 синдромов, далее они могут быть выданы на операционную шину 60 через буферный блок 26, значения локаторов перезаписываются из блока 29 памяти через второй вход мультиплексора 31 в блок 34 памяти независимо от состояния на его адресном входе, а значение счетчика 28 стираний во внутреннюю память контроллера 32 флага. После этого генератор 25 синдромов, счетчик 28 и блок 29 памяти готовы к обработке нового корректируемого кодового слова.

По известным значениям синдромов, локаторов и количеству стираний во втором кадре производится вычисление истинных значений ошибок Yi и их локаторов с последующей коррекцией кодового слова.

Алгоритмы состоят из четырехтактных операций вычисления, выполняемых следующим образом. Первый операнд A заносится по первому такту в регистр 47 с выхода мультиплексора 49, второй операнд B заносится по второму такту в регистр 48 с выхода мультиплексора 49.

После второго такта результат сложения первого и второго операндов в арифметико-логическом блоке 46, который представляет собой сумматор по модулю 255, пройдя через второй вход мультиплексора 52, блок памяти констант и второй вход мультиплексора 49, поступает на блокируемый вход сумматора 43. Блокировка происходит в случае, если на вход одного из компараторов 50 и 51 подан операнд, соответствующий значению 255, что позволяет реализовать условие (3). В сумматоре 43 производится сложение выше указанного результата сложения первого и второго операндов с третьим операндом С, фиксируемым в регистре 44 в третьем такте. Результат вычисления операции в четвертом такте может быть записан в блок 42 памяти объемом 16 байт либо выдан на операционную шину 60 через второй вход мультиплексора 40 и буферный блок 41. Для анализа значения этого результата на 0 он поступает также на вход детектора 38 нулевого сигнала, после чего результат анализа может быть записан в регистр 39, в качестве которого применяется последовательный регистр. Информация о состоянии регистра 39 анализа может быть выдана через первый вход мультиплексора 40 и буферный блок 41 на операционную шину 60. Причем буферный блок 41 может быть открыт только в четвертом такте операции.

Мультиплексор 52 позволяет пропускать через таблицы памяти операнды, взятые из блока 42 памяти в первом и втором тактах вышеуказанной операции вычисления. Для сокращения времени вычисления в нулевой ячейке блока 42 памяти хранится постоянное число 0.

Блок 53 памяти содержит следующие таблицы преобразования в поле GF(28): элемент поля в номер места элемента поля, номер места элемента поля в элемент поля, значение номера места элемента поля в значение из таблицы корней квадратного уравнения, повторение (элемент в тождественный элемент).

Операция вычисления характеризуется следующими математическими функциями над операндами:

A * B + C;

A / B + С.

Благодаря мультиплексорам 45 и 49 операции вычисления могут производиться как над операндами, взятыми из блока 42 оперативной памяти, так и над операндами, поступающими с операционной шины 60 через первый вход мультиплексора 54. Мультиплексор 54 вместе с шифратором 55 выполняет функцию кодирования, формируя значения номеров места локатора в кодовом слове.

Функция преобразователя 56 команд заключается в преобразовании командного слова, поступающего с выхода регистра 59 команд, по синхронизации с шины 65 в управляющие сигналы, поступающие на шину 66 управления, и адреса блока 42 оперативной памяти, поддерживающие операции вычисления. В формате кодового слова, представленного на фиг. 7, разряд INS7 определяет источник операнда, используемого в операции вычисления, т.е. либо блок оперативной памяти, либо шину 60. По команде БЛОК производятся отключение блокировки в сумматоре 43 и изменение модуля сумматора 46. Команда АЛУ включает один из режимов работы сумматора 46, а именно либо суммирование, либо вычитание. При наличии команды0 в регистр 39 записывается результат анализа на 0 данных, полученных в итоге операции вычисления. По команде ГОТ информация из регистра 39 поступает на шину 60 и одновременно в контроллере 56 строб передачи результатов анализа в котроллер 32 флага. Команда ВН позволяет в четвертом такте операции вычисления подключать к шине 60 внешние источники. Команды "таблица ПЗУ" инициализируют включение одной из таблиц блока 53 памяти констант.

Результат анализа в процессе вычислений заносится в контроллер 32 флага, а дополнительно вычисленные локаторы ошибок поступают как в блок 34 памяти, так и в контроллер 32, где производится его анализ на принадлежность его множеству локаторов кодового слова. Локаторы из блока 34 памяти могут выдаваться как на шину 60 через буферный блок 37, так и на выход 62 адреса коррекции.

После завершения вычисления значений ошибок и их локаторов по адресу, выставленному на выход 62, производится вызов из внешнего блока 17 оперативной памяти корректируемого символа, который через шину 12, регистр 20 и буферный блок 22 обмена поступает в устройство, где суммируется по модулю два со значением Yi. Далее скорректированный символ через буферные блоки 22 и 21 выдается на шину 12 и заносится в исходное место блока 17 оперативной памяти.

В устройстве регистр 20 и буферный блок 21 в промежутках между коррекциями используются для поддержания режима обмена информации по шине 12.

По выходу 63 контроллер 32 может блокировать коррекцию в случае, если количество ошибок превышает исправляющие возможности устройства. Для этого выход 63 подключен к контроллеру 16 внешней памяти вместе с выходом 62 адреса коррекции.

Контроллер 32 принимает окончательное решение о возможности коррекции ошибок по соотношениям результатов анализа и количеству стираний. После принятия решения контроллер 32 выдает на контрольный выход 64 информацию о кодовом слове, а также производит инициализацию флагов. Для трансляции ранее установленных флагов используется регистр 35, принимающий флаги с шины 13 флага. Инициализированные флаги поступают через буферный блок 36 на шину 13 для записи во внешний блок 17 оперативной памяти.

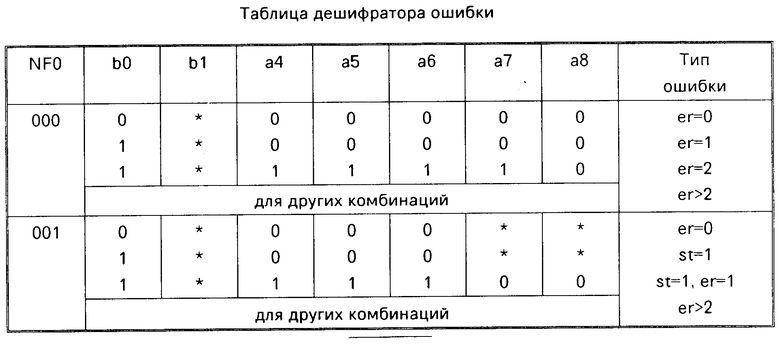

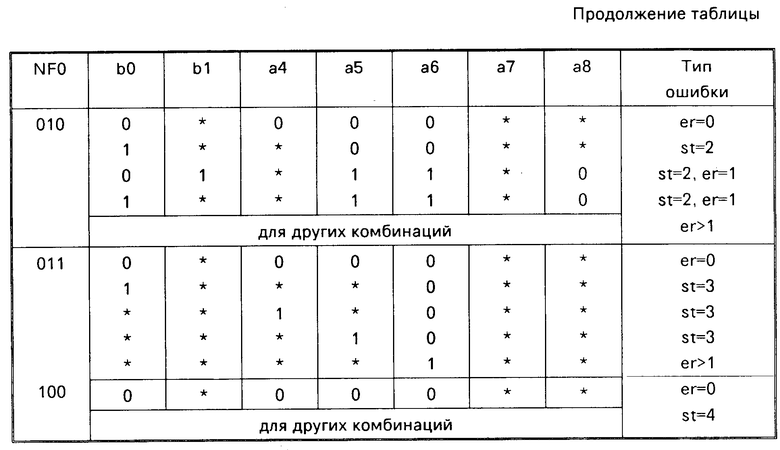

Обработка результатов анализа начинается с следующего переприсвоения:

b0=a0 / a3;

b1=a1*a2.

Далее с учетом состояния внутреннего регистра флага, который хранит информацию, ранее просчитанную в счетчике 28, о количестве флагов F0(NF0) для декодера CI, а также флагов F0 (NF0) и F1 (NF1) для декодера CII контроллер 32 в соответствии с таблицей дешифратора ошибки и алгоритмом вырабатывает команду разрешения коррекции (k), поступающую на выход 66, и флаги по каналам F0 и F1 для декодера CI и F0, F1 и F2 для декодера CII, выдаваемые на контрольный выход 66 и далее на шину 13.

Для переключения программ (стирание или ошибки) в блок 58 памяти команд из контроллера 32 на его управляющий вход поступает соответствующий сигнал.

Экспериментальные работы заявленного устройства, корректирующего ошибки, в составе кодека Рида-Соломона для оптических запоминающих устройств показали, что по сравнению с устройством аналогичного назначения (прототипом) заявленное устройство позволяет более эффективно использовать программные ресурсы, т.е. резко сокращается объем используемых ПЗУ, а также значительно упрощается его реализация, что позволяет с успехом реализовать заявленное устройство на полузаказных КМОП матричных БИС с небольшой степенью интеграции.

| название | год | авторы | номер документа |

|---|---|---|---|

| Канальный кодек | 1990 |

|

SU1798922A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| ДЕКОДЕР С ИСПРАВЛЕНИЕМ ОШИБОК | 1993 |

|

RU2054224C1 |

| Устройство для декодирования кода Рида-Соломона | 1985 |

|

SU1332539A1 |

| Устройство для декодирования блочных кодов, согласованных с многопозиционными сигналами | 1987 |

|

SU1543552A1 |

| Устройство для декодирования двоичных блочных кодов, согласованных с многопозиционными сигналами | 1987 |

|

SU1587644A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА НА БАЗЕ МАТРИЦЫ ПРОЦЕССОРНЫХ ЭЛЕМЕНТОВ | 1998 |

|

RU2117326C1 |

| Устройство декодирования произведений кодов Рида-Соломона | 2017 |

|

RU2677372C1 |

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ КОДА РИДА - СОЛОМОНА | 1991 |

|

RU2007040C1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ КАСКАДНОГО КОДА РИДА-СОЛОМОНА | 1993 |

|

RU2036512C1 |

Изобретение относится к вычислительной технике и может быть использовано в системах помехозащищенного кодирования и декодирования, в частности в оптических дисковых запоминающих устройствах. Целью изобретения является повышение информационной емкости устройства и его упрощение. Оно содержит пять регистров, буферный регистр, буферный блок обмена, три буферных блока, генератор синдромов, два регистра флага, счетчик стираний, два блока памяти локаторов, генератор локаторов, мультиплексор локаторов, контроллер флага, контроллер адреса локаторов, буферный блок флага, буферный блок локаторов, детектор нулевого сигнала, регистр анализа, пять мультиплексоров, блок оперативной памяти, сумматор, арифметико-логический блок, два компаратора, блок памяти констант, шифратор, преобразователь команд, блок синхронизации, блок памяти команд, регистр команд, операционную шину, информационную шину, шину флаговых сигналов, управляющий вход, выход адреса коррекции, управляющий выход, контрольный выход, шину синхронизации, шину управления. Устройство кодирует или декодирует поступающее по информационной шине принятое слово, причем при декодировании устройство может исправить до двух ошибок или до четырех стираний в слове. Устройство может обрабатывать непрерывный поток информации. 7 ил., 1 табл.

УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ОШИБОК, содержащее генератор синдромов, первый буферный блок, первый регистр флага, счетчик стираний, первый блок памяти локаторов, буферный блок локаторов, буферный блок флагов, блок памяти команд, регистр команд, блок оперативной памяти и детектор нулевого сигнала, арифметико-логический блок, первый компаратор, информационную шину, операционную шину и шину флаговых сигналов, отличающееся тем, что, с целью повышения информационной емкости устройства и его упрощения, в него введены блок синхронизации, первый пятый регистры, буферный регистр, буферный блок обмена, второй и третий буферные блоки, генератор локаторов, мультиплексор локаторов, контроллер адреса локаторов, контроллер флага, второй регистр флага, преобразователь команд, блок памяти констант, сумматор, регистр анализа, шифратор, второй компаратор и первый пятый мультиплексоры, управляющие входы блока памяти констант, арифметико-логического блока, блока оперативной памяти, первого пятого мультиплексоров, третьего пятого регистров, регистра анализа, третьего буферного блока, первого и второго компараторов и шифратора объединены и подключены к управляющей шине, управляющий выход преобразователя команд подключен к управляющей шине, его адресный выход соединен с адресным входом блока оперативной памяти, выход которого подключен к информационным входам первого и третьего мультиплексоров, выход арифметико-логического блока подключен к второму информационному входу третьего мультиплексора, второй информационный вход которого соединен с выходом арифметико-логического блока, выход которого подключен к адресному входу блока памяти констант, выход которого соединен с первым информационным входом второго мультиплексора, второй информационный вход которого объединен с вторым информационным входом первого мультиплексора и подключен к выходу пятого мультиплексора, выход второго мультиплексора подключен к входу блокировки сумматора и к информационным входам третьего и четвертого регистров, выходы которых соединены соответственно с первым и вторым входами арифметико-логического блока и информационным входами первого и второго компараторов, выходы которых подключены к блокирующим входам сумматора, первый вход которого соединен с выходом третьего регистра, а выход подключен к информационному входу блока оперативной памяти, первому информационному входу четвертого мультиплексора и входу детектора нулевого сигнала, выход которого соединен с входом регистра анализа, выход которого подключен к второму информационному входу четвертого мультиплексора, выход которого соединен с входом третьего буферного блока, выход которого подключен к операционной шине, выход первого буферного блока, первый информационный вход пятого мультиплексора, выход буферного блока локаторов, первый вход мультиплексора локаторов, первый вход контроллера флагов и первый вход-выход буферного блока обмена подключены к операционной шине, второй вход-выход буферного блока обмена соединен с входом буферного регистра и выходом первого регистра, вход которого объединен с выходами буферного регистра и второго буферного блока, с входом второго регистра и подключен к информационной шине устройства, выход второго регистра соединен с входами второго буферного блока и генератора синдромов, выход которого подключен к входу первого буферного блока, управляющий вход которого объединен с управляющими входами генератора синдромов, буферного блока локаторов, шифратора, контроллера флага, преобразователя команд и выходом регистра команд, вход которого подключен к выходу блока памяти команд, управляющий вход которого подключен к первому управляющему выходу контроллера флага, второй управляющий выход которого подключен к управляющему входу контроллера адреса локаторов, третий управляющий выход является управляющим выходом устройства, управляющий выход преобразователя команд подключен к управляющему входу контроллера флага, вход флага которого подключен к выходу второго регистра флага, а выход флага является контрольным выходом устройства и соединен с входом буферного блока флага, выход которого, а также входы первого и второго регистров флага подключены к шине флагового сигнала устройства, выход первого регистра флага соединен с управляющими входами первого блока памяти локаторов и счетчиком стираний, выход которого подключен к второму информационному входу контроллера флага и адресному входу первого блока памяти локаторов, информационный вход которого соединен с выходом генератора локаторов, а выход подключен к второму входу мультиплексора локаторов, выход которого соединен с информационным входом второго блока памяти локаторов, адресный и управляющий входы которого подключены к соответствующим выходам контроллера локаторов, а информационный выход соединен с информационным входом буферного блока локаторов и является выходом адреса коррекции устройства, выход шифратора подключен к второму информационному входу пятого мультиплексора, управляющий вход блока синхронизации является входом устройства, управляющий и адресный выходы блока синхронизации подключены к шине синхронизации и адресному входу блока памяти команд.

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Патент США N 4677622, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Кузнечная нефтяная печь с форсункой | 1917 |

|

SU1987A1 |

Авторы

Даты

1995-06-09—Публикация

1991-06-28—Подача