(54) ДЕШИФРАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Дешифратор | 1983 |

|

SU1119167A1 |

| Дешифратор троичного кода 1,0,1 | 1983 |

|

SU1106015A1 |

| Дешифратор троичного кода 1,0,1 | 1978 |

|

SU748407A1 |

| Дешифратор | 1977 |

|

SU702517A1 |

| Дешифратор | 1986 |

|

SU1361724A1 |

| Дешифратор | 1979 |

|

SU790297A1 |

| Дешифратор | 1986 |

|

SU1345352A1 |

| Преобразователь троичного кода 1,0,1 в двоичный код | 1978 |

|

SU741261A1 |

| Преобразователь троичного кода 1,0,1 в двоичный код | 1979 |

|

SU773615A1 |

| Преобразователь двоичного кода в троичный код 1,0,1 | 1978 |

|

SU750477A1 |

Изобретение относится к области автоматики и вычислительной техники.

Известны дешифраторы 1 , содержащие группы блоков, двухвходсвые и трехвходовы троичные логические элементы. Недостатками известных устройств являются сложная реализация и низкая надежность.

Наиболее близким техническим решением к изобретению является дешифратор 2, содержащий двухвходовые и трехвходовые логические зпементы. Такой дешифратор имеет сложную реализацию.

Целью изобретения является упрощение дешифратора.

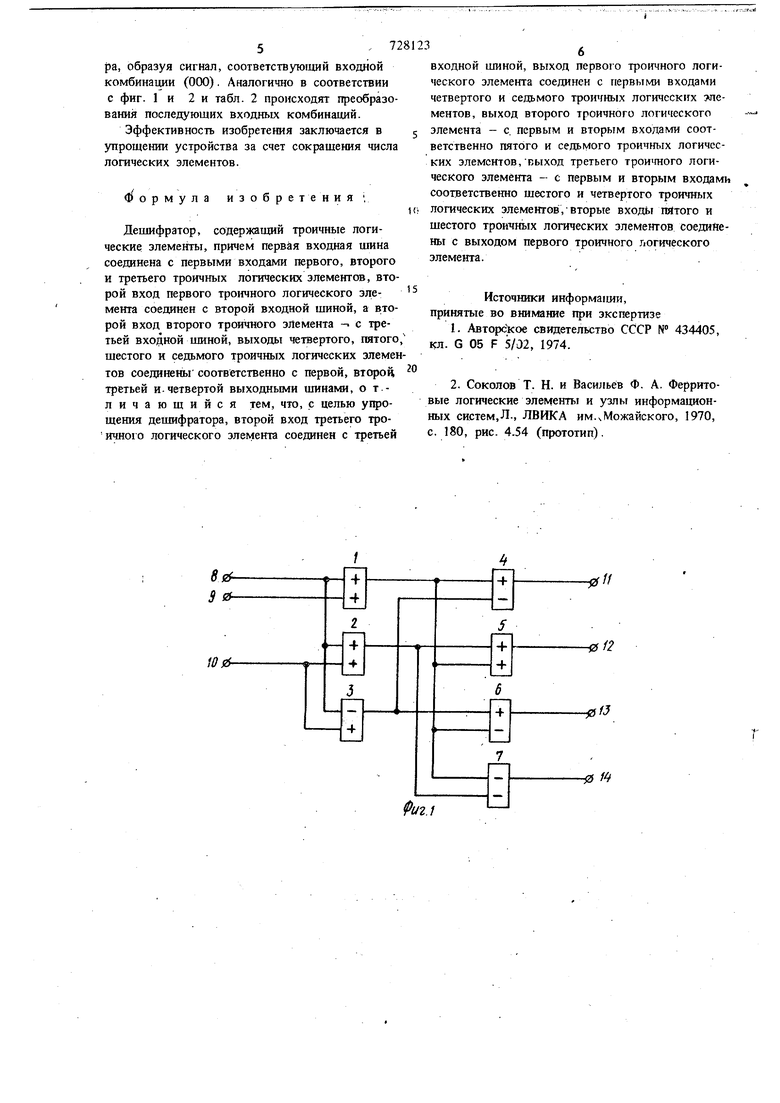

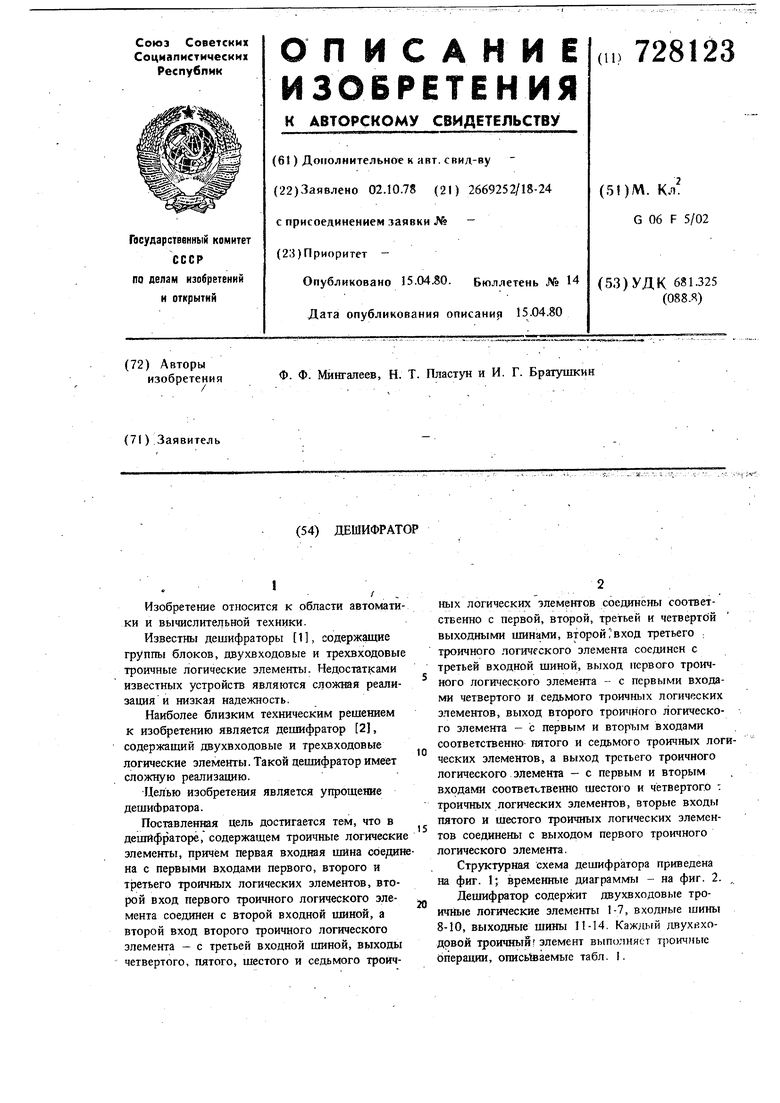

Поставленная цель достигается тем, что в дешифраторе, содержащем троичные логически элементы, причём первая входная шина сое/щнна с первыми входами первого, второго и третьего троичных логических элементов, второй вход первого троичного логического элемента соединен с второй входной шиной, а второй вход второго троичного логического элемента - с третьей входной шиной, выходы четвертого, пятого, шестого и седьмого троичных логических элементов соединены соответственно с первой, второй, третьей и четвертой выходными шинами, второй вход третьего ; троичного логического элемента соединен с третьей входной шиной, выход первого троичного логического элемента - с первыми входами четвертого и седьмого троичных логических элементов, выход второго троичного логического элемента - с первым и вторым входами соответственно пятого и седьмого троичных логических элементов, а выход третьего троичного логического элемента - с первым и вторым входами соответственно шесто)-о и четвертого : троичных логических элементов, вторые входы пятого и шестого троичных логических элементов соединены с выходом первого троичного логического элемента.

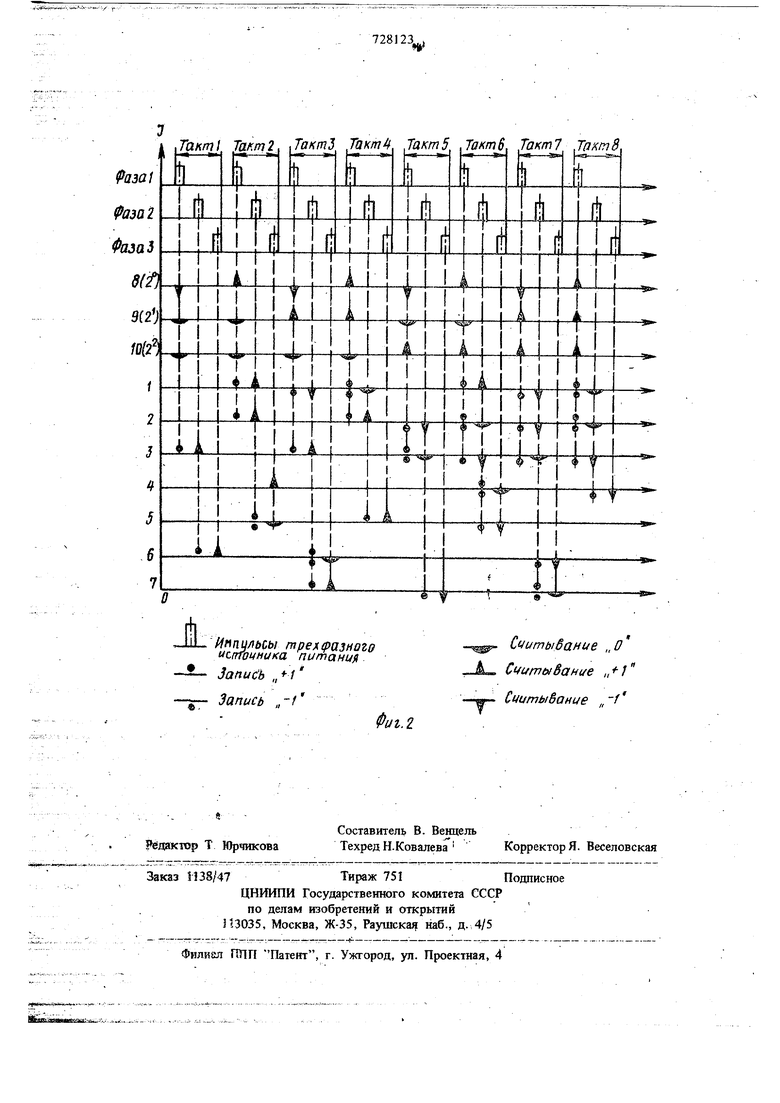

Структурная схема дешифратора приведена на фиг. 1; временные диаграммы - на фиг. 2. ,

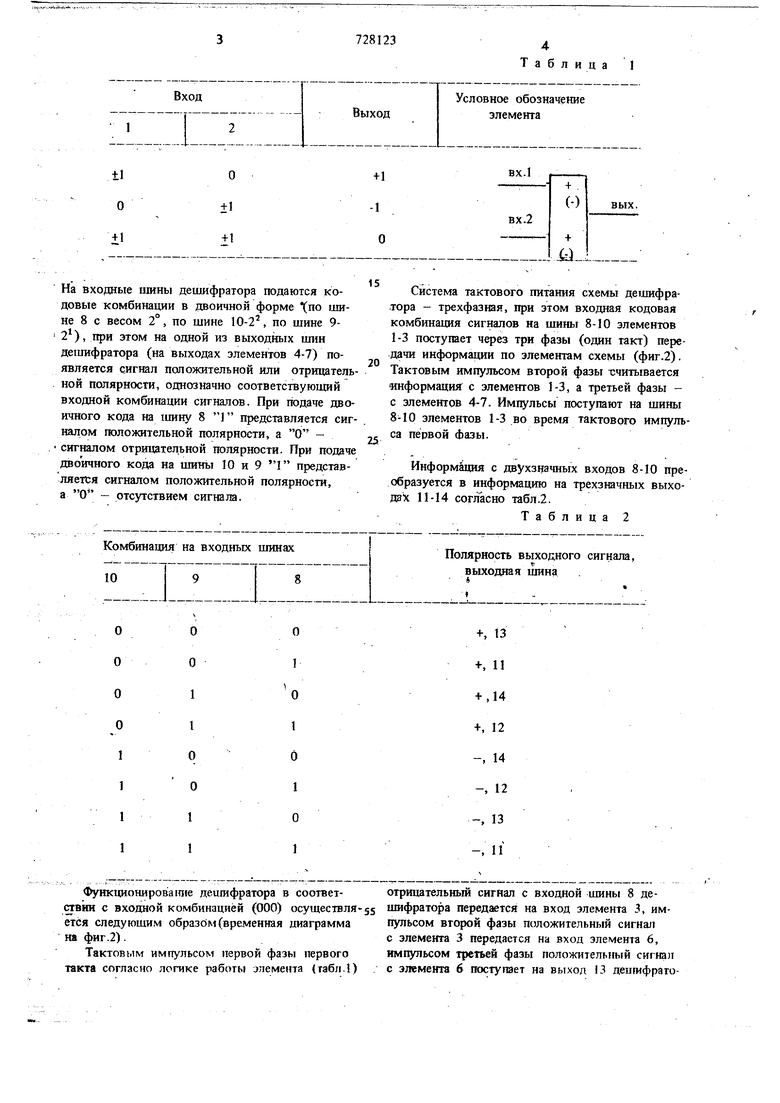

Дешифратор содержит двухвходовые троичные логические элементы 1-7, входные шины 8-10, выходные шины 11-14. Каждый двухвходрвой троичный элемент выполняет троичные Операции, опись аемые табл. 1.

На входные глины дешифратора подаются кодовые комбинации в двоичной форме (по шине 8 с весом 2°, по шине 10-2, но шине 92), при этом на одной из выходных шин де1Ш1фратора (на выходах элементов 4-7) ноявляется сигнал положительной или отрицательной полярности, одаозначно соответствующий входной комбинации сигналов. При подаче двоичного кода на 1Ш1ну 8 1 представляется сигналом положительной полярности, а О сигналом отрицательной полярности. При подаче двоичного кода на шины 10 и 9 представляется сигналом положительной полярности, а О - отсутствием сигнала.

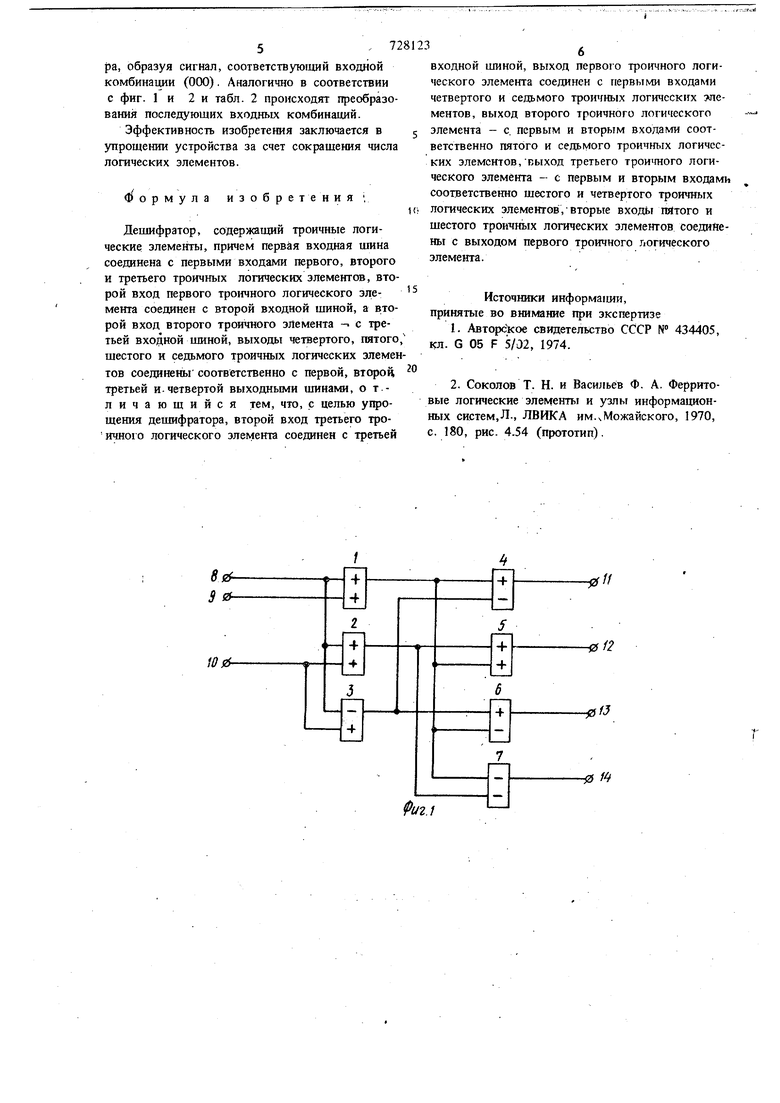

Функционировагтие дешифратора в соответствии с входной комбинацией (000) осуществля-55 етСя следуюшим образбм (временная диаграмма на фиг.2).

Тактовым импульсом первой фазы первого такта согласно логике работы отемеита (габл.1)

Система тактового питания схемы деишфратора - трехфазная, при этом входная кодовая комбинация сигналов на шины 8-10 элементов 1-3 поступает через три фазы (один такт) передачи информации по элементам схемы (фиг.2). Тактовым импульсом второй фазы считывается информация с элементов 1-3, а третьей фазы с элементов 4-7. Импульсы поступают на шины 8-10 элементов 1-3 во время тактового импульса первой фазы.

Информация с двухзначных входов 8-10 преобразуется в информацию на трехзначных выходах 11-14 согласно табл.2.

Таблица 2

отрицательный сигнал с входной шины 8 дешифратора передается на вход элемента 3, импульсом второй фазы положительный сигнал с элемента 3 передается на вход элемента 6, импульсом третьей фазы положительный сигнал с элемента 6 поступает на выход 13 дешифратоpa, образуя сигнал, соответствующий входной комбинации (000). Аналогично в соответствии с фиг. 1 и 2 и табл. 2 происходят преобразования последующих входных комбинаций. Эффективность изобретения заключается в упрощении устройства за счет сокращения числа логических элементов. ормула изобретения Дещифратор, содержащий троичные логические элементы, причем первая входная шина соединена с первыми входами первого, второго и третьего троичных логических элементов, второй вход первого троичного логического элемента соединен с второй входной шиной, а второй вход второго троичного элемента -. с третьей входной шиной, выходы четвертого, пятого шестого и седьмого троичных логических элемен тов соединены соответственно с первой, второй третьей и. четвертой выходными шинами, отличающийся тем, что, с целью упрощения дещифратора, второй вход третьего троичного логического элемента соединен с третьей ВХОДНОЙ шиной, выход первого троичного логического элемента соединен с первыми входами четвертого и седьмого троичных логических элементов, выход второго троичного логического элемента - с. первым и вторым входами соответственно пятого и седьмого троичных логических элементов,ВЫХОД третьего троичного логического элемента - с первым и вторым входами соответственно шестого и четвертого троичных логических элементов, вторые входы пятого и шестого троичных логических элементов соедийены с выходом первого троичного логического элемента. Источники информа1ши, принятые во внимание при экспертизе 1.Авторс кое свидетельство СССР N° 434405, кл. G 05 F 5/32, 1974. 2.Соколов Т. Н. и Васильев Ф. А. Ферритовые логические элементы и узлы информационных систем,Л., ЛВИКА им.чМожайского, 1970, с. 180, рис. 4.54 (прототип). fasai Фаза Фаза

JL

Иппипьм трехфазного чспто ника пи/пани)

Запись „ Ч Запись

С итыбание „о СиитыВание „ Снитыёание „ f

Фиг. 2 Такт 6 Такт 7 , Такт 8

Авторы

Даты

1980-04-15—Публикация

1978-10-02—Подача