1

Изобретение.относится к автоматике, вычислительной техшйсе и может быть испотйззовано в устройствах, к которым предъявляются высокие требования по надежности и помехозащищенности.

Известен реверсивный делитель чаототы, содержащий ;)СК-триггера и ритарные элементы, входы которых подключены к выходам 3 СЖ-триггеров, прямые выходы мажоритарных эле- ю ментов соединены с J -входами, а инверк тированные с К-входами ЗСК-тригт&ров ri:.,

Недостатком этого реверсивного делителя частоты является низкая надежность 15 так как он нормально функдиокирует только при одновременной подаче входных импульсов по (}ронтам, при подаче входных импульсдав со сдвигом по (J JOHTaM, что может иметь место при поступлении вход- о ных сигналов с выходов мажоритарных элементов, данная схема не обеспечивает поканального исправления ошибок за сяет сбоев в одном из каналов делителя.

Наиболее близким по технической суи ности к изобретению является резервированный делитель частоты следования ик пульсов, содержащий три канала деления, каждый из которых состоит из триггера, мажоритарного элемента, инвертора и двух элементов И, к одному входу первого из которых подключен ПРЯМОЙ выход мажоритарного элемегга, инвертированный выход которого подключен к первому входу второго элемента, на вторые входы элементов И подаяы стробирующие импульсы, а выходы первого и второго элеме1ггов И подключены соответственно к i. входам триггера, при этом выход триггера каждого канала деления подклк чен к входам вс;ех мажоритарных элементов 2.

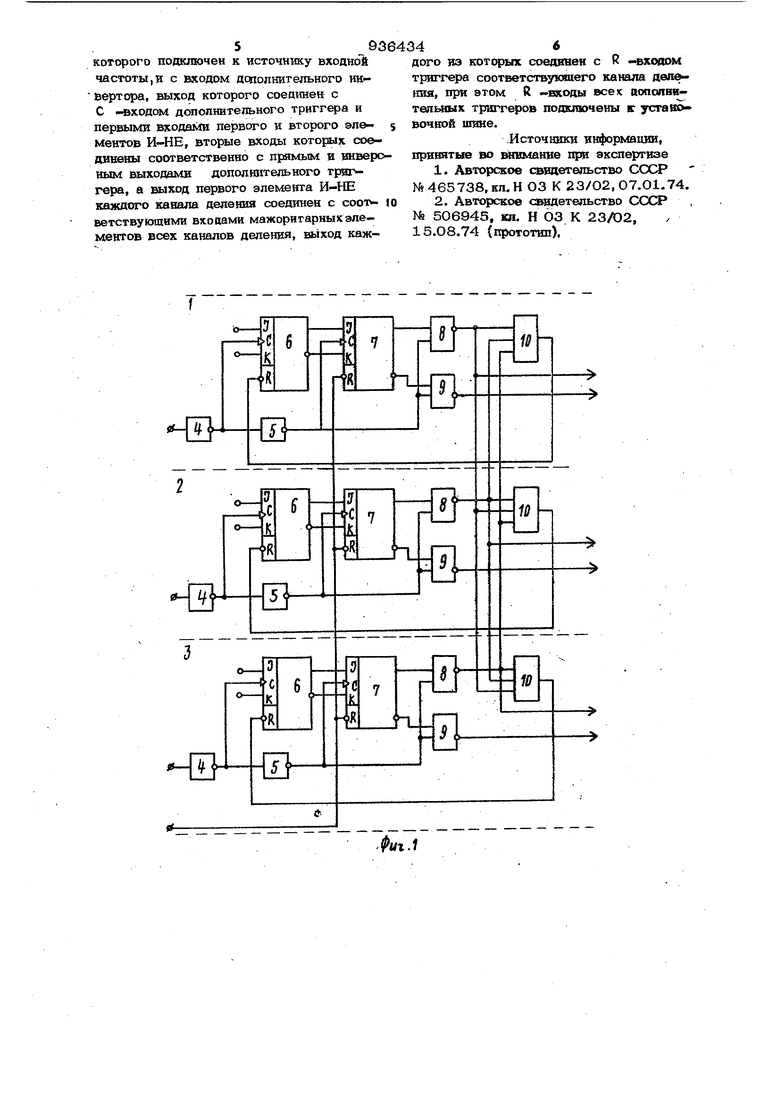

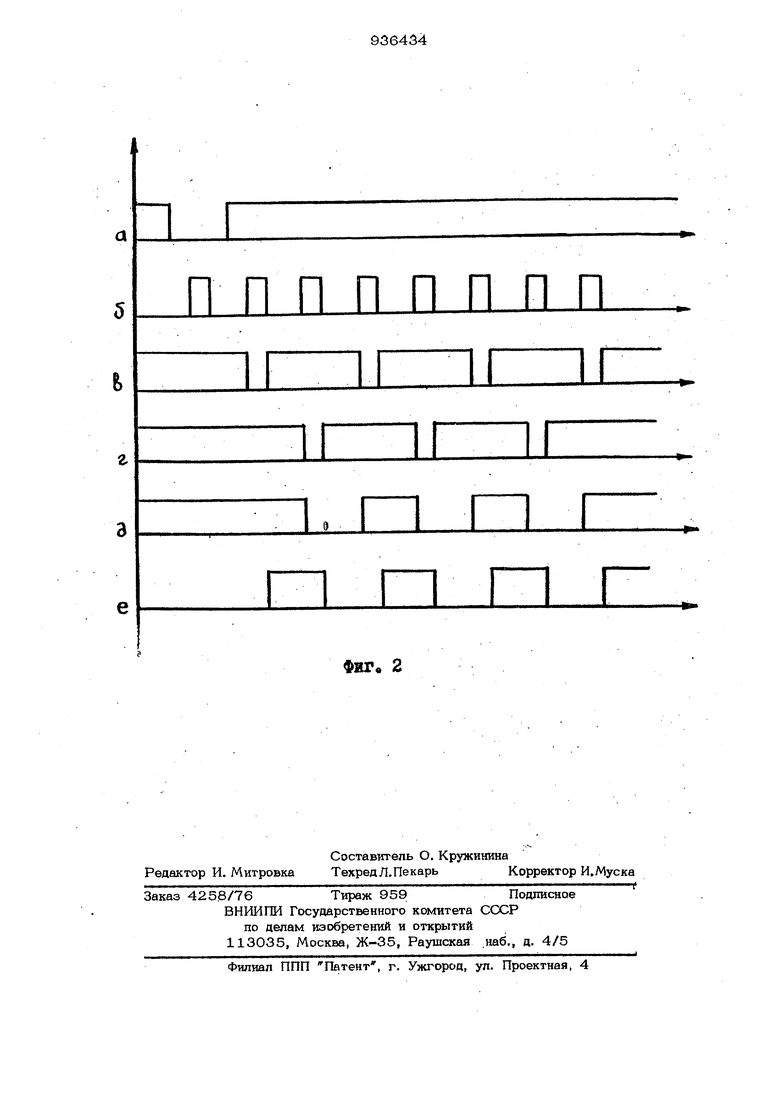

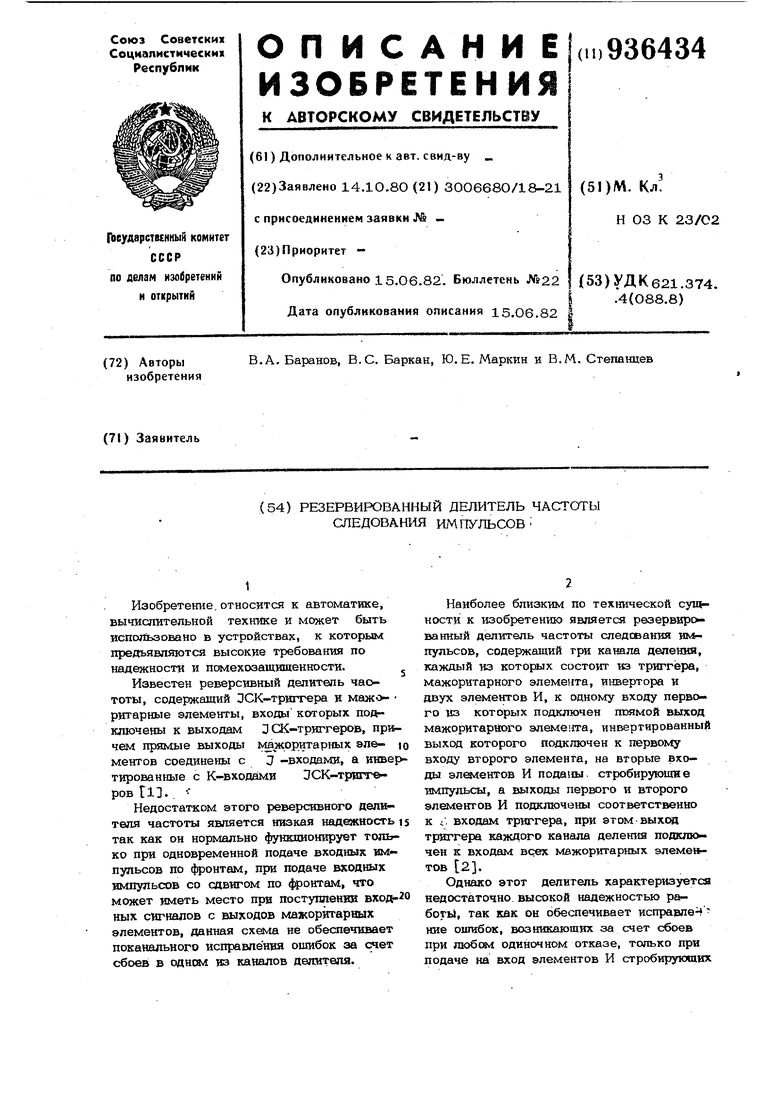

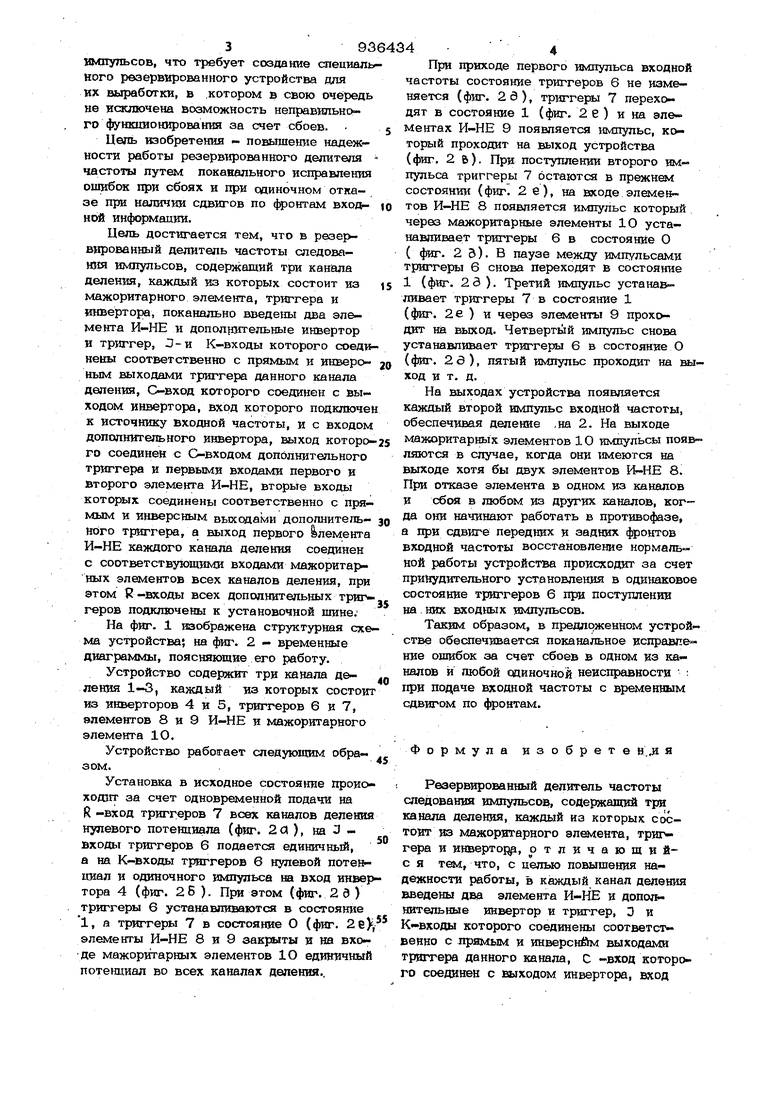

Однако этот делитель характеризуется недостаточно высокой надежностью работы, так как он обеспечивает исправле ние ошибок, возникающих за счет сбоев при любом одиночном отказе, только при подаче на вход элементов И стробирующих импульсов, что требует создание специального резервированного устройства для их выработки, в .котором в свою очередь не исключена возможность неправильного функционирования за счет сбоев. Цепь изобретения - повышение надежности работы резервированного делителя частоты путем поканального исправления ошибок при сбоях и при одиночном отказе при наличии сдвигов по ({ зонтам входной информации. Цель достигается тем, что в резерВ1фованный делитель частоты следования импульсов, содержащий три канала деления, каждый из которых состоит из мажоритарного элемента, триггера и инвертора, поканально введены два элемента И-НЕ и дополнительные инвертор и триггер. Л-и К-входы которого соединены соответственно с прямым и инвероным выходами триггера данного канала деления, С-вход которого соединен с выходом инвертора, вход которого подключен к источнику входной частоты, и с входом дополнительного инвертора, выход которсхго соединен с С-входом дополнительного триггера и первыми входами первого и второго элемента И-НЕ, вторые входы которых соединены соответственно с прямым и инверсным выходами дополнительНбго триггера, а выход первого Элемента И-НЕ каждого канала деления соединен с соответствующими входами мажоритарных элементов всех каналов деления, при этом Я-входы всех дополнительных триггеров подключены к установочной шине; На фиг. 1 изображена структурная схе ма устройства; на фиг. 2 - временные диаграммы, поясняющие его работу. Устройство содержит три канала деления 1-3, каждый из которых состоит из инверторов 4 и 5, триггеров 6 и 7, элементов 8 и 9 И-НЕ и мажоритарного элемента 1О. Устройство работает следующим образом. Установка в исходное состояние Дроио хошгг за счет одновременной подачи на R -вход триггеров 7 всех каналов деления нулевого потенциала (фиг. 20 ), на 3 входы триггеров 6 подается единичный, а на К-входы триггеров 6 нулевой потенциал и одиночного импульса на вход инвер тора 4 (фиг. 25 ). При этом (фиг. 2 Э ) триггеры 6 устанавливаются в состояние 1, а триггеры 7 в состояние О (фиг. 2еХ элементы И-НЕ 8 и 9 закрыты и на входе мажоритарных элементов 1О единичный потенциал во всех каналах деления.. При приходе первого импульса входной частоты состояние триггеров 6 не изменяется (фиг. 25), триггеры 7 переходят в состояние 1 (фиг. 2 е ) и на элементах И-НЕ 9 появляется импульс, который проходит на выход устройства (фиг. 2 6), При поступлении второго импульса триггеры 7 остаются в прежнем состоянии (фиг. 2 е), на входе элементов И-НЕ 8 появляется импульс который через мажоритарные элементы 10 устанавливает триггеры 6 в состояние О ( фиг. 2 Э). В паузе между импульсами триггеры 6 снова переходят в состояние 1 (фиг. 23 ). Третий импульс устанавливает триггеры 7 в состояние 1 (фиг. 2е ) и через элементы 9 проходит Hia выход. Четвертый импульс снова устанавливает триггеры 6 в состояние О (фиг. 2в), пятый импульс проходит на выход и т. д. На выходах устройства появляется каждый второй импульс входной частоты, обеспечивая деление ,на 2. На выходе мажоритарных элементов 10 импульсы появляются в случае, когда они имеются на выходе хотя бы двух элементов И-НЕ 8. При отказе элемента в одном из каналов И сбоя в любом из других каналов, когда они начинают работать в противофазе| а при сдвиге передних и задних фронтов входной частоты восстановление нормальной работы устройства происходит за счет принудительного установления в одинаковое состояние триггеров 6 при поступлении на них входных импульсов. Таким образом, в предложенном устройстве обеспечивается поканальное исправление ошибок за счет сбоев в одном из каналов и любой одиночной неиспрешности : при подаче входной частоты с временным сдвигом по фронтам. Формула изобрете Н.Д1 я Резервированный делитель частоты следования импульсов, содержащий три канала деления, каждый из которых состоит из мажоритарного элемента, триг гера и инвертору, ртличающийс я тем, что, с целью повышения надежности работы, в каждый канал деления введены два элемента И-НЕ и дополнительные инвертор и триггер, 3 И К-входы которого соединены соответственно с прямым и инверсн выходами триггера данного канала, С -вход которого соединен с выходом инвертора, вход которого подключен к источнику входной частоты,и с входом додопнительного ин йертора, шлход которого соединен с С -входом дополнительного триггера и первыми входами первого и второго элементов И-НЕ, вторые входы которых соединены соответственно с прямым и инвер ным выходами дополнительного трш. гера, а выход первого элемента И-НЕ каждого канала деления соединен с cooivветствующими входами мажоритарных элементов всех каналов деления, вь1ход каж94 дого из которых соединен с R -входом триггера соответствукяцего канала делекия, при этом R -входы все к пополни- тельных триггеров подключены г ycraaS вечной шине. Источники информашш, принятые во внимание при экспертизе 1.Авторское свидетельство ССОР М 4е5738,кя.НОЗ К 23/О2, 07.01,74. 2.Авторское свидетельство СССР J 506945, кл. Н 03 К 23/02, 15.О8.74 (прототип).

п п п п п п п

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированный делитель частоты следования импульсов | 1981 |

|

SU961155A1 |

| Резервированный делитель частоты следования импульсов | 1981 |

|

SU953744A1 |

| РЕЗЕРВИРОВАННЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 2022 |

|

RU2785274C1 |

| Резервированный триггерный делитель частоты | 1977 |

|

SU750743A1 |

| Резервированный делитель частоты | 1985 |

|

SU1330756A1 |

| Резервированный делитель частоты | 1978 |

|

SU731597A1 |

| МАЖОРИТАРНО-РЕЗЕРВИРОВАННЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2015617C1 |

| РЕЗЕРВИРОВАННЫЙ RS-ТРИГГЕР | 2006 |

|

RU2308147C1 |

| Резервированный делитель частоты следования импульсов | 1986 |

|

SU1367152A2 |

| Резервированный делитель частоты | 1990 |

|

SU1780187A1 |

Фвг« 2

Авторы

Даты

1982-06-15—Публикация

1980-10-14—Подача