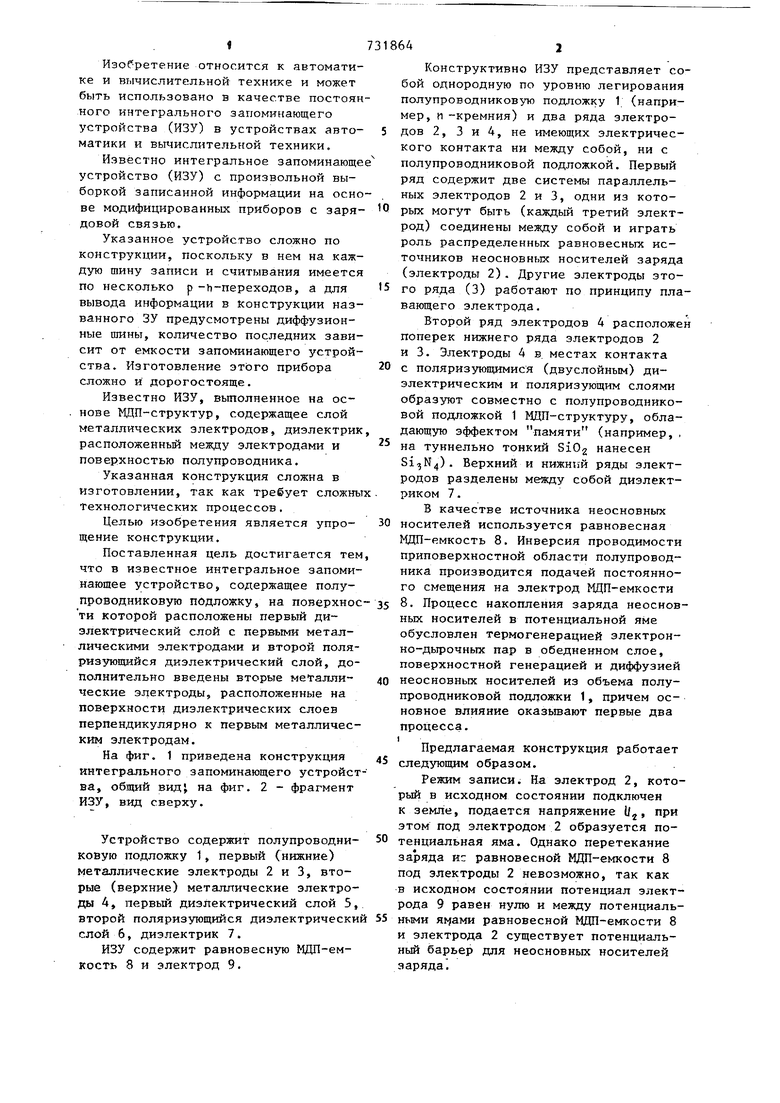

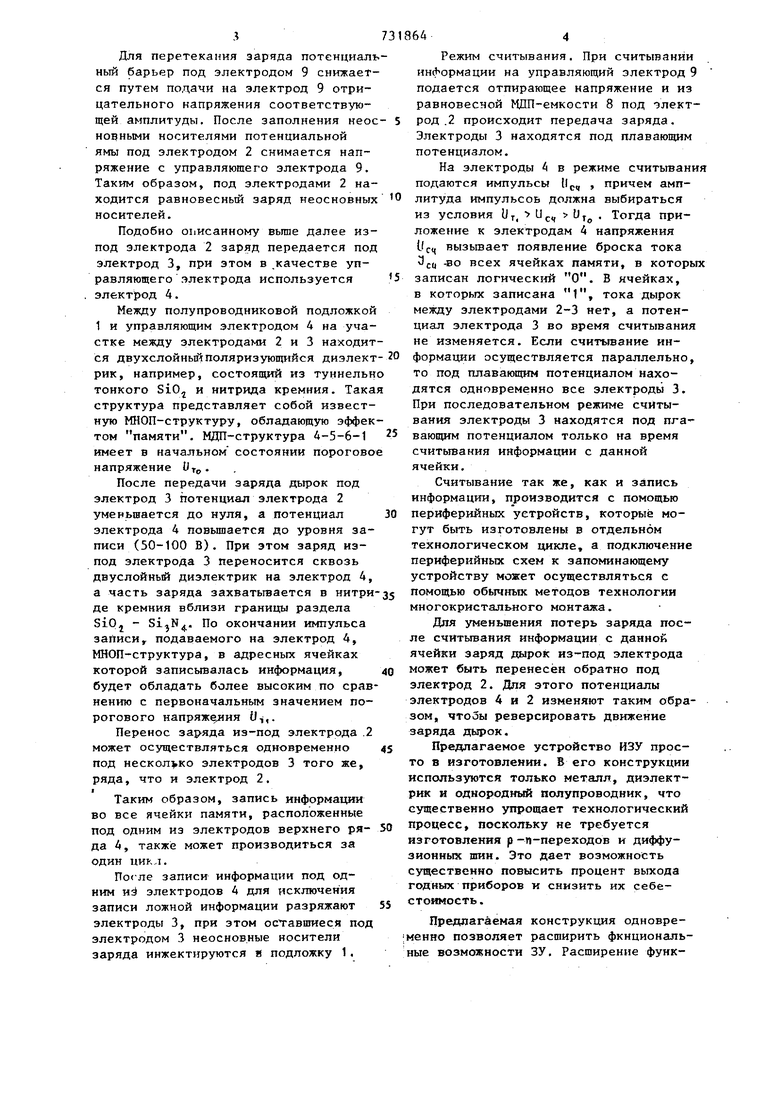

« Изобретение относится к автоматике и вычислительной технике и может быть использовано в качестве постоян ного интегрального запоминающего устройства (ИЗУ) в устройствах автоматики и вычислительной техники. Известно интегральное запоминающе устройство (ИЗУ) с произвольной выборкой записанной информации на осно ве модифицированных приборов с заря довой связью. Указанное устройство сложно по конструкции, поскольку в нем на каждую шину записи и считывания имеется по несколько р-ъ-переходов, а для вывода информации в Конструкции названного ЗУ предусмотрены диффузионные шины, количество последних зави сит от емкости запоминающего устрой ства. Изготовление этого прибора сложно и дорогостояще. Известно ИЗУ, вьтолненное на основе МДП-структур, содержащее слой металлических электродов, диэлектрик расположенньй между электродами и поверхностью полупроводника. Указанная конструкция сложна в изготовлении, так как требует сложны Технологических процессов, Целью изобретения является упрощение конструкции. Поставленная цель достигается те что в известное интегральное запоми наюшее устройство, содержащее полупроводниковую подложку, на понерхнос- 35 ти которой расположены первый диэлектрический слой с первыми металлическими электродами и второй поляризующийся диэлектрический слой, дополнительно введены вторые металли- 40 ческие электроды, расположенные на поверхности диэлектрических слоев перпендикулярно к первым металлическим электродам. На фиг. 1 приведена конструкция 45 интегрального запоминающего устройства, общий вид на фиг. 2 - фрагмент ИЗУ, в:ид сверху. Устройство содержит полупроводни- 50 ковую подложку 1, первый (нижние) металлические электроды 2 и 3, вторые (верхние) металлические электроды 4, первый диэлектрический слой 5, второй поляризующийся диэлектрический55 слой 6, диэлектрик 7. ИЗУ содержит равновесную МДП-емкость 8 и электрод 9. 4 Конструктивно ИЗУ представляет собой однородную по уровню легирования полупроводниковую подложку 1 (например, и-кремния) и два ряда электродов 2, 3 и 4, не имеющих электрического контакта ни между собой, ни с полупроводниковой подложкой. Первый ряд содержит две системы параллельных электродов 2 и 3, одни из которых могут быть (каждый третий электрод) соединены между собой и играть роль распределенных равновесных источников неосновных носителей заряда (электроды 2). Другие электроды этого ряда (3) работают по принципу плавающего электрода. Второй ряд электродов 4 расположен поперек нижнего ряда электродов 2 и 3. Электроды 4 в. местах контакта с поляризующимися (двуслойным) диэлектрическим и поляризующим слоями образзпот совместно с полупроводниковой подложкой 1 МДП-структуру, обладающую эффектом памяти (например, , на туннельно тонкий SiOg нанесен ). Верхний и нижнтш ряды электродов разделены между собой диэлектриком 7. В качестве источника неосновных носителей используется равновесная МДП-емкость 8. Инверсия проводимости приповерхностной области полупроводника производится подачей постоянного смещения на электрод МДП-емкости 8. Процесс накопления заряда неосновных носителей в потенциальной яме обусловлен термогенерацией электронно-дырочных пар в обедненном слое, поверхностной генерацией и диффузией неосновных носителей из объема полупроводниковой подложки 1, причем основное влияние оказьтают первые два процесса. I Предлагаемая конструкция работает следующим образом. Режим записи. На электрод 2, который в исходном состоянии подключен к земле, подается напряжение Ц, при этом под электродом 2 образуется потенциальная яма. Однако перетекание заряда ис равновесной МДП-емкостн В под электроды 2 невозможно, так как в исходном состоянии потенциал электрода 9 равен нулю и между потенциальньми равновесной МДП-емкости 8 и электрода 2 существует потенциальный барьер для неосновных носителей заряда. Для перетекания заряда потенциал ный барьер под электродом 9 снижает ся путем подачи на электрод 9 отрицательного напряжения соответствующей амплитуды. После заполнения нео новными носителями потенциальной ямы под электродом 2 снимается напряжение с управляющего электрода 9. Таким образом, под электродами 2 на ходится равновесньш заряд неосновных носителей. Подобно описанному выше далее из под электрода 2 заряд передается под электрод 3, при этом в .качестве управляющего электрода используется электрод 4. Между полупроводниковой подложкой 1 и управляющим электродом 4 на участке между электродами 2 и 3 находит ся двухслойньйполяризующийся диэлект рик, например, состоящий из туннельн тонкого SiO и нитрида кремния. Така структура представляет собой известную МНОП-структуру, обладающую эффек том памяти. МДП-структура 4-5-6-1 имеет в начальном состоянии порогово напряжение Чго После передачи заряда дырок под электрод 3 потенциал электрода 2 уменьшается до нуля, а потенциал электрода 4 повышается до уровня записи (50-100 В). При этом заряд изпод электрода 3 переносится сквозь двуслойный диэлектрик на электрод 4, а часть заряда захватьгаается в нитри де кремния вблизи границы раздела SiQj - . По окончании импульса записи,, подаваемого на электрод 4, МНОП-структура, в адресных ячейках которой записывалась информация, будет обладать более высоким по срав нению с первоначальным значением порогового напряж ия Hi,. Перенос заряда из-под электрода .2 может осуществляться одновременно под нескол ко электродов 3 того же, ряда, что и электрод 2. I Таким образом, запись инфррмащт во все ячейки памяти, расположенные под одним из электродов верхнего ряда 4, также может производиться за один цикл. После записи информации под одним и электродов 4 для исключения записи ложной информации разряжают электроды 3, при этом оставшиеся под электродом 3 неосновные носители заряда инжектируются я подложку 1. Режим считывания. При считывании информации на управляющий электрод 9 подается отпирающее напряжение и из равновесной МДП-емкости 8 под электрод .2 происходит передача заряда. Электроды 3 находятся под плавающим потенциалом. На электроды 4 в режиме считьгоания подаются импульсы U причем амплитуда импульсов должна выбираться условия UT, Uj. Uj . Тогда приложение к электродам 4 напряжения О броска тока вызывает появление У си -so всех ячейках памяти, в которых записан логический О. В ячейках, в которых записана 1, тока дырок между электродами 2-3 нет, а потенциал электрода 3 во время считывания не изменяется. Если считывание информации осуществляется параллельно, то под плавающим потенциалом находятся одновременно все электроды 3. При последовательном режиме считывания электроды 3 находятся под пга вающим потенциалом только на время считьшания информации с данной ячейки. Считывание так же, как и запись информации, производится с помощью периферийных устройств, которые могут быть изготовлены в отдельном технологическом цикле, а подключение периферийных схем к запоминающему устройству может осуществляться с помощью обычных методов технологии многокристального монтажа. Для уменьшения потерь заряда после считывания информации с данной ячейки заряд дырок из-под электрода может быть перенесён обратно под электрод 2. Для этого потенциалы электродов 4 и 2 изменяют таким образом, чтооы реверсировать движение заряда дырок. Предлагаемое устройство ИЗУ просто 8 изготовлении. В его конструкции используются только металл, диэлектрик и однородный полупроводник, что существенно упрощает технологический процесс, поскольку не требуется изготовления р-п-переходов и диффуионных шин. Это дает возможность существенно повысить процент выхода годных приборов и снизить их себетоимость . Предлагаемая конструкция одновреенно позволяет расширить фкнциональые возможности ЗУ, Расширение функциойал;ьньгх возможностей состоит в том, что предлагаемое устройство обладает постоянной памятью. Размер элементарной ячейки памяти предлагаемого ЗУ при существующем уровне технологии может составить 24-32 мкм, что позволяет получать плотность упаковки 1,3-10 бит прибли- зительно в 2 раза превьшает плотность

упаковки современных интегральных

ПЗУ.

Предлагаемая матрица потребляет мало энергии ( 1-3 мкВ, т/бит) и поэтому найдет широкое распространение в различных областях автоматики и вычислительной техники в качестве постоянного запоминающего устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗГОТОВЛЕНИЯ МОНОП-ЯЧЕЙКИ ПАМЯТИ, ЯЧЕЙКА ПАМЯТИ И МАТРИЧНЫЙ НАКОПИТЕЛЬ НА ЕЕ ОСНОВЕ | 1996 |

|

RU2105383C1 |

| Элемент памяти | 1976 |

|

SU628536A1 |

| СПОСОБ УПРАВЛЕНИЯ РАБОТОЙ МЕМРИСТИВНОЙ КОНДЕНСАТОРНОЙ СТРУКТУРЫ МЕТАЛЛ-ДИЭЛЕКТРИК-ПОЛУПРОВОДНИК | 2018 |

|

RU2706197C1 |

| ЭЛЕМЕНТ ПАМЯТИ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1981 |

|

SU1012704A1 |

| Матрица приборов с зарядовой связью | 1978 |

|

SU719408A2 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО И СПОСОБ УПРАВЛЕНИЯ ИМ | 1979 |

|

RU1110315C |

| Ячейка памяти | 1978 |

|

SU752476A1 |

| Способ записи оптической информации в двухзатворной МДП- @ - @ -структуре с диэлектриком с захватом заряда | 1984 |

|

SU1170509A1 |

| Координатно-чувствительный фоторезистор (его варианты) | 1982 |

|

SU1104607A1 |

| Накопитель информации для оптоэлектронного запоминающего устройства | 1981 |

|

SU995125A1 |

ИНТЕГРАЛЬНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее полупроводниковую подложку, на поверхности которой расположены первый диэлектрический слой с первыми мета)тлическими электродами и второй поляриэующийся диэлектрический слой,о т л и ч а ющ е е с я тем, что,с целью упрощения устройства, оно содержит вторые металлические электроды, расположенные на поверхностях диэлектрических сло.;в перпендикулярно первым металлическим электродам. (Л 00 00 .

8 I

Фиг.2

| Старое Ф.Г | |||

| и др | |||

| Полупроводниковые интегральные, запоминающие устройства | |||

| Л | |||

| Энергия, 1973, с | |||

| Пюпитр для работы на пишущих машинах | 1922 |

|

SU86A1 |

| IEEE Journal of Solid State Cirquit, 1972, c | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Катодная трубка Брауна | 1922 |

|

SU330A1 |

Авторы

Даты

1986-08-30—Публикация

1976-05-04—Подача