(54) ЯЧЕЙКА ПАМЯТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегральное запоминающее устройство | 1976 |

|

SU731864A1 |

| Матрица приборов с зарядовой связью | 1974 |

|

SU533090A1 |

| Матрица приборов с зарядовой связью | 1978 |

|

SU719408A2 |

| УСТРОЙСТВО СЧИТЫВАНИЯ НА ПРИБОРАХ С ЗАРЯДОВОЙ СВЯЗЬЮ ДЛЯ ДВУМЕРНЫХ ПРИЕМНИКОВ ИЗОБРАЖЕНИЯ | 1993 |

|

RU2054753C1 |

| Способ изготовления матричного накопителя для постоянного запоминающего устройства | 1989 |

|

SU1607621A1 |

| Матричный накопитель для запоминающего устройства | 1986 |

|

SU1361628A1 |

| Способ изготовления интегральных схем памяти на основе МНОП-транзисторов | 1982 |

|

SU1040978A1 |

| Фазометр с масштабно-временным преобразованием | 1987 |

|

SU1422180A1 |

| Ячейка оперативной памяти | 2024 |

|

RU2826859C1 |

| Элемент памяти для постоянного запоминающего устройства | 1984 |

|

SU1159447A1 |

Изобретение относится к микроэлектронике и может быть использовано для создания полупроводниковых запоминающих устройств ( ЗУ) как оперативных, так и электрически перепрограммируемых постоянных запоминающих устройств (ППЗУ) . Известны ячейки ППЗУ с произвольной выборкой, представляющие собой р-канальный МНОП-транзистор, состоящий из слабо легированной кремниевой подложки п-типа, двух расположенных в приповерхностном слое подложки на некотором расстоянии друг от друга сильно легированных областей р-типа (сток и исток), являющихся диффузионными шинами (разрядная шина и шина питания) и последовательно на несенных на подложку слоев двуокиси кремния, нитрида кремния и металлического слоя, являющегося затвором 11 и 2 . В другой ячейке памяти -используется сочетание ПЗС сдвигового регистра и запоминающего МНОП-конденсатора, в котором после каждого третьего ПЗС-элемента расположен МНОП-конденсатор. Здесь на кремниевую .подложку п-типа последовательно нанесены слои двуокиси кремния переменной толщины (в области ПЗС-злемента толщина слоя составляет 500 А ,а в области МНОП-конденсатора - 20 А ) и нитрида кремния толщиной 500 А , на слое нитрида кремния расположены алюминиевые электроды, служащие затворами ПЗС-элемента и МНОП-конденсатора З . Недостатком описанных конструкций является большая площадь ячейки и отсутствие произвольной выборки из ЗУ на основе данной ячейки. Наиболее близким к изобретению техническим решением является ячейка памяти, содержащая полупроводниковую подложку с V-образными параллельными канавками, расположенными в приповерхностном слое полупроводниковой подложки до соединения с легированными диффузионными областями внутри полупроводниковой подложки, противоположного ей типа проводимости, первый слой диэлектрика на поверхности которого в V-образных параллельных канавках размещены тактовые шины, на поверхности которых и первого слоя диэлектрика расположен второй защитный слой диэлектрика. Кроме того, в полупроводниковой подложке размещены также разрядные диффузионные шины 4 .

Недостатком этой ячейки является только оперативный режим работы и трудность стирания информации в режиме ППЗУ.

Цель изобретения - повышение степени интеграции ячейки памяти и-обеспечение произвольной выборки в сочетании с последовательной выборкой и электрическим стиранием информации. Поставленная цель достигается тем, что в ячейку памяти введены шины выборки, расположенные на втором слое диэлектрика перпендикулярно тактовым шинам, и образующие с полупроводниковой подложкой между тактовыми шинами МНОП-конденсаторы,

И тем, что легированные диффузионные области выполнены одинаково с полупроводниковой подложкой типа проводимости и с концентрацией примеси не менее, чем в 10 раз превышающей концентрацию примеси в полупроводниковой подложке.

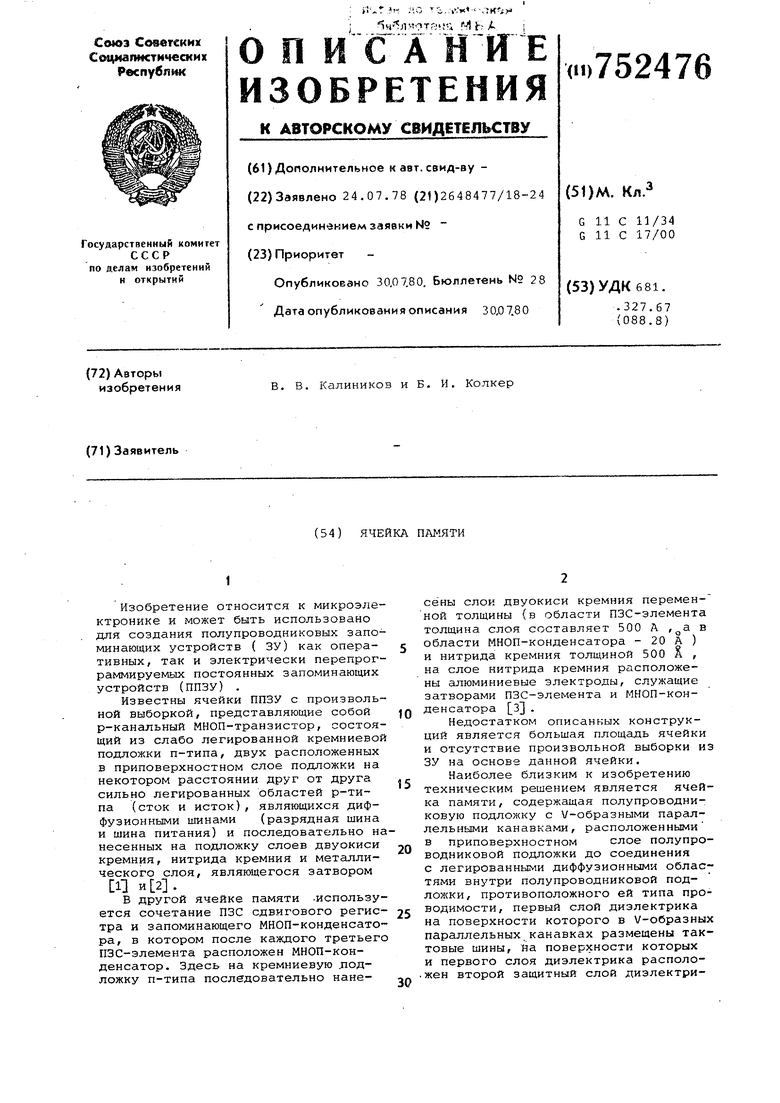

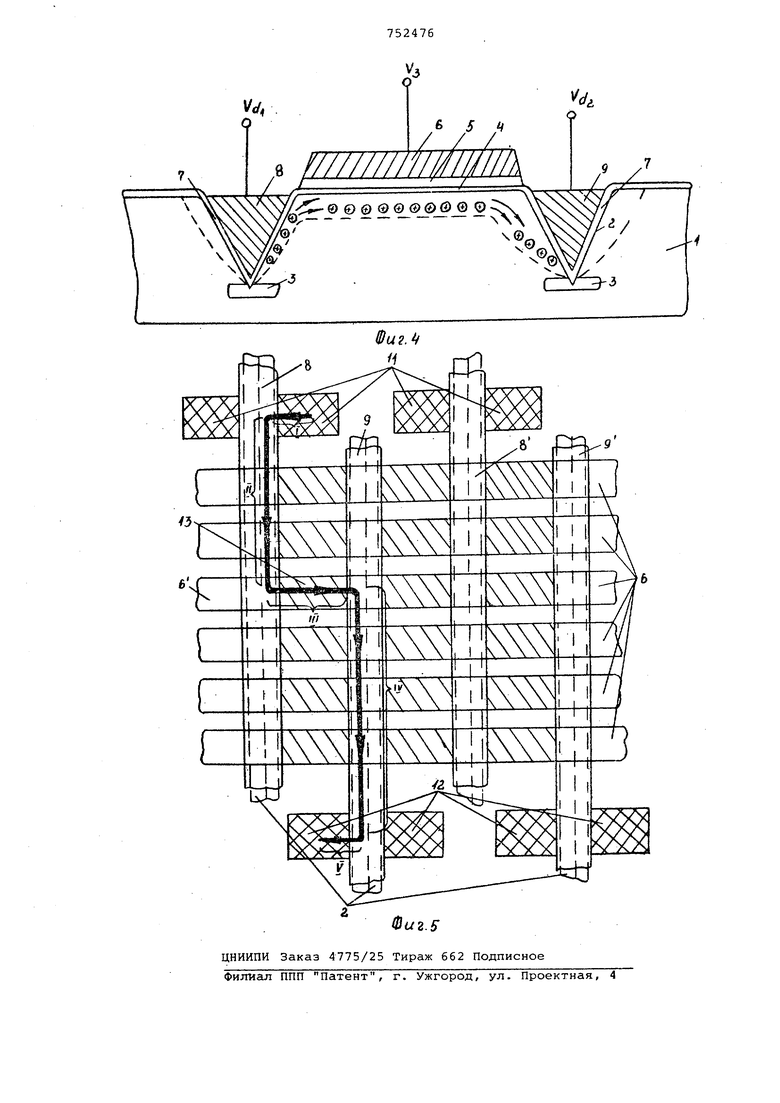

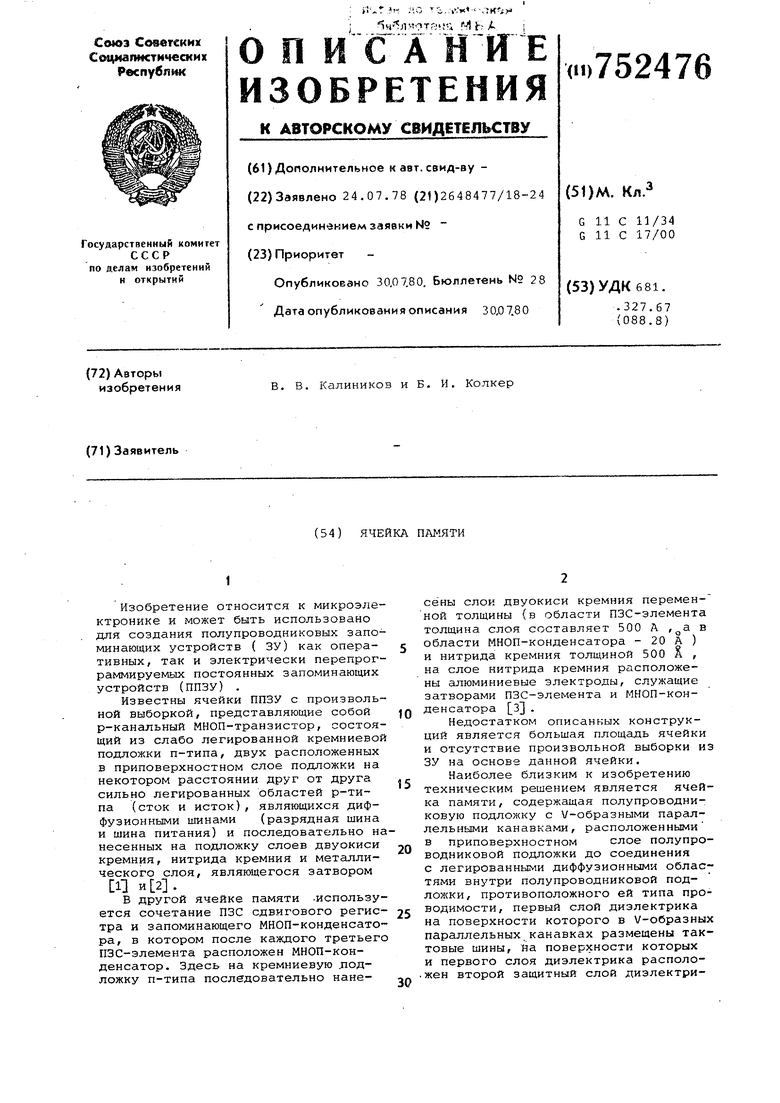

На фиг. 1 показана предлагаемая ячейка памяти; на фиг. 2 - перенос заряда в ПЗС-элементе; на фиг. 3 и 4пояснение работы ячейки при записи- и считывании информации, соответственно; на фиг. 5 - возможная конструкция матрицы памяти.

В полупроводниковой подложке 1 выполнены V-канавки 2, дно которых находится в контакте с диффузионными областями 3, выполненными в подложке и совпадающими с ней по типу проводимости. В промежутках между V-канавками расположены элементы запоминающего МНОП-конденсатора : диэлектрические слои 4 SiO - толщиной 2050 А и Si 2,4 - 5 толщиной 600-1000 А и АЕ шины 6 выборки.

На боковых гранях V-канавок, примыкающих к запоминающему конденсатору, последовательно расположены элементы ПЗС структуры, включающей подзатворный окисел 7 из SiOj толщиной 1000-1200 А, совпадающий с диэлектрическим слоем 4 запоминающего конденсатора, и тактовые электроды 8 и 9 из поликремния, изолированного от электрода МНОП-конденсатора окислом 10. Области 3 служат для увеличения порогового напряжения участка о ПЗС-элемента, расположенного в углублении V-канавки. Концентрация примес в области не менее, чем в 10 ра превышает концентрацию примеси в подложке, что обеспечивает пороговое напряжение на указанном участке больше чем максимальное рабочее напряжение на ПЗС-электроде.

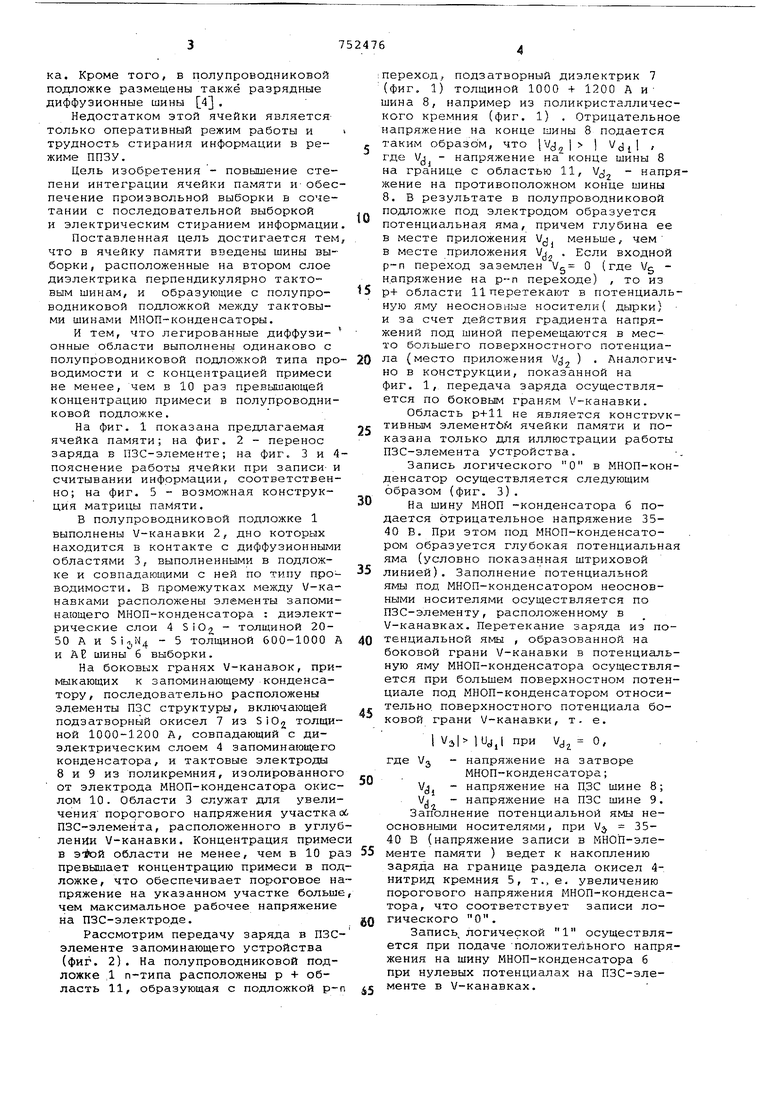

Рассмотрим передачу заряда в ПЗСэлементе запоминающего устройства (фиг. 2). На полупроводниковой подложке ,1 п-типа расположены р + область 11, образующая с подложкой р-п

:переход, подзатворный диэлектрик 7 (фиг, 1) толщиной 1000 + 1200 А н шина 8, например из поликристаллического кремния (фиг. 1) . Отрицательное напряжение на конце шины 8 подается таким образом, что iVj, I dil где Vjj - напряжение на конце шины 8 на границе с областью 11, V напряжение на противоположном конце шины В. В результате в полупроводниковой подложке под электродом образуется потенциальная яма, причем глубина ее в месте приложения V меньше, чем в месте приложения Vj . Если входной р-п переход заземлен / О (где Vg напряжение на р-п переходе) , то из р+ области 11 перетекают в потенциальную яму неосновные носители( дырки) и за счет действия градиента напряжений под шиной перемещаются в место большего поверхностного потенциа0 -ла (место приложения М, ) . Аналогично в конструкции, показанной на фиг. 1, передача заряда осуществляется по боковьа1 граням V-канавки.

Область р+11 не является конструктивным элементбм ячейки памяти и показана только для иллюстрации работы ПЗС-элемента устройства.

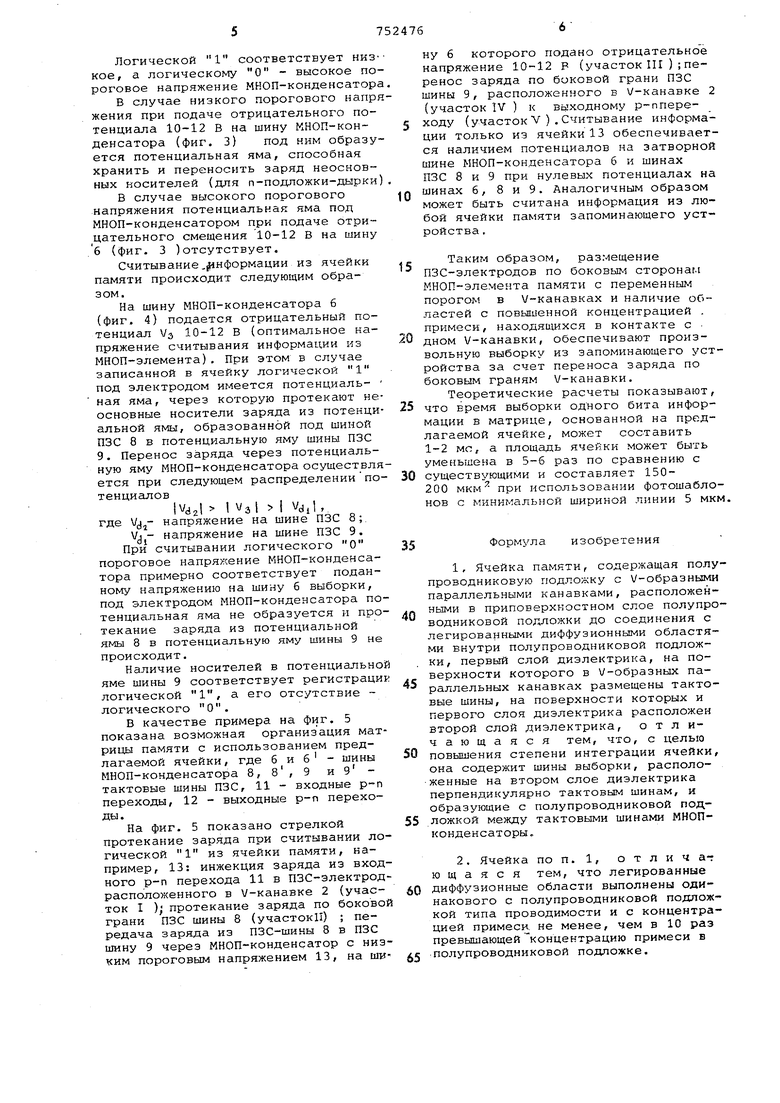

Запись логического О в МНОП-конденсатор осуществляется следующим образом (фиг. 3).

На шину МНОП -конденсатора 6 подается отрицательное напряжение 3540 В. При этом под МНОП-конденсатором образуется глубокая потенциальная яма (условно показанная штриховой линией). Заполнение потенциальной ямы под МНОП-конденсатором неосновными носителями осуществляется по ПЗС-элементу, расположенному в V-канавках. Перетекание заряда из потенциальной ямы , образованной на боковой грани V-канавки в потенциальную яму МНОП-конденсатора осуществляется при большем поверхностном потенциале под МНОП-конденсатором относительно, поверхностного потенциала боковой грани V-канавки, т. е.

I з| lUjJ при Vj О,

где Vj - напряжение на затворе МНОП-конденсатора; напряжение на ПЗС шине 8;

Vd, напряжение на ПЗС шине 9. А, ЗаЪюлнение потенциальной ямы неосновными носителями, при М 3540 В (напряжение записи в МНОП-элементе памяти ) ведет к накоплению заряда на границе раздела окисел 4нитрид кремния 5, т.,е. увеличению порогового напряжения МНОП-конденсатора, что соответствует записи лоQ гического О.

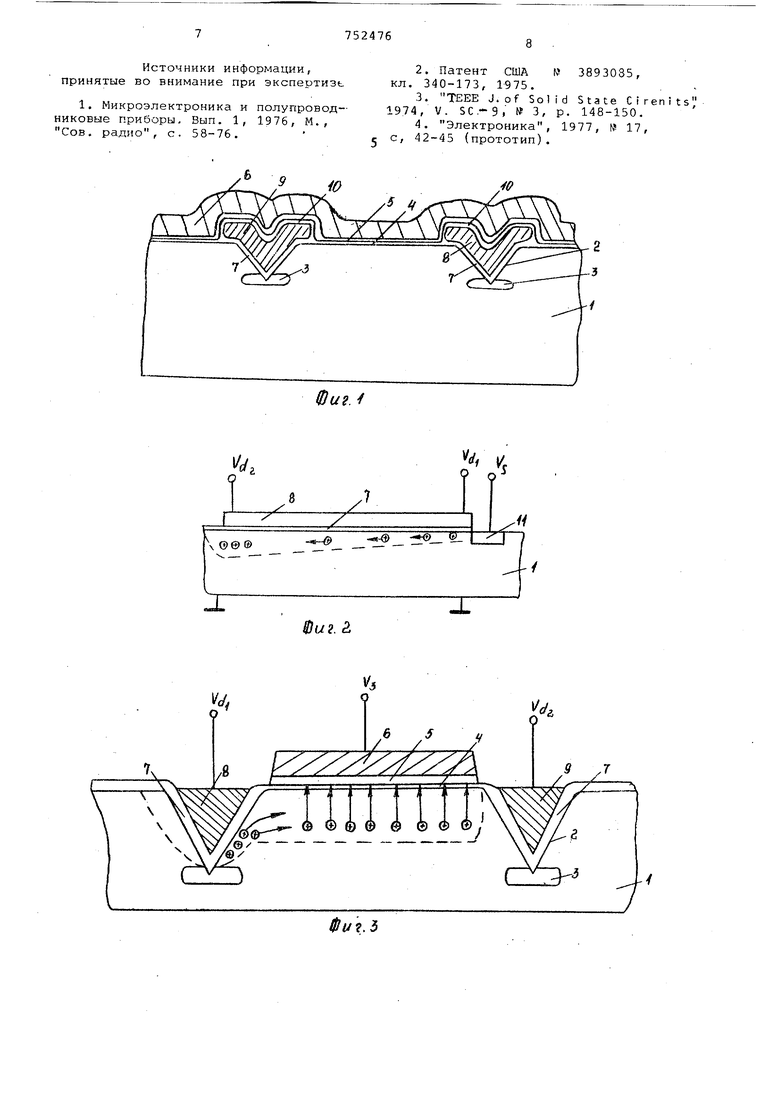

Запись, логической 1 осуществляется при подаче положительного напряжения на шину МНОП-конденсатора 6 при нулевых потенциалах на ПЗС-эле5 менте в V-канавках. Логической 1 соответствует низ кое, а логическому О - высокое по роговое напряжение МНОП-конденсатор В случае низкого порогового напр жения при подаче отрицательного потенциала 10-12 В на шину КНОП-конденсатора (фиг. 3) под ним образу ется потенциальная яма, способная хранить и переносить заряд неосновных носителей (для п-подложки-дырки В случае высокого порогового напряжения потенциальная яма под МНОП-конденсатором при подаче отри цательного смещения 10-12 В на шину б (фиг. 3 )отсутствует. Считывание,информации из ячейки памяти происходит следующим образом. На шину МНОП-конденсатора 6 (фиг. 4) подается отрицательный потенциал УЗ 10-12 В (оптимальное напряжение считывания информации из МНОП-элемента). При этом в случае записанной в ячейку логической 1 под электродом имеется потенциальная яма, через которую протекают не основные носители заряда из потенци альной ямы, образованной под шиной ПЗС 8 в потенциальную яму шины ПЗС 9. Перенос заряда через потенциальную яму МНОП-конденсатора осуществля ется при следующем распределениипо тенциалов tVd 1 Val I VdJ, где Vjj- напряжение на шине ПЗС 8; Vj - напряжение на шине ПЗС 9. При считывании логического О пороговое напряжение МНОП-конденсатора примерно соответствует поданному напряжению на шину б выборки, под электродом МНОП-конденсатора по тенциальная яма не образуется и про текание заряда из потенциальной ямы 8 в потенциальную яму шины 9 не происходит. Наличие носителей в потенциально яме шины 9 соответствует регистраци логической 1, а его отсутствие логического О. Б качестве примера на фиг. 5 показана возможная организация матрицы памяти с использованием предлагаемой ячейки, где 6 и б - шины МНОП-конденсатора 8, 8 , 9 и 9 тактовые шины ПЗС, 11 - входные р-п переходы, 12 - выходные р-п переходы. На фиг. 5 показано стрелкой протекание заряда при считывании лоиз ячейки памяти, нагическойпример, 13: инжекция заряда из входного р-п перехода 11 в ПЗС-электрод расположенного в V-канавке 2 (участок I ); протекание заряда по боковой грани ПЗС шины 8 (участок) ; передача заряда из ПЗС-шины 8 в ПЗС шину 9 через МНОП-конденсатор с низким пороговым напряжением 13, на ши ну 6 которого подано отрицательной напряжение 10-12 Р (участок III );перенос заряда по боковой грани ПЗС шины 9, расположенного в V-канавке 2 (участок IV ) к выходному р-ппереходу (участок V).Считывание информации только из ячейки 13 обеспечивается наличием потенциалов на затворной шине МНОП-конденсатора б и шинах ПЗС 8 и 9 при нулевых потенциалах на шинах б, 8 и 9. Аналогичным образом может быть считана информация из любой ячейки памяти запоминающего устройства . Таким образом, размещение ПЗС-электродов по бoкoвы - сторонам МНОП-элемента памяти с переменным порогом в V-канавках и наличие областей с повышенной концентрацией . примеси, находящихся в контакте с дном V-канавки, обеспечивают произвольную выборку из запоминающего устройства за счет переноса заряда по боковым граням V-канавки. Теоретические расчеты показывают, что время выборки одного бита информации в матрице, основанной на предлагаемой ячейке, может составить 1-2 мс, а площадь ячейки может быть уменьшена в 5-6 раз по сравнению с существующими и составляет 150200 мкм при использовании фотошаблонов с минимально шириной линии 5 мкм. Формула изобретения 1,Ячейка памяти, содержащая полупроводниковую подложку с V-образными параллельными канавками, расположенными в приповерхностном слое полупроводниковой подложки до соединения с легированными диффузионными областями внутри полупроводниковой подложки, первый слой диэлектрика, на поверхности которого в V-образных параллельных канавках размещены тактовые шины, на поверхности которых и первого слоя диэлектрика расположен второй слой диэлектрика, отличающаяся тем, что, с целью повышения степени интеграции ячейки, она содержит шины выборки, расположенные на втором слое диэлектрика перпендикулярно тактовым шинам, и образующие с полупроводниковой подложкой между тактовыми шинами МНОПконденсаторы. 2.Ячейка по п. 1, о т л и ч а-: ю щ а я с я тем, что легированные диффузионные области выполнены одинакового с полупроводниковой подложкой типа проводимости и с концентрацией примеси не менее, чем в 10 раз превышающей концентрацию примеси в полупроводниковой подложке.

Источники информации, принятые во внимание при экспертизь

ug.-f

1/.

1

Z

©@© ,

S)u.2.

Фич.Ъ

У

Ч V,

о S

11

Авторы

Даты

1980-07-30—Публикация

1978-07-24—Подача