подложки под нимчгг величины захваченного эарйДа.

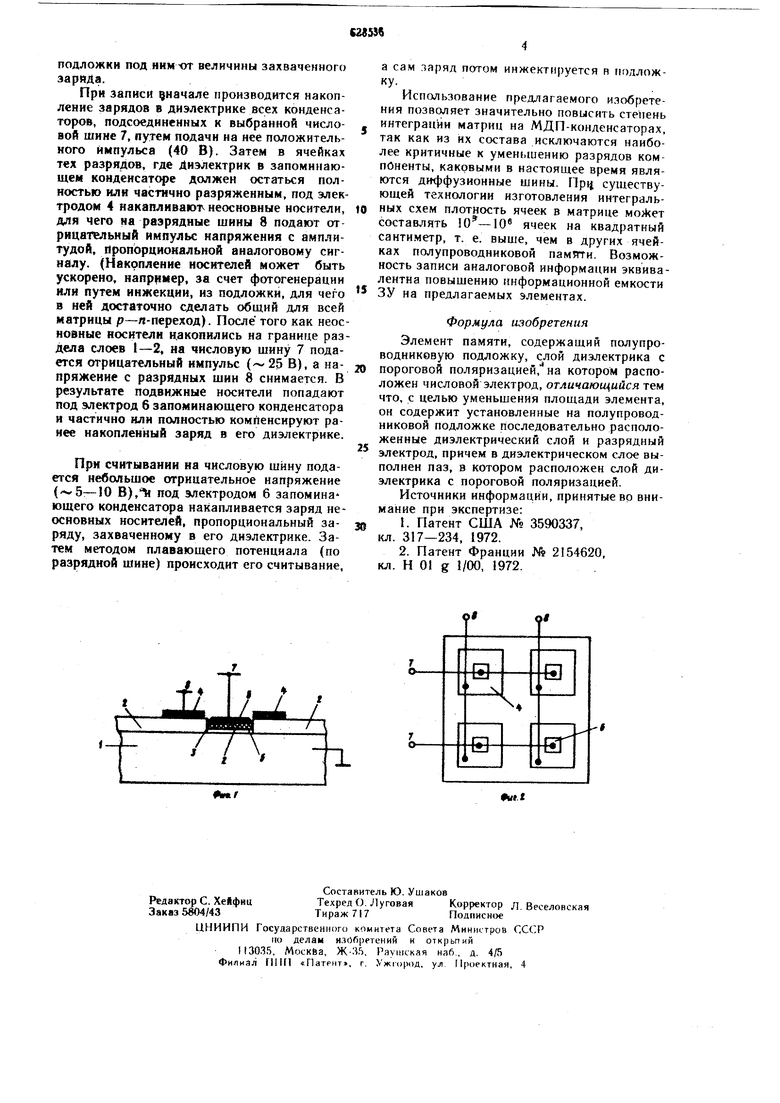

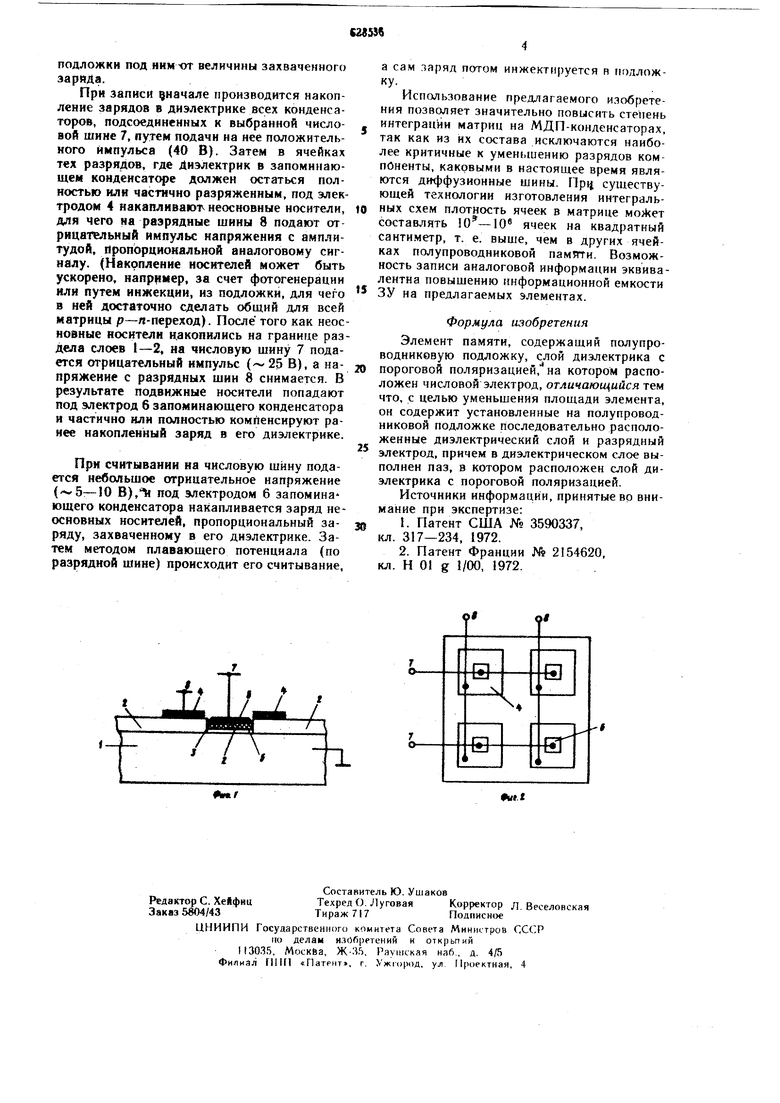

При записи начале производится накопление зарядов в диэлектрике всех конденсаторов, подсоединенных к выбранной числовой шине 7, путем подачи на нее положительного импульса (40 В). Затем в ячейках тех разрядов, где Диэлектрик в запоминающем конденсаторе должен остаться полностью или частично разряженным, под электродом 4 накапливают неосновные носители, для чего на разрядные шины 8 подают отрицательный импульс напряжения с амплитудой, пропорциональной аналоговому сигналу. (Накопление носителей может быть ускорено, например, за счет фотогенерации или путем инжекции, из подложки, для чего в ней достаточно сделать общий для всей матрицы р-я-переход). После того как неосновные носители накопились на границе разДела слоев I-2, на числовую шину 7 подается отрицательный импульс ( 25 В), а напряжение с разрядных шин 8 снимается. В результате подвижные носители попадают под электрод 6 запоминающего конденсатора и частично или полностью компенсируют ранее накопленный заряд в его диэлектрике.

При считывании на числовую шину подается небольшое отрицательное напряжение ( В), под электродом 6 запомина ющего конденсатора накапливается заряд неосновных носителей, пропорциональный заряду, захваченному в его диэлектрике. Затем методом плавающего потенциала (по разрядной шнне) происходит его считывание,

а сам заряд потом инжектируется R подложку.

Использование предлагаемого изобретения позвсхляет значительно повысить степень

интеграции матриц иа МДП-кондеисаторах, так как из их состава исключаются наиболее критичные к уменьшению разрядов компоненты, каковыми в настоящее время являются диффузионные шины. Прц, существующей технологии изготовления интегральных схем плотность ячеек в матрице моАет составлять ячеек на квадратный сантиметр, т. е. выше, чем в других ячейках полупроводниковой памяти. Возможность записи аналоговой информации эквивалентна повышению информационной емкости

ЗУ на предлагаемых элементах.

Формула изобретения

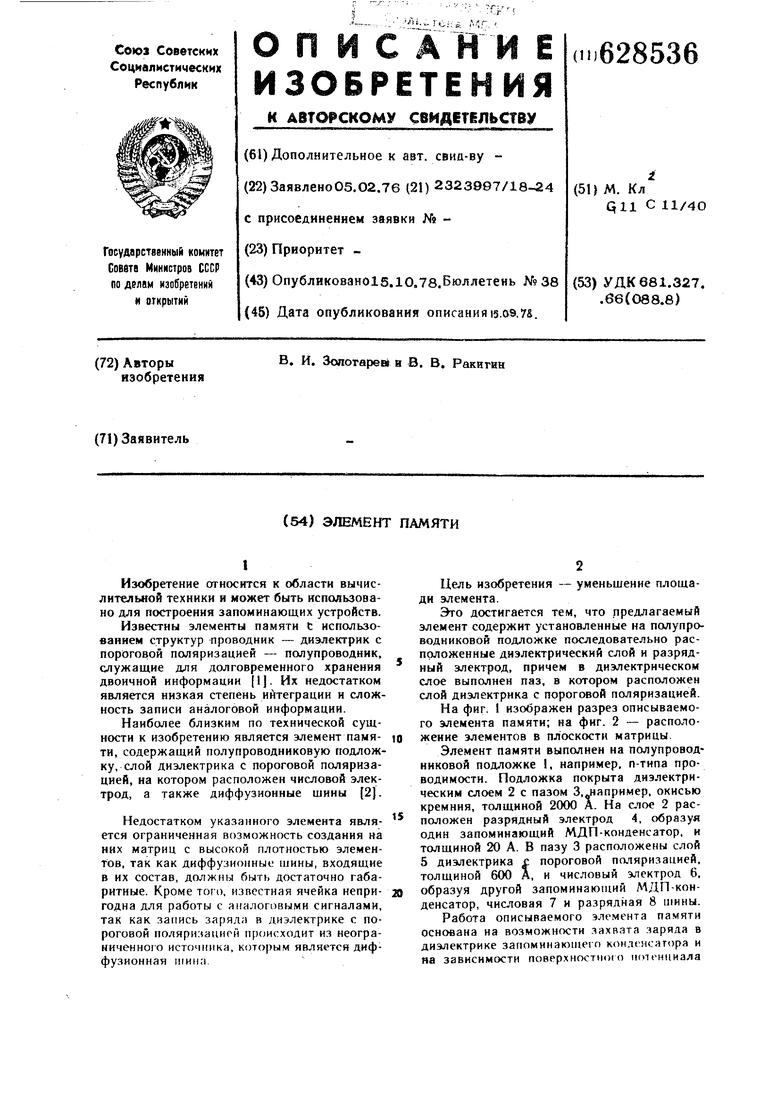

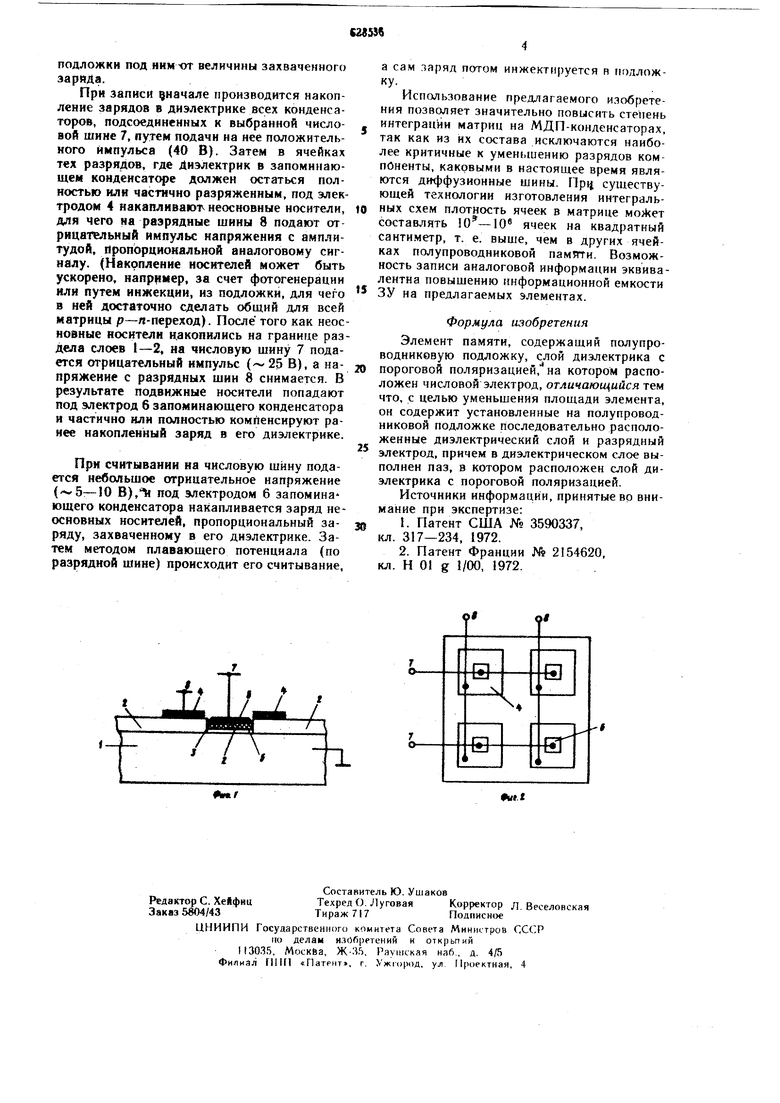

Элемент памяти, содержащий полупроводниковую подложку, слой диэлектрика с пороговой поляризацией, на котором расположен числовой электрод, отличающийся тем что, с целью уменьшения площади элемента, он содержит установленные иа полупроводниковой подложке последовательно расположенные диэлектрический слой и разрядный электрод, причем в диэлектрическом слое выполнен паз, в котором расположен слой диэлектрика с пороговой поляризацией.

Источники информации, принятые во внимание при экспертизе:

1.Патент США № 3590337, кл. 317-234, 1972.

2.Патент Франции № 2154620, кл. Н 01 g 1/00, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка памяти | 1978 |

|

SU752476A1 |

| ЯЧЕЙКА ПАМЯТИ | 1976 |

|

SU611581A1 |

| Интегральное запоминающее устройство | 1976 |

|

SU731864A1 |

| Ячейка оперативной памяти | 2024 |

|

RU2826859C1 |

| Устройство для усиления сигнала от ячейки матричного фотоприёмника | 2016 |

|

RU2616222C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МОНОП-ЯЧЕЙКИ ПАМЯТИ, ЯЧЕЙКА ПАМЯТИ И МАТРИЧНЫЙ НАКОПИТЕЛЬ НА ЕЕ ОСНОВЕ | 1996 |

|

RU2105383C1 |

| СПОСОБ АНАЛОГОВО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ СВЕТОВОГО ИЗЛУЧЕНИЯ НА ДИОДЕ С ПЕРЕКЛЮЧАЕМОЙ ПРОВОДИМОСТЬЮ И ФОТОПРИЕМНИК ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2011 |

|

RU2499291C2 |

| Матричный накопитель | 1984 |

|

SU1403096A1 |

| Матричный накопитель для постоянного запоминающего устройства | 1978 |

|

SU1444890A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1980 |

|

SU888731A1 |

Авторы

Даты

1978-10-15—Публикация

1976-02-05—Подача