Изобретение относится к вычислительной технике и может быть использовано при моделировании случайных процессов, а также в стохастических вычислительных машинах при вводе, преобразовании и выводе информации. Известны стохастические преобразо ватели, преобразующие случайную посл довательность Бернулли в цифровой код, матиматическое ожидание которого пропорционально заданной функции от вероятности поябления единичного символа во входном случайном потоке Известен стохастический преобразователь, содержащий реверсивный счетчик, схему сравнения и генерато случайных чисел 1. Однако он не позволяет реализовать заданные функциональные эависимости. Известен также преобразователь, содержащий набор логических схем и многоканальный генератор несовместных случайных коэффициентов 2J. Однако он не позволяет реализог аать произвольную непрерывную функц ональную зависимость. Наиболее близким техническим реш нием к данному изобретению является стохастический преобразователь, содержащий первый регистр сдвига, первый вход которого соединен с первым входом стохастического преобразователя, генератор тактовых импульсов, первую группу элементов И, первые входы которых подключены к разрядны Hfcw выходам регистра сдвига соответственно, второй вход первого элемента И первой группы соединен с первым выходом генератора тактовых импульсов, второй вход каждого последующего элемента Н первой группы соединен с выходом предыдущего элемента И этой же группы, реверсивный счетчик, выход которого подключен к первому выходу стохастического преобразователя, преобразователь код-вероятность, входы которого соединены с выходом реверсивного счетчика и с первым выходом генератора тактовых импульсов, а выход преобразователя код-вероятность соединен со вторвм выходом стохастического преобразователя 3. Известный преобразователь, реализующий метод полиноминального представпения воспроизводимой функции, имеет низкую точность, большую сложность и ограниченные функциональные возможности, что объясняется применением

генератора несовместных случайных коэффициентов при реализации полинома и преобразователя код-вероятность для обеспечения следящего режима работы устройства. Известный преобразователь не позволяет, в частности, реализовать произвольную дробно-рациональную функцию.

Цель изобретения - увеличение точности стохастического преобразовател типа вероятность-код(. вероятность-вероятность , вероятностьчастота, реализующего функции, входящие в класс непрерывных ограниченных функций, а также произвольные цробно-рациональные функции.

Поставленная цель достигается тем что преобразователь дополнительно содержит первую группу элементов ЗАПРЕТ, преобразователь код-частота, второй регистр сдвига, переключатель вторую группу элементов И, вторую группу элементов ЗАПРЕТ, .первый и второй блоки памяти, первый, второй и третий сумматоры, первый и второй блоки контроля переполнения, первый вход первого элемента ЗАПРЕТ первой группы соединен с первым выходом генератора тактовых импульсов, а первы вход каждого последующего элемента ЗАПРЕТ первой группы подключен к выходу соответствующего элемента И первой группы, второй вход каждого предыдущего элемента ЗАПРЕТ первой группы соединен с первым входом каждого последующего элемента ЗАПРЕТ этой же группы, входы преобразователя кодчастота соединены с выходом реверсивного счетчика и с первым выходом генератора тактовых импульсов, первый вход второго регистра сдвига подключен к первому выходу переключателя, вход которого соединен со вторым входом стохастического преобразователя, а второй выход переключателя соединен со вторым выходом стохастического преобразователя, вторые входы регистров сдвига объединены и подключены ко второму выходу генератора тактовых импульсов, первые входы элементов И второй группы соединены с разрядными выходами второго регистра сдвига соответственно, второй вход первого элемента И второй группы подключен к выходу преобразователя кодчастота, а второй вход каждого последующего элемента И второй группы со единен с выходом предыдущего элемента И этой же группы, первые входы первого и второго элементов ЗАПРЕТ второй группы подключены соответственно к первому выходу генератора тактовых импульсов и к выходу преобразователя код-частота, а первые входы остальных элементов ЗАПРЕТ этой же группы соединены с выходами соответствующих элементов И второй группы, второй вход каж.цого -предыдудего элемента ЗАПРЕТ второй группы

подключен к первому входу каждого последующего элемента ЗАПРЕТ этой же группы, адресные входы первого и второго блоков памяти соединены соответственно с выходами первой и второй групп элементов ЗАПРЕТ и с Влходами последних элементов И первой и второй групп элементов И, разрядные входы первого и второго сумматоров подключены к разрядным выходам первого и второго блоков памяти соответственно, входы первого и второго блоков контроля переполнения соединены с выходами первого и второго сумматоров и со вторым и третьим выходами генератора тактовых импульсов соответственно, первые и вторые выходы блоков контроля переполнения подключены к установочным входам первого и второго сумматоров соответственно, входы третьего сумматора соединены с третьими и четвертыми выходами блоков контроля переполнения соответственно, выходы третьего сумматора соединены со входами реверсивного счетчика, выход преобразователя код-частота подключен .к третьему выходу стохастического преобразователя.

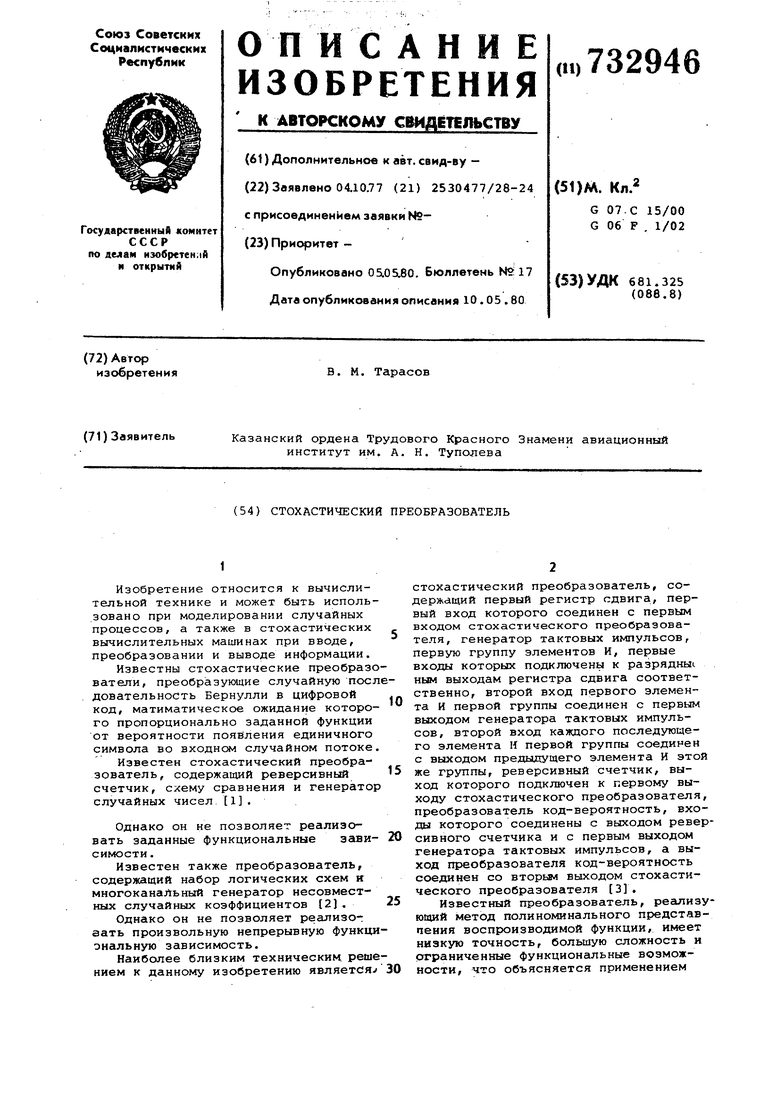

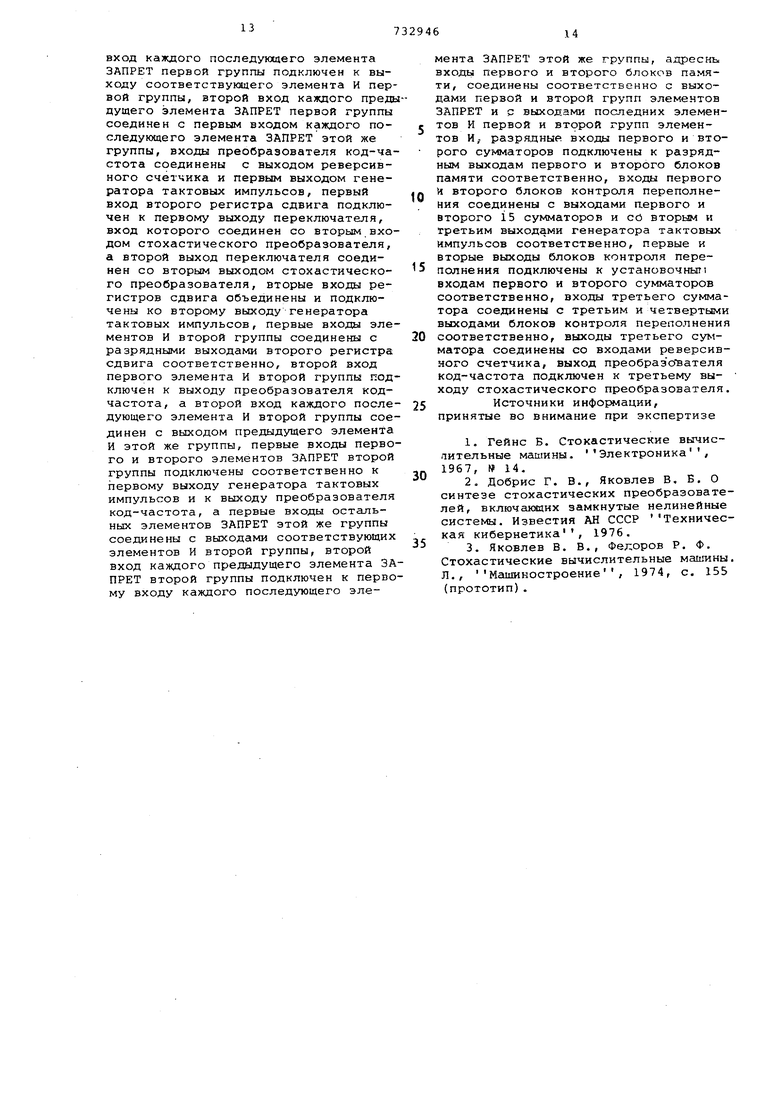

На фиг. 1 приведена блок-схема стохастического преобразователя; на фиг. 2 - схема блока контроля перепонения;- на фиг. 3 - схема третьего суматора.

Стохастический преобразователь содержит первый регистр 1 сдвига, первую группу 2 элементов И, первую групу 3 элементов ЗАПРЕТ, первый блок 4 памяти, первый сумматор 5, первый блок 6 контроля переполнения, третий сумматор 7, реверсивный счетчик 8, преобразователь 9 код-вероятность, преобразователь 10 код-частота, второй регистр 11 сдвига, вторую группу 12 элементов И, вторую группу 13 элементов ЗАПРЕТ, второй блок 14 памяти второй сумматор 15, второй блок 16 контроля переполнения, генератор 17 тактовых импульсов, первый У8 и второй 19 входы, первый 20, второй 21 и третий 22 выходы и переключатель 2

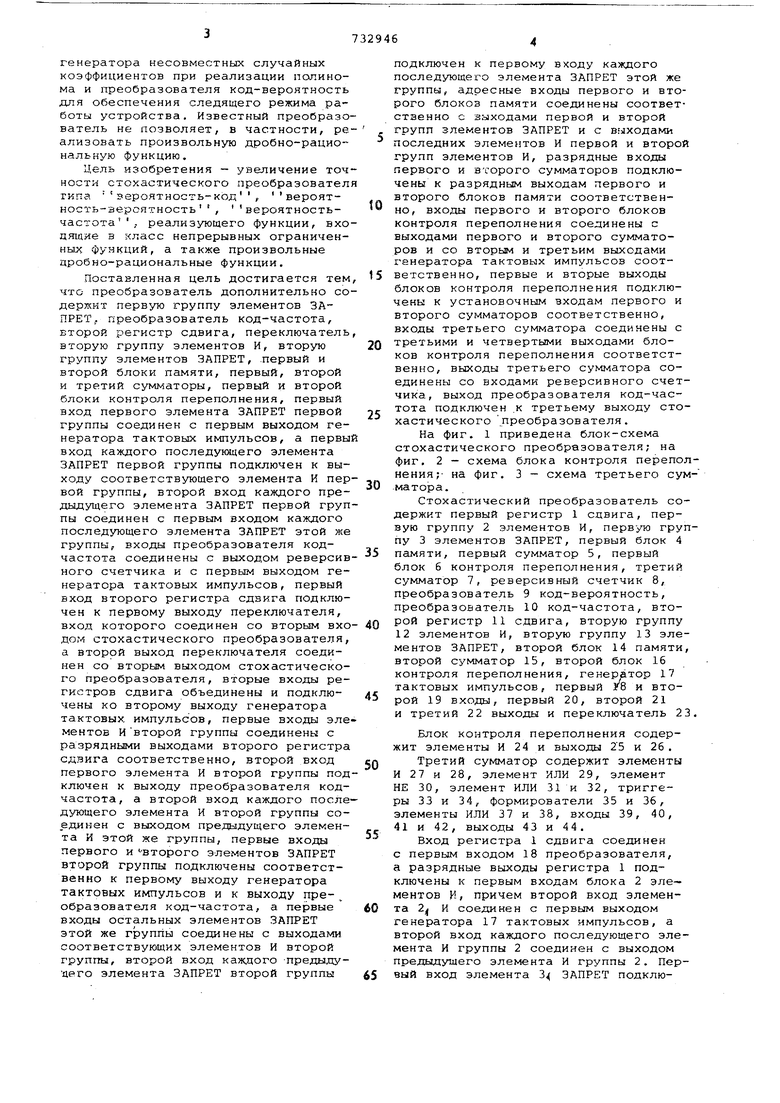

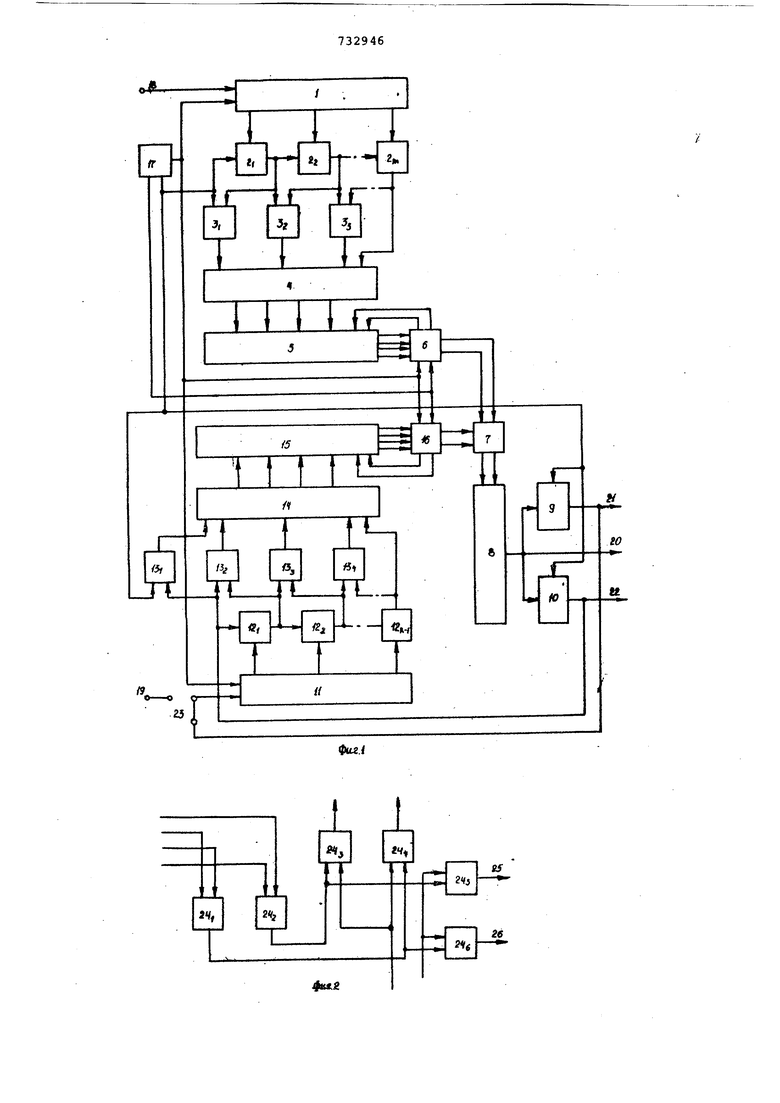

Блок контроля переполнения содержит элементы И 24 и выходы 25 и 26 .

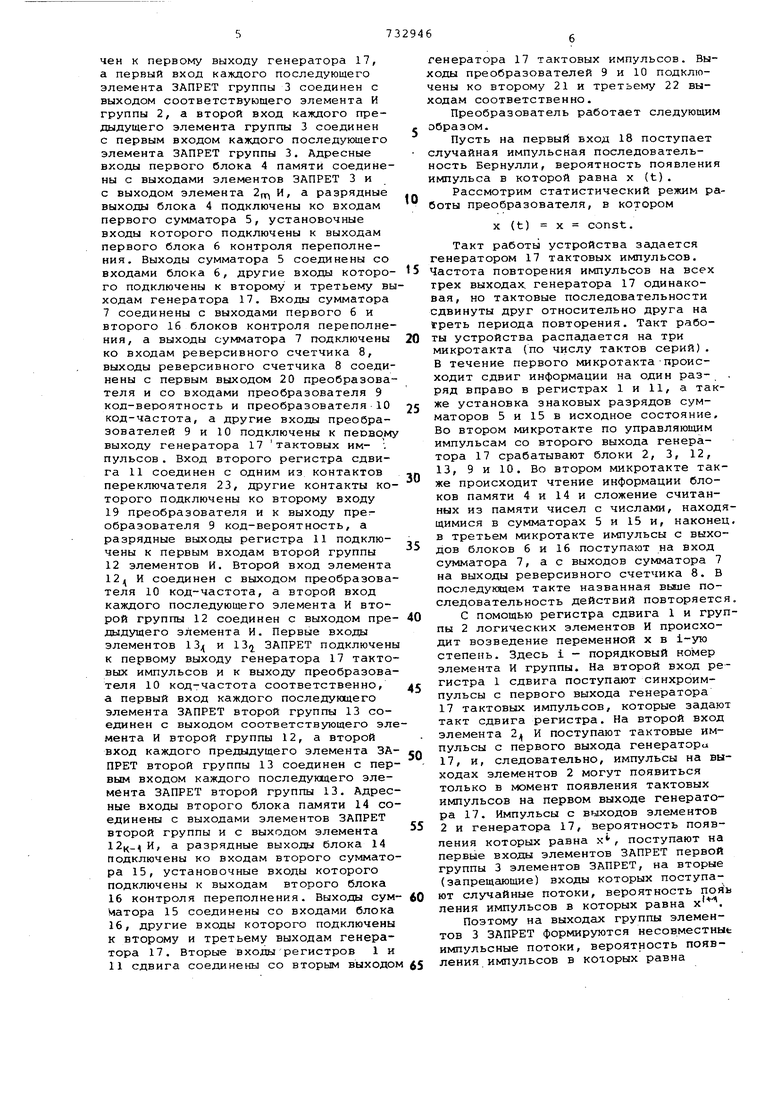

Третий сумматор содержит элементы и 27 и 28, элемент ИЛИ 29, элемент НЕ 30, элемент ИЛИ 31 и 32, триггеры 33 и 34, формирователи 35 и 36, элементы ИЛИ 37 и 38, входы 39, 40, 41 и 42, выходы 43 и 44.

Вход регистра 1 сдвига соединен с первым входом 18 преобразователя, а разрядные выходы регистра 1 подключены к первым входам блока 2 элементов И, причем второй вход элемента 2 и соединен с первым выходом генератора 17 тактовых импульсов, а второй вход каждого последующего элемента И группы 2 соединен с выходом предыдущего элемента И группы 2. Первый вход элемента 3 ЗАПРЕТ подключен к первому выходу генератора 17, а первый вход каждого последующего элемента ЗАПРЕТ группы 3 соединен с выходом соответствующего элемента И группы 2, а второй вход каждого предыдущего элемента группы 3 соединен с первым входом каждого последующего элемента ЗАПРЕТ группы 3. Адресные входы первого блока 4 памяти соединены с выходами элементов ЗАПРЕТ 3 и с выходом элемента 2 И, а разрядные выходы блока 4 подключены ко входам первого сумматора 5, установочные входы которого подключены к выходам первого блока 6 контроля переполнения. Выходы сумматора 5 соединены со входами блока 6, другие входы которого подключены к второму и третьему выходам генератора 17. Входы сумматора 7 соединены с выходами первого 6 и второго 16 блоков контроля переполнения, а выходы сумматора 7 подключены ко входам реверсивного счетчика 8, выходы реверсивного счетчика 8 соединены с первым выходом 20 преобразователя и со входами преобразователя 9 код-вероятность и преобразователя 10 код-частота, а другие входы преобразователей 9 и 10 подключены к пеовому выходу генератора 17 тактовых импульсов . Вход второго регистра сдвига 11 соединен с одним из контактов переключателя 23, другие контакты которого подключены ко второму входу 19 преобразователя и к выходу преобразователя 9 код-вероятность, а разрядные выходы регистра 11 подключены к первым входам второй группы 12 элементов И. Второй вход элемента 12; И соединен с выходом преобразователя 10 код-частота, а второй вход каждого последующего элемента И второй группы 12 соединен с выходом предыдущего элемента И. Первые входы элементов iЗ и 13,2. ЗАПРЕТ подключены к первому выходу генератора 17 тактовых импульсов и к выходу преобразователя 10 код-частота соответственно, а первый вход каждого последующего элемента ЗАПРЕТ второй группы 13 соединен с выходом соответствующего элемента И второй группы 12, а второй вход каждого предыдущего элемента ЗАПРЕТ второй группы 13 соединен с первым входом каждого последующего элемента ЗАПРЕТ второй группы 13. Адресные входы второго блока памяти 14 соединены с выходами элементов ЗАПРЕТ второй группы и с выходом элемента 12( И, а разрядные выходы блока 14 подключены ко входам второго сумматора 15, установочные входы которого подключены к выходам второго блока 16 контроля переполнения. Выходы сумМатора 15 соединены со входами блока 16, другие входы которого подключены К второму и третьему выходам генератора 17. Вторые входы регистров 1 и 11 сдвига соединены со вторым выходом

генератора 17 тактовых импульсов. Выходы преобразователей 9 и 10 подключены ко второму 21 и третьему 22 выходам соответственно.

Преобразователь работает следующим образом.

Пусть на первый вход 18 поступает случайная импульсная последовательность Бернулли, вероятность появления импульса в которой равна х (t).

Рассмотрим статистический режим ра0боты преобразователя, в котором

X (t) X const.

Такт работы устройства задается генератором 17 тактовых импульсов.

5 Частота повторения импульсов на всех грех выходах, генератора 17 одинаковая, но тактовые последовательности сдвинуты друг относительно друга на tpeTb периода повторения. Такт рабо0ты устройства распадается на три микротакта (по числу тактов серий) . В течение первого микротакта-происходит сдвиг информации на один разряд вправо в регистрах 1 и 11, а также установка знаковых разрядов сум5маторов 5 и 15 в исходное состояние. Во втором микротакте по управляющим импульсам со второго выхода генератора 17 срабатывают блоки 2, 3, 12, 13, 9 и 10. Во втором микротакте так0же происходит чтение информации блоков памяти 4 и 14 и сложение считанных из памяти чисел с числами, находящимися в сумматорах 5 и 15 и, наконец, в третьем микротакте импульсы с выхо5дов блоков 6 и 16 поступают на вход сумматора 7, ас выходов сумматора 7 на выходы реверсивного счетчика 8. В последукяцем такте названная выше последовательность действий повторяется. С помощью регистра сдвига 1 и груп0пы 2 логических элементов И происходит возведение переменной х в i-ую степень. Здесь i - порядковый номер элемента И группы. На второй вход регистра 1 сдвига поступают синхроим5пульсы с первого выхода генератора 17 тактовых импульсов, которые задают такт сдвига регистра. На второй вход элемента 2 И поступают тактовые импульсы с первого выхода генератора

0 17, и, следовательно, импульсы на выходах элементов 2 могут появиться только в момент появления тактовых импульсов на первом выходе генератора 17. Импульсы с выходов элементов

5 2 и генератора 17, вероятность появления которых равна , поступают на первые входы элементов ЗАПРЕТ первой группы 3 элементов ЗАПРЕТ, на вторые (запрещающие) входы которых поступают случайные потоки, вероятность пояь

0 пения импульсов в которых равна х . Поэтому на выходах группы элементов 3 ЗАПРЕТ формируются несовместны : импульсные потоки, вероятность появления импульсов в которых равна

5 ie(o,m-i), т - количество элементов И в группе 2. Форму ла х-,- х - вытекает из формулы для математического ожидания последовательности на выходе логического элемента ЗАПРЕТ, если в последнюю подставить значения вероятностей по явления импульсов на входах элемента ЗАПРЕТ и значение взаимнокорреляционной функции входных случайных потоков. Выходы элементов ЗАПРЕТ группы 3 и выход элемента 2 И соединены с адресными входами блока 4 памяти, в ко тором хранятся константы Ь; , Так выход элемента 3; ЗАПРЕТ соединен с ад ресным входом ячейки, в которой хранится константа Ьд , выход элемента Зд - со входом ячейки памяти, в которой хранится константа Ь , и т. д. Наконец, выход элемента 2пп И соедине с адресным входом ячейки памяти, в чоторой хранится константа bm . При появлении импульса на выходе элемен та 3) (или 2 m И) происходит чтение числа ь-, из блока 4 памяти (с функцио нальной точки зрения блоки 1, 2, 3 выступают в роли своеобразного дешиф ратора адреса запоминающего устройст ва 4). Но вероятность появления импульса на выходе элемента З ЗАПРЕ равна X; X , а вероятность появления импульса на выходе элемента 2т И равна Хт х. Следовательно число Ь-, из блока 4 памяти счит ваться с вероятностью х; х - , где i е (о, га-1) , а чтение числа Ь будет происходить с вероятностью х. Числа с выхода блока памяти 4 поступают на вход сумматора 5, где они складываются с содержимым сумматора 5. Отсюда математическое ожидание кода, поступающего на вход сумматора 5, равно m Е(х) 1 Ь,.-У(. Пусть необходимо с помощью предлагаемого устройства реализовать фун цию Р{х), которая аппроксимируется с заданной точностьюполиномом Рт(х) РО + Р X + +.,. + Рг х степени т. Здесь х - вероятность появления импульса на первом входе 18. , При Ь-|-|Р; , учитывая, что х-| х х ,-х х, получают Е(Х |Ь -Х; |Р;Л-Р СХ),. Таким образом, если Ь;- 5 Р; , то математическое ожидание числового ко да, поступающего на вход сумматора 5 равно значению реализуемого полинома Р,Т((х). Коэффициенты ь; можно для конкретного полинома Pfr,(x) сосчитать за ранее и записать в блок 4 памяти в д полнительном коде. Сумматор 5, блок 6 контроля переполнения, сумматор 7 и реверсивный счетчик 8 выполняют функции усредняю щего устройства (устройства для вычисления оценки математического ожидания входного сигнала). Но математическое ожидание входного сигнала Е(х) равно значению заданного полинома Р (х) , и, следовательно, на вьгходе усредняющего устройства будет образован цифровой код, математическое ожидание хоторого равно полиному Р (х) , Таким образом, на выходе реверсивного счетчика 8, в котором находятся старшие разряды выходного сигнала, образуется цифровой код, математическое ожидание которого равно заданной нелинейной зависимости РГ„ (х) от вероятности х появления импульса на входе 18, т. е. реализуется нелинейное преобразование типа вероятность-код. Усредняющее устройство (блоки 5, 6, 7, 8) работает следующим образом. Сумматор 5 представляет стандартный накапливающий сумматор, разрядность которого равна разрядности чисел to;. Числа Ь; представлены модифицированным дополнительным кодом, т. е. кодом, в котором для представления знака числа используются два разряда. При этом знак плюс обозначается двумя нулями (00) , а знак минус - двумя единицами (11). Модифицированный код используется для получения признака переполнения. При алгебраическом сложении на переполнение разрядной сетки указывает несовпадение цифр в знаковых разрядах. Комбинации 01 в знаковых разрядах соответствует положительное число, а комбинации 10 - отрицательное число. При коэффициентах Ь по модулю меньших единицы переполнение разрядной сетки сумматора 5 возникает тогда, когда модуль суммы больше единицы или равен ей, но меньше двух. Усредняющее устройство состоит из блоков 5, б, 7, и 8, причем в сумматоре 5 находятся младшие разряды результата преобразования, а в/блоках 7 и 8 - старшие разряды. При переполнении разрядной сетки сумматора 5 (т. а , при возникновении переноса в старшие разряды), формируется сигнал переполнения (переноса), причем этот сигнал поступает на вход следукядегОр более старшего разряда усредняющего устройства, т. е. на вход одноразрядного комбинационнонакапливающего, сумматора 7. Формирование сигнала переполнения разрядной сетки сумматора 5 осуществляется блоком б. Блок 6 контроля переполнения состоит из шести логических элементов И. Входы блока 6 связаны с прямым и инверсным выходами знаковых разрядов сумматора 5 (в сумматоре 5 два знаковых разряда), а также с вторым и третьим выходами генератора 17 тактовых импульсов. Так как на переполнение разрядной сетки указывает несовпадение цифр в знаковых разрядах то на первый вход элемента 24 И подается инверсный выход старшего знак вого разряда, а.на второй вход - пря мой выход .младшего знакового разряда т. е. комбинация цифр 01. Следовател но на выходе элемента 24. И сигнал появляется только тогда, когда в сум маторе 5 возникает положительное переполнение (если сумма двух чисел больше или равна единице). На первый вход элемента 24 И подается инверсный вьоход младшего знакового разряда а на второй вход - прямой выход стар шего знакового разряда, т. е. комбинация цифр 10, поэтому на выходе эле мента 24j И сигнал появляется только тогда, когда в сумматоре 5 возникает отрицательное переполнение. Выход элемента 24,, И соединен со входами элементов 24д И и 24 И, и поэтому на выходах элементов 24 И и 24g И импульс появляется только тогда, когда в сумматоре 5 возникает положительное переполнение. Выход элемента 24j И соединен со входами элементов 24, И и 24д И и, следовательно, на выходах элементов 24 И и 24g И импульс появляется только тогд когда в сумматоре 5 возникает отрицательное переполнение. Выходы элементов 24дИи24ь Ив дальнейшем подключаются ко входам сумматора 7 {на выходах.этих элементов импульс может появиться только в третьем микротакте, так как один из входов этих элементов соединен с тре тьим выходом генератора 17). Выходы элементов 24 И и И в дальнейшем подключаются к установоч ным входам знаковых разрядов сумматора 5 (импульс на выходах этих эле ментов может появиться в первом мик ротакте, т. е. один из входов этих элементов соединен с первым выходом генератора 17). Выход элемента 24з И соединен со входом установки в единичное состоя ние младшего знакового разряда (на выходе элемента 24з И импульс может появиться только при отрицательном переполнении разрядной сетки сумматора 5, т. е. в знаковых разрядах сумматора 5 находится код 10), и, следовательно, по сигналу с выхода элемента 24.j И произойдет установка знаковых разрядов в состояние 11. Выход элемента 24 И соединен со входом установки в нулевое состояни младшего знакового разряда, и, следовательно, по сигналу с выхода эле мента 24д И произойдет установка знаковых разрядов сумматора 5 в исходное состояние 00. Таким образом осуществляется установка знаковых разрядов сумматора 5 в исходное состояние, что необходимо для правильной работы всего ус редняющего устройства. Итак, сумматор 5 осуществляет сложение поступающих на .его вход чисел Ь; в дополнительном мо/5ифицированном коде (числа Ь; ) на вход сумматора 5 поступают с выхода запоминающего устройства 4), причем сигнал переноса в старший разряд, сформированный блоком б, поступает на входы одноразрядного комбинационно накапливающего сумматора 7, на другие входы которого поступает сигнал переноса из сумматора 15. Сумматор.15 выполняет в предлагаемом устройстве те же функции, что и сумматор 5, а блок 16 эквивалентен блоку 6 . Сумматор 7 работает следующим образом. Первый 39 и второй 40 входы сумматора 7 соединены с первым 25 и вторым 26 выходами блока 6 формирования сигнала переполнения, третий 41 и четвертый 42 входы сумматора 7 соединены с первым и вторым выходами второго блока 16 контроля переполнения (на первых вьаходах блоков б или 16 контроля переполнения импульс появляется в третьем микротакте только в том случае, если в сумматорах 5 или 15 возникает отрицательное переполнение). На втором выходе блока 6 (или 16) импульс появляется при положительном переполнении разрядной сетки суммаТора 5 (или 15). Поскольку в сумматоре 5 (или 15) не может одновременно быть положительного и отрицательного переполнений, то, следовательно, импульс может появиться не более чем на одном из выходов блока 6 (или 16). Другими словами, на первом и втором выходах блока 6 (или 16) импульсы одновременно появиться не могут. С учетом последнего и построена схема одноразрядного комбинационно накапливающего сумматора 7. У сумматора 7 в каждый момент времени импульсы могут появиться не более чем на двух входах (один импульс может поступить с выходов блока б, а второй - с выходов 16). Четвертая группа двухвходовых логических элементов И 27 и предназначена для выявления всех возможных комбинаций появлений двух импульсов на входах блока 7. Так, на выходе элемента 21f И сигнал появляется только в том случае, если в сумматоре 5 возникает положительное переполнение (сигнал + 1), а в сумматоре 15 - отрицательное переполнение (сигнал - 1). Действительно, при положительном переполнении разрядной сетки сумматора 5 импульс появляется на втором выходе 26 блока б, но выход 26 блока 6 соединен со вторым входом 40 блока 7, и, следова тельно, импульс с выхода блока 6 поступает на первый вход элемента . На второй вход элемента 27, И импульс поступает только в том случае,

если в сумматоре 15 возникает отрицательный перенос, так как второй вход элемента 27 И соединен с первым выходом блока 16.

На выходе элемента 27 И сигнал появляется только в том случае, если в сумматоре 5 возникает отрицательное переполнение, а в сумматоре 15 положительное переполнение, т, е. на выходах элементов 27 И и 27 И имлульсы появляются только при разнополярности переполнения разрядных сеток сумматоров 5 и 15. Поскольку разнополярные переносы из младаиих разрядов при сложении дают в результате ноль, то импульсы с выходов элементо 27 и 27 И, проходя через элемент 29 ИЛИ и элемент 30 НЕ, запрещают прохождение входных сигналов на выходы блока 7 через пятую группу логических элементов 28 И (запрет осущесвляется с помощью элемента 30 НЕ, на выходе которого будет нулевой потенциал при подаче на его вход единичного уровня).

На выходе элемента 27 И сигнс1л появляется только в том случае, если в сумматорах 5 и 15 возникают отрицательные переполнения. Отрицательные переносы из младших разрядов при сложении дают в результате минус два что равносильно формированию отрицательного переноса в старший разряд, поэтому выход элемента 27,, И через элемент 37 ИЛИ соединен с выходом отрицательного переноса сумматора 7.

На выходе элемента 24 И импульс появляется только в том случае, если в сумматорах 5 и 15 возникают положительные переполнения, поэтому выход элемента 27 И через элемент 38 ИЛИ соединен с выходом положительног6 переноса сумматора 7, Импульсы с выходов элементов 27 И и 27 через элементы 29 ИЛИ и 30 НЕ запрещают прохождение входных сигналов на выходы блока 7 через элементы 28 И.

Таким образом, с помощью комбинационных схем происходит формирование сигналов переноса в старший разряд (старшим разрядом для блока 7 является младший разряд счетчика 8).

Сигнал переноса должен формироваться не только при одновременном приходе двух положительных или отрицательных сигналов на входы блока 7 но и при поступлении каждого второго одиночного положительного или отрицательного сигнала. С этой целью одиночные сигналы, проходя через пя тую группу логических элементов И 28 и соответствующий элемент ИЛИ (31 или 32), поступают на счетный вход триггеров,33 или 34. На счетный вход триггера 33 проходят отрицательные входные сигналы, а на счетный вход триггера 34 - положительные сигнгипы (переносы из суммирующих устройств

5 или 15), Элементы И 28 пропускают на счетный вход триггера только одиночные сигналы (если на входы блока 7 поступают одновременно два импульса, то на выходе одного из элементо И 27 появляется импульс, который запрещает прохождение входных сигналов через элементы И 28). Таким образом, на вход триггеров могут пройти только одиночные сигналы, т. е. переносы только с одного из суммирующих устройств 5 или 15. Поскольку импульсы поступают на счетный вход триггеров 33 и 34, то на выход этих триггеров сможет пройти только каждый второй иг шульс, что и требуется для логики работы блока 7. Далее импульсы с выходов триггеров через импульсные формирователи 35 или 36 и через элементы ИЛИ 37 или 38 поступают на соответствующие выходы блока 7, На выход 43 поступают отрицательные переносы, а на второй выход 44 - положителные переносы в старший разряд. Эти переносы из сумматора 7 поступают на соответствующие входы реверсивного счетчика 8, где происходит их сложение .

Формула изобретения

Стохастический преобразователь, содержащий первый регистр сдвига, первый вход которого соединен с первым входом стохастического преобразователя, генератор тактовых импульсов, первую группу элементов И, первые входы которых подключены к разрядным выходам регистра сдвига соответственно, второй вход первого элемента И первой группы соединен с первым выходом генератора тактовых импульсов, второй вход каждого последующего элемента И первой группы соеди- ; иен с выходом предыдущего элемента И этой же группы, реверсивный счетчик, выход которого подключен к первому выходу стохастического преобразователя, преобразователь код-вероятность, входы которого соединены с выходом реверсивного счетчика и с первым выходом генератора тактовых И1 ульсов, а выход преобразователя код-вероятность соединен со вторым выходом стохастического преобразователя, отличающийся тем, что, с целью увеличения точности стохастического преобразователя он дополнительн содержит первую группу элементов ЗАПРЕТ, преобразователь код-частота, второй регистр сдвига, переключатель вторую группу элементов И, вторую группу элементов ЗАПРЕТ, первый и второй блоки памяти, первый, второй и третий сумматоры, первый и второй блоки контроля переполнения первый вход первого элемента ЗАПРЕТ первой группы соединен с первым выходом генеоатора тактовых импульсов, а первы

вход каждого последующего элемента ЗАПРЕТ первой группы подключен к выходу соответствуквдего элемента И первой группы, второй вход каждого предыдущего элемента ЗАПРЕТ первой группы соединен с первым входом каждого последующего элемента ЗАПРЕТ этой же группы, входы преобразователя код-частота соединены с выходом реверсивного счетчика и первым выходом генератора тактовых импульсов, первый вход второго регистра сдвига подключен к первому выходу переключателя, вход которого соединен со вторым входом стохастического преобразователя, а второй выход переключателя соединен со вторым выходом стохастического преобразователя, вторые входы регистров сдвига объединены и подключены ко второму выходу генератора тактовых импульсов, первые входы элементов И второй группы соединены с разрядными выходами второго регистра сдвига соответственно, второй вход первого элемента И второй группы подключен к выходу преобразователя кодчастота, а второй вход каждого последующего элемента И второй группы соединен с выходом предыдущего элемента И этой же группы, первые входы первого и второго элементов ЗАПРЕТ второй группы подключены соответственно к первому выходу генератора тактовых импульсов и к выходу преобразователя код-частота, а первые входы остальных элементов ЗАПРЕТ этой же группы соединены с выходами соответствующих элементов И второй группы, второй вход каждого предыдущего элемента ЗАПРЕТ второй группы подключен к первому входу каждого последующего элемента ЗАПРЕТ этой же группы, адреснь входы первого и второго блоков памяти, соединены соответственно с выходами первой и второй групп элементов ЗАПРЕТ и р выходами последних элеменс тов И первой и второй групп элементов И, разрядные входы первого и второго сумматоров подключены к разрядHfcJM выходам первого и второго блоков памяти соответственно, входы первого

И второго блоков контроля переполнения соединены с выходами первого и второго 15 сумматоров и cd вторым и Третьим выходами генератора тактовых импульсов соответственно, первые и вторые выходы блоков контроля пере5 полнания подключены к установочнып входам первого и второго сумматоров соответственно, входы третьего сумматора соединены с третьим и четвертыми выходами блоков контроля переполнения

0 соответственно, выходы третьего сумматора соединены со входами реверсивного счетчика, выход преобразотвателя код-частота подключен к третьему выходу стохастического преобразователя.

5 Источники информации,

принятые во внимание при экспертизе

1.Гейне Б. Стохастические вычислительные машины. Электроника, 1967, № 14,

2,Добрис Г. В., Яковлев В. Б. О

синтезе стохастических преобразователей, включанвдих замкнутые нелинейные системы. Известия АН СССР Техническая кибернетика , 1976.

3. Яковлев В. В., Федоров Р. Ф.

Стохастические вычислительные машины. Л., Машиностроение, 1974, с. 155 (прототип).

40 39

41

f5

| название | год | авторы | номер документа |

|---|---|---|---|

| Нелинейный вероятностный преобразователь | 1976 |

|

SU610119A1 |

| Стохастический функциональный преобразователь | 1977 |

|

SU732892A1 |

| Цифровой преобразователь координат | 1977 |

|

SU742944A1 |

| Устройство для возведения в степень | 1976 |

|

SU634273A1 |

| Преобразователь кодов | 1978 |

|

SU744548A1 |

| Адаптивный групповой приемник многочастотного кода с импульсно-кодовой модуляцией | 1989 |

|

SU1830632A1 |

| Вероятностный коррелометр | 1986 |

|

SU1327121A1 |

| Генератор систем функций Аристова | 1989 |

|

SU1746373A1 |

| Стохастическое вычислительное устройство | 1982 |

|

SU1062700A1 |

| Устройство для моделирования нейрона | 1989 |

|

SU1709356A1 |

Авторы

Даты

1980-05-05—Публикация

1977-10-04—Подача