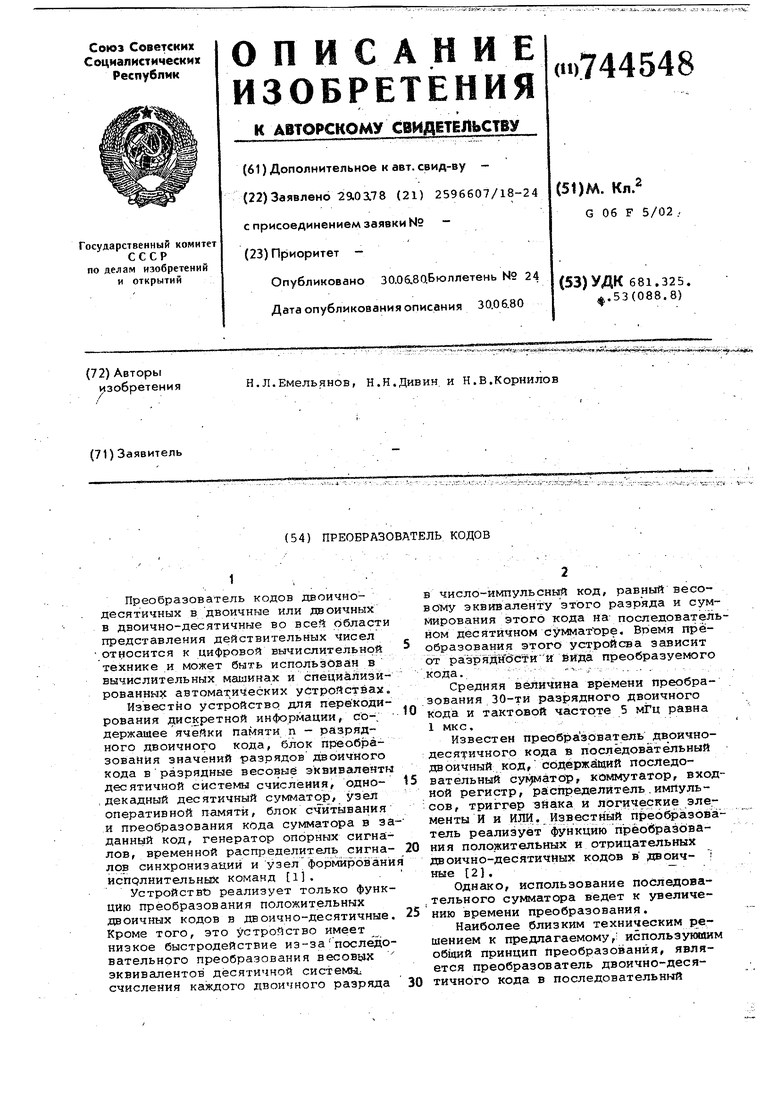

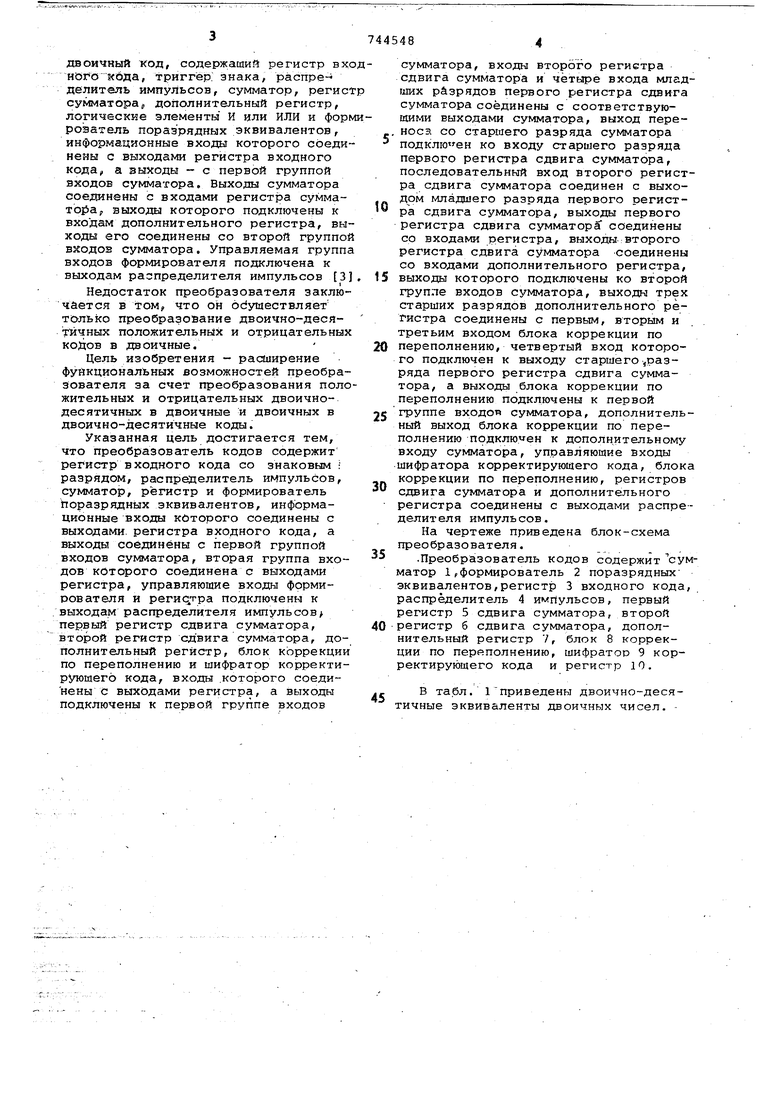

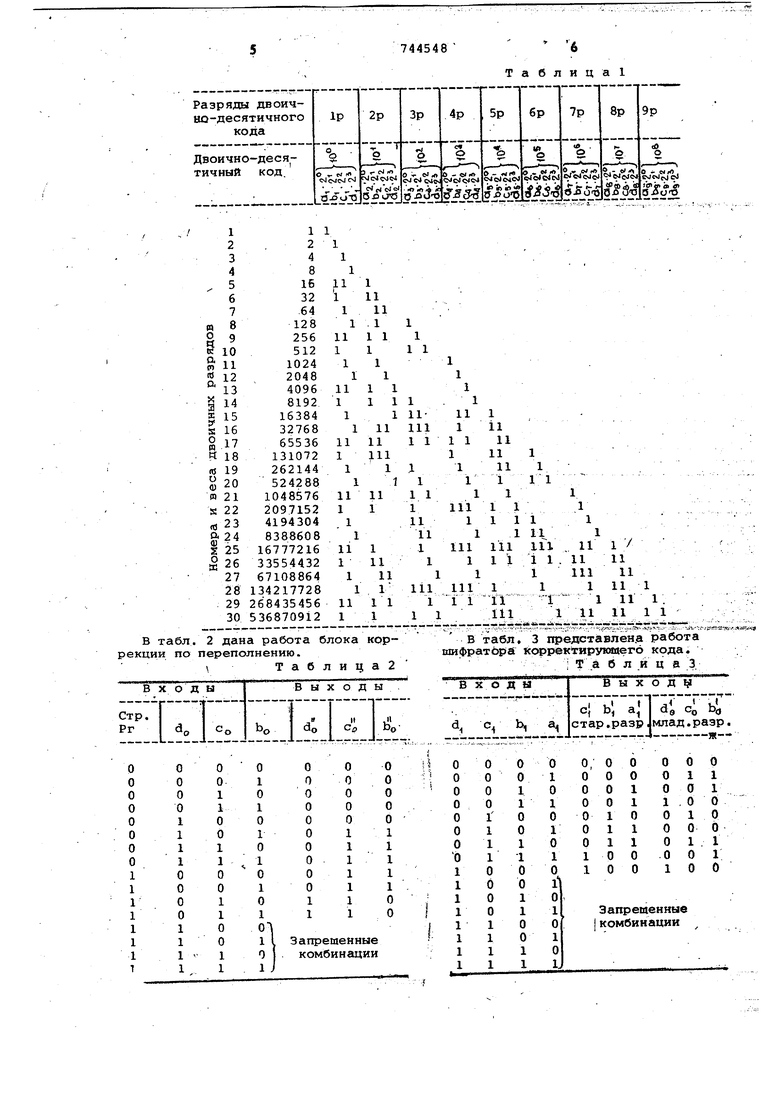

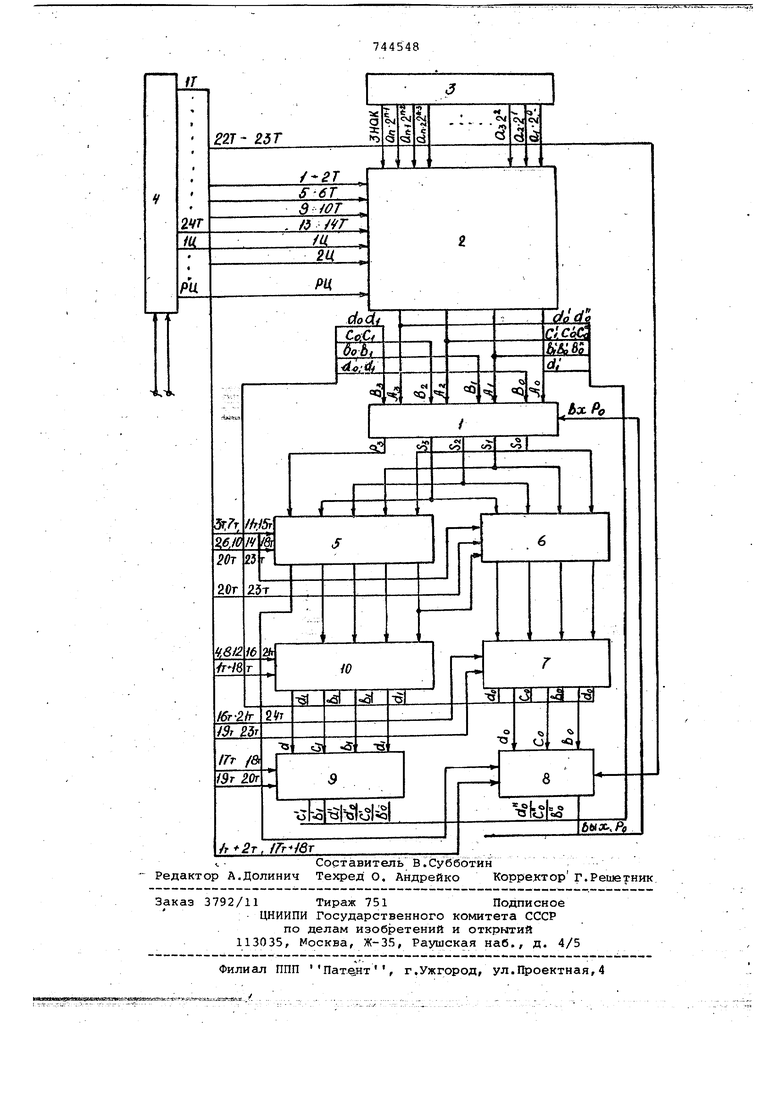

(54) ПРЕОБРАЗОВАТЕЛЬ КОДОВ 1, Преобразователь кодов двоичнодесятичных в двоичные или двоичных в двоично-десятичные во всей области представления действительных чисел относится к цифровой вычислительной технике и может быть использован в вычислительных машинах и специализированных автомат.ических устройствах. Известно устройство для перекодирования дискретной информации, со-. держащее ячейки памяти п - разрядного двоичного кода, блок П1« об}эазования значений разрядов двоичного кода вразрядные весовые эквиваленты десятичной системы счисления, однодекадный десятичный сумматозр, узеЛ оперативной памяти, блок считывания и преобразования кода сумматора в за данный код, генератор опорных сигналлов, временной распределитель сигналов синхронизации и узелформировани испрлнительных команд 1. Устройства реализует только функцию преобразования положительных двоичных кодов в двоично-десятичные. Кроме того, это устройство имеет низкое быстродействие из-запоследовательного преобразования весовых эквивалентов десятичной системы.; счисления каждого двоичного разряда в число-импульсный код, равный весовому эквиваленту этого разряда и сумкшрования Этого кода на последовательном десятичном сумматоре , преобразования этого устройева зависит от разрядндсти и бйда. преобразуемого кода.У Средняя величина времени преобразования 30-ти разрядного двоичного кода и тактовой частоте 5 мГц равна 1 МКС. Известен преобразователь двоичйодеся1ричного кода в последовательный двоичный код, сбдержйщий последовательный , коммутатор, входной регистр, ра;спределитель.импульсов, триггер знака и логические элементы И и ИЛИ. Известный прео азователь реализует функцию преобразования положительных и отрицательных двоично-десятичных кодов в двоич- : ные 21. Однако, использование последовательного сумматора ведет к увеличению времени преобразования. Наиболее близким техническим решением к предлагаемому ,i используимаим общий принцип преобразования, является преобразователь двоично-десятичного кода в последовательный двоичный код, содержащий регистр вх ного кода, триггер; знака, распре- делитель импульсов, сумматор, регис сумматора;, дополнительный регистр, логические элементы И или ИЛИ и фор рователь поразрядных эквивалентов, информационные входы которого соеди нены с выходами регистра входного кода, а выходы - с первой группой входов сумматора. Выходы сумматора соединены с входами регистра сумматора,, выходы которого подключены к входам дополнительного регистра, вы ходы его соединены со второй группо входов сумматора. Управляемая групп входов формирователя подключена к выходам распределителя импульсов 3 Недостаток преобразователя заклю чается в том, что он 6с ушествляет только преобразование двоично-десятичных положительных и отрицательны кодов в двоичные. Цель изобретения - расширение функциональных возможностей преобра зователя за счет преобразования пол жительных и отрицательных двоичнодесятичных в двоичные и двоичных в двоично-десятичные коды. Указанная цель достигается тем, что преобразователь кодов содержит регистр входного кода со знаковым ; разрядом, распределитель импульсов, сумматор, регистр и формирователь поразрядных эквивалентов, информационные входы которого соединены с выходами, регистра входного кода, а выходы соединены с первой группой входов сумматора, вторая группа входов которого соединена с выходами регистра, управляющие входы формирователя и регис;гра подключены к выходам распределителя импульсов первый регистр сдвига сумматора, второй регистр сдвига сумматора, дополнительный регистр, блок коррекции по переполнению и шифратор корректи рующего кода, входы .которого соединены С выходами регистра, а выходы подключены к первой группе входов сумматора, входы второго регистра сдвига сумматора и четыре входа младших разрядов первого регистра сдвига сумматора соединены с соответствующими выходами сумматора, выход переноса со старшего разряда сумматора подклю ен ко входу старшего разряда первого регистра сдвига сумматора, последовательный вход второго регистра сдвига сумматора соединен с выходом младшего разряда первого регистра сдвига сумматора, выходы первого регистра сдвига сумматорS соединены со входами регистра, выходы:второго регистра сдвига сумматора Соединены со входами дополнительного регистра, выходы которого подключены ко второй группе входов сумматора, выходы трех старших разрядов дополнительного регистра соединены с первым, вторым и третьим входом блока коррекции по переполнению, четвертый вход которого подключен к выходу старшего ,разряда первого регистра сдвига сумматора, а выходы блока коррекции по переполнению подключены к первой группе входои сумматора, дополнительный выход блока коррекции по переполнению подключен к дополнительному входу сумматора, управляющие входы шифратора корректирующего кода, блока коррекции по переполнению, регистров сдвига сумматора и дополнительного регистра соединены с выходами распределит ел я импуль сов. На чертеже приведена блок-схема преобразователя. .Преобразователь кодов содержит сумматор 1,формирователь 2 поразрядных эквивалентов,регистр 3 входного кода, распределитель 4 импульсов, первый регистр 5 сдвига сумматора, второй регистр б сдвига сумматора, дополнительный регистр V, блок 8 коррекции по переполнению, шифратор 9 корректирук)щего кода и регистр Ю. В табл. 1приведены двоично-десятичные эквиваленты двоичных чисел.

Таблица

744548

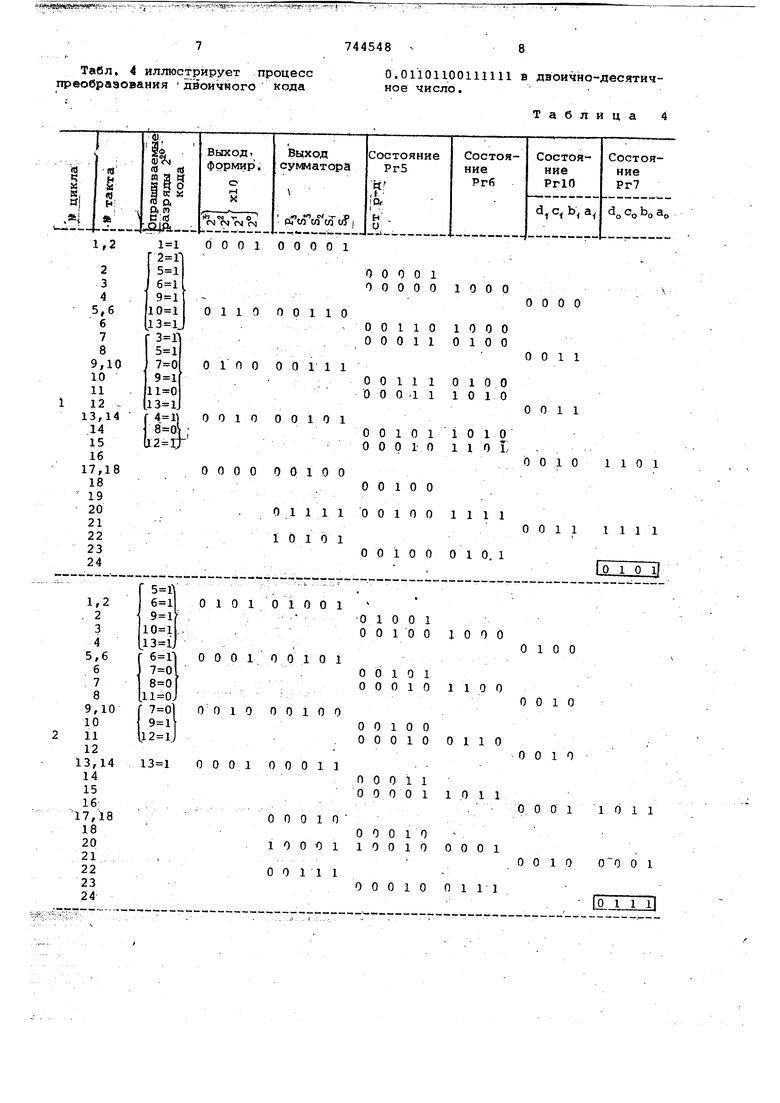

Табл. 4 иллюстрирует процесс преобразования двоичного кода

8

0.01101100111111 6 двоично-десятичное число.

Таблица 4

-/Продолжение табл.4

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоично-десятичного кода в последовательный двоичный код | 1975 |

|

SU720424A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код градусов,минут,секунд | 1980 |

|

SU960791A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код | 1980 |

|

SU943703A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1444958A1 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный | 1974 |

|

SU620975A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1554143A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1978 |

|

SU767749A1 |

| Преобразователь двоично-десятичной дроби в двоичную дробь | 1979 |

|

SU860053A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1979 |

|

SU860054A1 |

1,2 f

0001 00011 2

3

4

5,6 pool 00010 б .

7 8

9,10 1. 0001 oooio

10 11.

12 13,140000 00001

14

15

16 17,18.00000

18

2001001

21

2201001

23

24

00000000,0

1,2

2

3

4 5,6 000. 1 00001

6

7

8

000100001

9,10 10

11 12 000000000

13,14 1.4 15

16

о ,0 о о ,0 17,18 18 20 21 22 23 24

00110 00110

Преобразователькодов работает следующим образом.

Входы А разрядного сумматора 1 соединены через-,шину А слагаемого с выходами формирователя 2 поразрядных эквивалентов. Количество выходов формирователя 2, а, следовательно, разрядность сумматора зависит только от разрядности преобразуемого кода, но не от его вида. Входы формирователя 2 .соединены с одной стороны с выходами регис- ра 3 входного кода, а

00011

00001 1000.

о о ю 1

00010 00001 0100

0001

00010 00001 0010

0001

00001 00000 1001

0000 1001

00000 00000 1001

0000 1001

00000 10-01

I 1 001

00000 00000 0000

0000

00001 00000 1000

0000

00001 00000 1100

0000

00000 00000 0110

0000 0110

00000 00000 0110

0000 0110

00000 0110

|0 1 1 01

- с выходами распределителя ов, количество выходов котоN РЦ + 24 Т;,

количество циклов, равное количеству разрядов преобразованного кода; количество тактов в каждом цикле при преобразовании двоичного кода в двоичнодесятичный код. Выход каждого разряда сумматорас У 1Ш гТТ11ёреноеа Ч:;о сгаршёгб1Газряда Соейинени с входом соответствующего разряда сдвигающего регистра 5.сумматора, четыре мла;ц11их разряда его соединены с соответствующими разрядами четырехразрядного сдвигающего регистр-а б cyMiviaTOpa, Выходмладшёто разряда первого регистра 5 сум матора соедин1ен с последовательным входом второго регистра 6 сдвига. Выходы регистра б подключены к соответствующим входам дополнительного регистра 7, выходы трех старших раарядов которого соединены с входа ми блока коррекции по переполнению 8. Выходы Ьд , Со, do схемы 8, через шину А слагаемого соединены с входами А , AJ и AJ сумматора . Шлход РО блока коррекции по переполнению соединены с входом РО сугл атора 1. Все выходы первого регистра сдвига sa исключением старшего разряда, соединены с входами регистра 10, стар ший разряд его подключен к четвертому входу блока 8. Выходы регистра 10 подключены к входам шифратора корректирующего кода 9, а вйхода JD; , ci , д , а , .Ь , с чёрёЗ шину слагаемого А Соединены с соответствующими входами сумматора I. В то же время выходы а Ь , CQ , Af, регистра 7 И выходы а , Ц , с , d регистра 10, через шину слагаемого В соединены с входами Во, Щ , В сумматора. Управляющие входы регист ров 5, б, 7, 10, схемы 8, а также шифратора 9 соединены с выходами ра пределителя 4. ... , „. . -„ ., . Работа предлагаемого преобразова теля описана для случая преобразова ния двоичного кода в двоично-десяти ный код. ... По команде Вид преобразования На вход распределителя 4 поступает входная частота ( ) , с помощью ко торой распределитель 4 вырабатывает количество циклов, равное разрядности преобразованного двоично-десятичного кода и в каждом цикле по 24 так товых импульса, а также устанавливаются S нулевое состояние регистры 5, б, 7 и 10,- Во время 1-го и 2-го тактовых импульсов первого цикла распределителя импульсов опрашивается двоичный разряд регистра 3 с весом 2 формирователем ,2 . Одновременно выходы формирователя подключаются /через Тйины слагаемого ,А на входы А сумматора 1, на входы В, через шины слагаемого В , подключаются выходы регистра 10 и .на дополнительный вход РО его подключается дополнительный выход РО блока 8, Таким образом, на выходе формирователя образуется двоичный 4-х разрядный код (слагаемое А ) для случая преобразования 30-ти разрядного двоичного кода, равный значению разряда с 2 Формирователь выполняет функцию преобразования одновесовых единицОпрашиваемых разрядов в двоичный 4-х разрядный код. Если опрашиваемый разряд с весом 2° равен единице, то на выходе формирователя будет двоичный код, равный 0001. Слагаемое В равно 0000, так как регистр 10 установлен в нулевое состояние. На дополнительном входе PQ сумматора 1 также будет О, так как старший разряд регистра 5, подключаемый ко входу РО сумматора 1-2т рас- . предёлителя импульсов через блок коррекции по переполнению 8 равен О. Работа блока 8 поясняется таблицей истинности (табл.2). Следовательно, на выходе сумматора 1 будет код 00001. Вт6)рым тактовым импульсом (2Т) , четыре младших разряда сумматора записываются на первый регистр сдвига 5, третьим тактовым импульсом (ЗТ) производится одновременный сдвиг содержимого первого и второго регистров сдвига 5 и б на один разряд вправо. Таким образом, первый регистр сдвига 5 окажется в нулевом состоянии, а единица младшего разряда перейдет в старший разряд второго регистра б сдвига. Четвертым тактом (4Т) нулевое состояние 4-х младших разрядов регистра 5 переписываются в регистр К). Во время 5 и б-го тактов опрашиваются двоичные разряды регистра 3 с весами 2 , 2 , 25 , 28 , i , 2 , 2 , 2 , о1 52- -,2Й ,29 . f . t t , f t I t Т .-е. в соответствии с табл.1. Одновременно, выходы формирователя подключаются через шины .слагаемого А на первую группу входов сумматора, на вторую группу входов поданы выходы регистра 10, как и ппи опросе разряда регистра 3 с весом 2. Если . предположить, что все эти разряды равны единицам , то на выходе формирователя будет код 1111, т.е. 15 единиц выраженных двоичным кодом. Шестым тактовым импульсом содержимое сумматора переписывается в первый регистр 5 сдвига. Седьмым производится сдвиг содержимого регистров 5 и 6, т.е. содержимое регистра 5 равно .11100, а регистра б - ООН. Восьмым тактом содержимое 4-х младших разрядов регистра 5 переписывается в регистр 10. Следовательно, содержимое регистра 10 равно 1110. Во время 9 и 10-го тактовых иМпульсов опрашиваются разряды в столбце с.,- 2 первого разряда табл.1,, Производится сложение содержимого регистра 10 и выхода формирователя. Результат записывается на регистр 5, Одиннадцатым тактом производится сдвиг регистров 5 и б, двенадцатым -запись.на регистр 1013-14т опрашивается столбец d|2 первого разряда и производится сложение содержимого регистра 10 с выходами формирователя. Четырнадцатым тактом записывается результат сложения на регистр 5. Пятнадцатым тактом производится сдвиг регистров 5 и б. Шестнадцатым производится запись содержимого регистров 5 и 6 на регистры 10 и 7. Таким образом, по шестнадцатому тактоврму и.мпульсу на регистрах 7 и 10 имеем информацию о количестве единиц в преобразуемом числе, выраженное двоичным кодом, величина которой для 30-ти разрядного двоичного кода не превышает 143. Теперь остается выделить из общего количества единиц количество единиц, выраженное в двоично-десятичном коде. Эта операция выполняется следующим образом. Шифратор корректирующего кода 9 вырабатывает три старших разряда корректирующего кода а, Ь , с и три младших разряда bj, , со , do . Работа шифратора 9 поясняется таблицей интенсивности (табл.З). Входы шифратора постоянно подключены к выходам регистра 10. Во время 17 и 18-го тактов выходы старших разрядов корре тирующего кода, через шинй слагаемог Л подаются соответственно на входы AJ,, А и AJ сумматора, на входы 6 попрежнему поданы выходы регистра 10. Происходит сложение 4-х старших разр дов двоичного кода количества единиц со старшими разрядами корректирующег кода. В это же время на вход Р сумматора подается сигнал переполнения с выхода PQ блока 8, если содержимо регистра 7 больше или равно 10-ти, Результат сложения, который не превышает 140 единиц, т.е. выход Р сум матора равен О, записывается восемнадцатым тактом на регистр 5, пос ле которого выходы регистра 10 отклю чаются от шин слагаемого В . На время 19-23-го тактов подключа ются выходы регистра 7 через шины слагаемого & на входы В сумматора. На время 19-20-го тактов, через шины слагаемого Л, на входы А , А, и А cyMMaToi a подаются соответственно мл шие разряды корректирующего кода шиф ратора 9. Происходит сложение содержимого регистра 7 с младшими разряда ми корректирующего кода. Информация четырех младших разрядов сумматора двадцатым тактом записывается на регистр б, а выход Pj сумматора записы Бается в старший разбяд регистра 5. Двадцать первыг тактом содержимое ре гистров 5 и б переписывается на регистры 10 и 7. Эта информация на регистре 10 используется в следующем цикле, а информация на регистре 7 подвергается окончательной корректировке, т.е. происходит сложение содержимого регистра 7 с выходом схемы 8. Для чего, на время 22-23-го такто подаются выходы Ь , с , d блока 8 через шины слагаемого А соответственно на входы А, Aj и AJ сумматора. Сумма, записывается 23 тактом на регистр 6. Выход Pg сумматора записывается в старший разряд регистра 5 этим же тактом в случае, если в это время он находится в единичном состоянии. Двадцать четвертым тактом содержимое регистра б переписывается на регистр 7. Эта информация представляет собой двоично-десятичный код тетрады единиц. Последующие разряды вырабатываются аналогично, только опрашиваемые разряды регистра соответствуют табл.1. Преобразование дополнительного двоичного кода производится аналогично прямому, за исключением того, что на вход формирователя 3 подается инверсный код преобразуемого числа и знак опрашивается во время 1-2Т первого цикла. Для пояснения работы преобразователя в режиме преобразования двоичного кода в двоично-десятичный рассмотрим пример преобразования двоичного кода 0.01101100111111 (табл. 4). Положительный эффект предлагаемого изобретения заключается в расширении функциональных возможностей, т.е. в возможности на одном устройстве преобразовывать как двоичные коды в двоично-десятичные, так и двоично-десятичнйе в двоичные во всей области представления дейГствительных чисел. Оборудование и потребляемая мощность сократятся при этом примерно вдвое, что влечет к повышению надежности устройства. Время преобразования двоичного кода в двоичнодесятичный сократится f в 20 раз. Предлагаемый преобразователь кодов выполняет операцию преобразования ЗО-ти разрядного двоичного кода в двоично-десятичный за 50 мкс, .а 9-ти разрядный двоично-десятичный код в двоичный за 25 мкс при частоте задающего генератора 5 мГц. Формула изобретения Преобразователь кодов, содержащий регистр входного кода со знаковым разрядом, распределитель импульсов, сумттор, регистр и формиров,атёль поразрядных эквивалентов, информационные входы которого соединены с выходами регистра входного кода, а выходы соединены с первой группой входов сумматора, вторая группа входов которого соединена с выходами регистра, управляющие входа формирователя и регистра подключены к выходам распределителя импульсов, .отличающийс я тем, что, г целью расширения фуНВДйОйаленыз йВзмэжностей за счет выполнения преоб -|5Ш§ВШ 1йй дйЬйчнбго т дДа в двбйчнодёбятичный и двоично-десяти 1ного кода в двоичный во всей области представления действ ительных чясеп, он содержи первый регистрСдвига сумг матора, второй регистр сдвига сумматора, дополнительный регистр, блок Коррекции по переполнению и шифратор коррёктируюйегО йода; вkbjfta которого соединены с выходами регистра, а выхо да подключены к первой группе входов сумматора, входы второго регистра ТЭд йМ -СУмматора и четыре входа млад ййГхраэ эяйов первого регистра сдвига. - СУМйатбра; со-единены с соответству,ю-. Шими выходами сумматора, выход net./нреа со старшего {Разряда сумматор подключен ко входу стаЕмаего разряда первого регистра сдвига сумматора, последовательный вход второго регист ра сдвига сумматора соединен с внхЪдом младшего разряда первого регист расдвига сумматора, выходы первого регйстра сдвига сумматора соединены со входайи регистра, выходы SToiporo регистра сдвига сумматора соединены Со входами дополнительного регистра.

TKj SSfSiMj-s i: -Г..

,

-5 б 1чавк&Ьчл 1 , f выход которого подключей ко второй труппе входов сумматора, выходы трех старших разрядов дополнительного регистра соединены с первым,вторым и третьим входом блока коррекции по переполнению, четвертый вход которого подключен к выходу CTapiuero разряда первогорегистра сдвига сумматора, а выходы блока коррекции по переполнению подключены, к первой группеf входов сумматора, дополнительный выход блока коррекции по переполнению подключен к дополнительному входу сумматора, управляюиие входы шифратора корректируюиего кода, бЛока коррекции по переполнению, регистров сдйига сумматора и дополнительного регистра, соединены с выходами распределителя импульсов. Источники информации, принятые во внимание при экспертизг 1,Авторское свидетельство СССР №228334, кл.,С Об F 5/02, 1968. 2,Авторское свидетельство ССС № 543934, кл.С Об Р 5/02, 1974. 3,Авторское свидетельство СССР по заявке № 2136416,кл.С 06 F 5/02, 1977 (прототип) .

Авторы

Даты

1980-06-30—Публикация

1978-03-29—Подача