Изобретение относится к вычислительной технике и предназначено для воспроизведения по известным кодам полярных координат ( Ч, I) измеряемой величины кодов ее прямоугольных координат (х,Ч) и наоборот.

Известны устройства для преобразования координат аналоговые или гибридные 1 .

Известные цифровые устройства имеют недостаточные функциональные возможности .

Из известных устройств наиболее близким по технической сущности к изобретению является цифровой преобразователь координат 2J.

Преобразователь содержит два счетчика кодов прямоугольных координат, схему переноса, реверсивный счетчик, блок управления,, первый ключ,генератор импульсов, шифратор дискретных . значений функций (sin p)j) и (cosjbj), реверсивный счетчик фазы, второй и ч третий ключи, цифровой компаратор, различитель квадратов, датчик полярной координаты If, датчик полярной координаты z, датчик прямоугольной координаты -j и датчик прямоугольной координаты X.

Работает преобразователь в двух режимах.

В режиме преобразования полярных координат (f, z ) в прямоугольные координаты (ч , х7 ив режиме преобразования прямоугольных координат () в полярные координаты (if,z).

Функционирование преобразователя в обоих режимах основано на решении

10 системы уравнений

i -Zsin4

(1) U Zcos4.

В первом режиме т неизвестные х

15 и s - преобразователь непосредственно решает одновременно оба уравнения системы Ш , преобразованной в систему уравнений

S I Z/s-lnM

20

(2) l(KM zfcos /

путем преобразования кода Z в числоимпульсный (унитарный) код (чИК) поступающий на оба множительных бло25ка, на выходе первого из которых вырабатывается код ЧИК (tf), а на выходе второго - код ЧИК (х ). Импульсы ЧИК (v) и ЧИК (к ) подсчитываются соответственно счетчиками () и «)

Во втором focHOBHOM режиме работ ре ление системы уравнений (1 - неиз1вестные Чиг. - производится путем доиска такого угла {,| V, при котором

(hMiiv p KU|.|cosp )rv,aiK-- (3)

Однако в этом режиме преобразователь имеет, низкое быстродействие, обусловленное низким коэффициентом использования оборудования (счетчики ф нкционируют только как регистры, а |множительные блоки работают последс|вательно) , а также тем, что решение систе1« уравнений (1) основано нй поиске максимума левой части вырЦження (3).

i Действительно, анализ работы преос разователя показывает, что даже при применении в нем для нахожденця угла принципов гшгоритма поразР5 цного кодирования максимальная дл1ительность цикла преобразователя (ti+1) - разрядных ПР51МЫХ кодов у и X в {.И+2) - разрядный код Ц и п-разpfодиый код Z имеет значительную величину, т.к.

(

X

(4)

где TI

-длительность цикла прецпргобразования прототипа;

-коэффициент, обусловленный .математическим алгоритмом работы преобразователя, основанном на выражении (3) ,

-обусловлен низк1( коэффициентом использования оборудования;

-период повторения импультисов генератора;

- длительность времени воср-произведения шифратором функций() и (coefSjOЦель изобретения - повыиеииа быстродействия преобразователя.

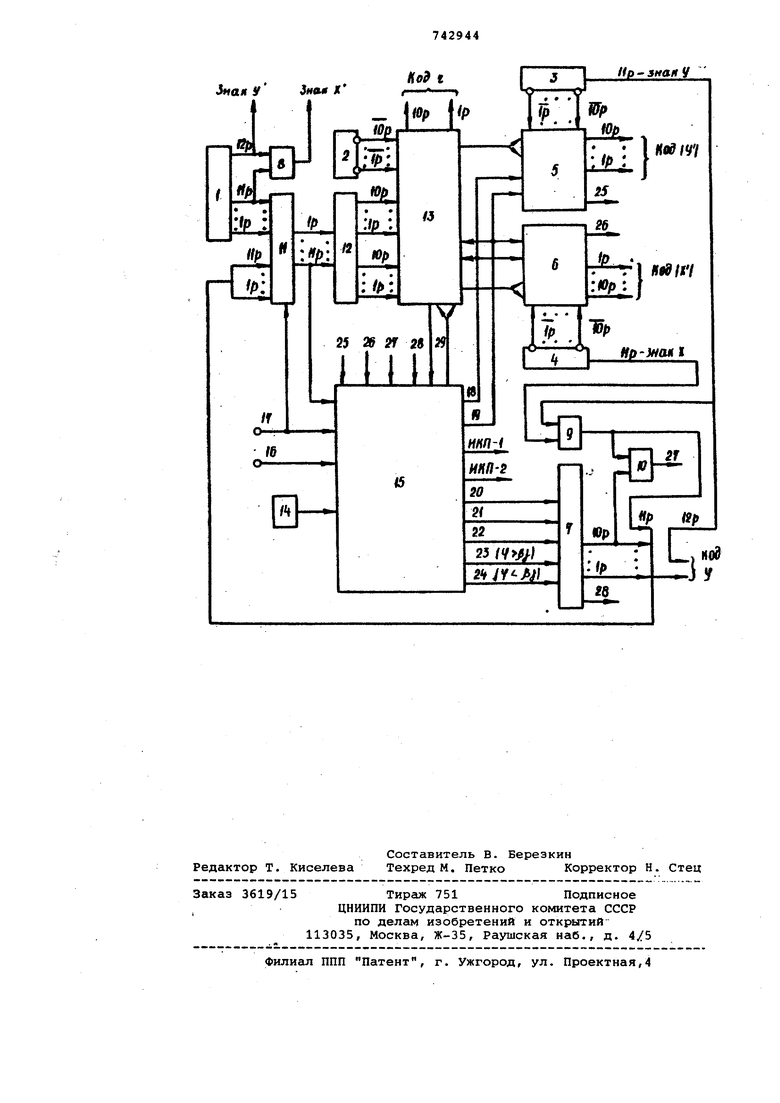

Для достижения поставленной цели цифровой преобразователь координат, содержащий первый и второй резисторы прймоугольных координат, постоянный запоминающий блок тригонометрических коэффициентов, блок управления и генератор импульсов, вход которого подключен к первому входу блока управления.

суммавведены

три

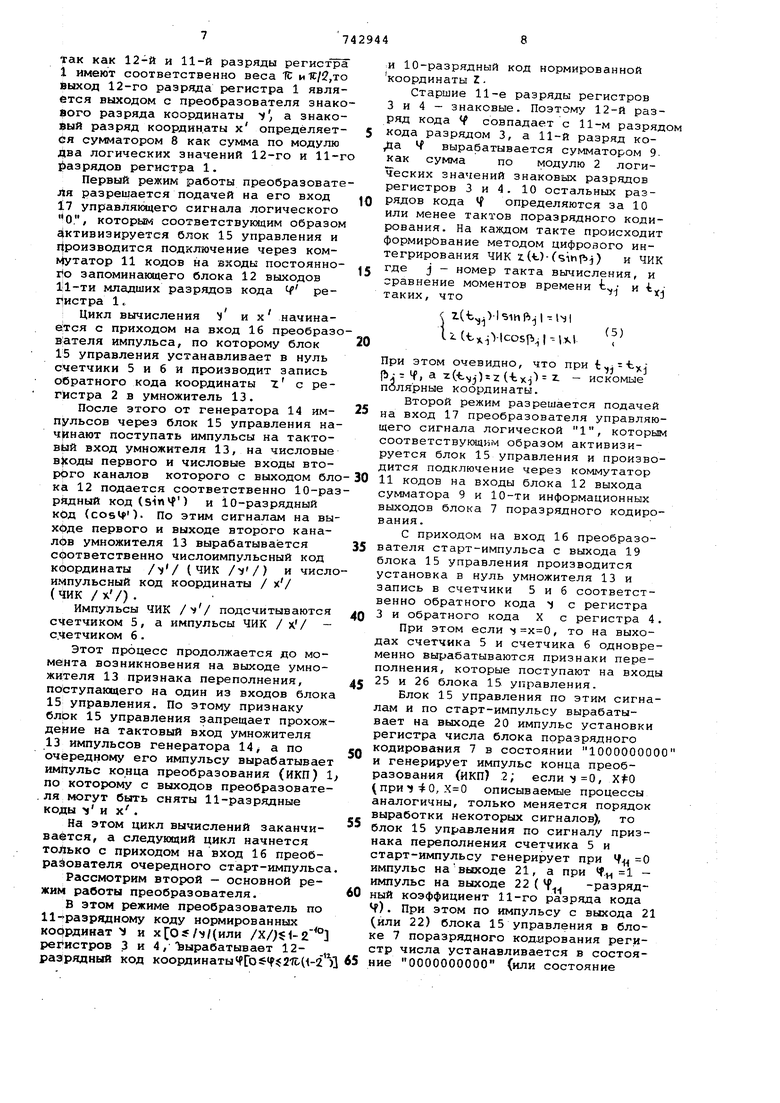

ToJ)a, коммутатор кодов , умножител блок поразрядного кодирования, причем вхдды первого сумматора подключены к выходам двух старших разрядов первого регистра полярных координатой, входы второго сумматора - к выходам знаковых разрядов первого и второго регистров прямоугольных координат, входы третьего сумматора к ВЫХОДУ старшего разряда блока поразрядного кодирования, выходы всех, кроме старшего, рвсзрядов первого регистра полярных координат подклю«е 4|ы к первой гру ппе входов комму таiTopa кодов,вторая группа входов Ьсоторого соединена с выходом второго сумматора и с выходами блока поразрядного кодирования, а выходы подключены ко входам постоянного запоминающего блока тригонометрических коэффициентов, первая и вторая группа выходов которого соединена соответственно с первой и второй группой входов умножителя, третья группа входов которого подключена к выходам второго регистра полярных координат, первый и второй импульсные выходы которого подключены к счетным входам соответственно первого и второго счетчиков прямоугольных координат, разрядные входы которых подключены к выходам первого и второго регистров прямоугольных координат соответственно, второй вход блока управления подключен к входу запуска преобразователя, третий вход блока управления соединен с входом признака режима преобразователя и с управляющим входом коммутатора кодов, четвертый вход - с выходом старшего разряда коммутатора кодов, пятый и шестой входы блока управления соединены с выходами переполнения первого и второго счетчиков прямоугольных координат,соответственно, седьмой вход - с выходом третьего сумматора, восьмой вход - с управляющим выходом блока поразрядного кодирования, девятый вход блока управления подключен к выходу переполнения умножителя, тактовый вход которого соединен с первым выходом блока управления,вход записи умножителя соединен со входом установки нуля счетчиков прямоугольных координат и со вторым выходом блока управления, третий выход которого соединен со входом установки нуля умножителя и входами записи счетчиков прямоугольных координат, четвертый, пятый и шестой выходы блока управления подключены соответственно к первому, второму и третьему установочным входам блока поразрядного кодирования, первый и второ информационные входы которого подключены соответственно к седьмому и восьмому выходам блока управления На чертеже приведена структурная схема цифрового преобразователя координат. Цифровой преобразователь координат содержит регистр 1 12-разрядного кода координаты Ч ;регистр 10-разрядного кода координаты z , регистр 3 11-разрядного прямого код координаты N и регистр 4 11-разрядного прямого кода координаты X,счетчик 5 координаты у , подключенный информационными входами к выходс1М кода J регистра 3, счетчик 6 координаты х , подключенный разрядными входами к выходам кода (х) регистра 4р блок 7 поразрядного кодирования. -сумматор 8, подключенный к выходам двух старших разрядов регистра 1, сумматор 9, подключенный к выходам знаковых разрядов регистров 3 и 4, сумматора 10, у котЬрого первый вход соединен с выходом сумматора 9, а второй - с выходом старшего разряда блока 7 поразрядного кодирования, коммутатор 11 кодов,постоянный запоминающий блок 12 тригонометрических коэффициентов, запрограммированный на воспроизведение синуса и косинуса и подключенный через коммутатор 11 кодов к выходам 11-ти младших разрядов регистра 1 и к выходу сумматора 9 и информационным выходсм блока поразрядного кодирования 7,дву канальный умножитель 13, у которого информационные входы соединены с выходами регистра 2, числовые входы первого и числовые входы второго ка налов подключены соответственно к выходам синуса и к выходам косинуса постоянного запоминающего блока 12, а выход первого и выход второго каналов подключены соответственно к суммирующему входу счетчика 5 и к суммирующему входу счетчика 6, гене ратор 14 импульсов, блок 15 управления, вход 16, подключенный к вход запуска блока 15 управления и вход 17 признака режима/ подключенный к управляющему входу коммутатора 11 кодов и к одному из управляющих вхо дов блока 15 управления, другой управляющий вход которого соединен с выходом 11-го разряда коммутатора 1 кодов, при этом у блока 15 управления выход 18 соединен с входами установки в нуль счетчиков 5 и 6 и со входом записи умножителя 13, выход 19 - с входами записи счетчиков 5 и 6 и входом установки в нуль умножителя 13, выход 20 - с первым установочным входом блока 7 поразрядного кодирования,два других уста новочных входа которого подключены к выходам 21 и 22 блока 15 управлен у которого выход 23 импульса (47pj) и выход 24 импульса ( Ч р ) подключе к информационньп входам блока 7 поразрядного кодирования)причем у бло ка 15 управления вход 25 соединен с выходом признака переполнения счетчика 5, вход 26 - с выходом при нака переполнения счетчика 6,вход 27 - с выходом сумматора 10,вход 28 с выходом признака 11-го такта вычи ления блока 7 поразрядного кодирова ния, а вход 29 псцдключен к выходу пр нака переполнения умножителя 13,так вый вход которого соединен через бло 15 управления с выходом генератора 14 импульсов. Преобразователь выполнен на элеюнтной базе, триггеры которой переключаются в моменты после окончания импульсов на их синхронизирующих входах. Регистры 1-4 представляют собой обычные регистры, прием информации в которые разрешается только после окончания цикла преобразования. Счетчики 5 и 6 выполнены как обычные счетчики, имеющие разрядные входы записи в них начальных условий. Блок 7 поразрядного кодирования содержит 11-тактовый распределитель импульсов, схему управления поразрядным кодированием и 10-разрядный регистр. Распределитель импульсов синхронизирует работу схемы управления поразрядным кодированием, которая по импульсу (f 7 (Ъ) или по импульсу () осуществляет соответствующим образом переключение триггеров регистра. Каждый из сумматоров 8-10 реализует операцию суммирования по модулю два двух логических переменных. Двухканальный умножитель 13 представляет собой множительный блок, реализующий одновременное умножение параллельного кода первого числа (кода/sinpj/) и параллельного .кода второго числа (кода /cospj/) на об-. дий меняющийся сомножитель ), представленный на тактовом входе умножителя 13, числоимпульсным кодом. На выходам умножителя 13 первое и второе произведения представлены в чнслоимпульсных кодах. При этом умножитель 13 содержит 10-разрядный счетчик - регистр с параллельным переносом, имеющий информационные входы для записи на него обратного кода общего фиксированного сомножителя г и две 10-разрядные схемы двоичных умножителей две схемы поразрядного умножения со схемами или). Работой двоичных умножителей управляет счетчик. Преобразователь работает в режиме вычисления прямоугольных координат s и X по известным полярным координатам и Z. и в режиме вычисления полярных координат ч и 2/ по известным прямоугольным координатс1м м и X. Математический алгоритм работы преобразователя в каикдом из режимов основан на решении системы уравнений Ц) ив каждом из режимов преобразователь работает циклически. Рассмотрим первый режим работы преобразователя. В этом режиме преобразователь по 12-разрядному коду координаты 2ttn-2) регистра 1 и 10разрядному коду, нормированной координаты ,()l регистра 2 вырабатывает прямые 11-разрядные коды нормированных координат их, у которых 11-е разряды - знаковые. Так как 12-й и 11-й разряды регистр 1 имеют соответственно веса 1C и1С/,т выход 12-го разряда регистра 1 явля ется выходом с преобразователя знак вого разряда координаты ч , а знако вый разряд координаты х определяет 3я сумматором 8 как сумма по модулю два логических значений 12-го и 111Ьазрядов регистра 1. Первый режим работы преобразоват ля разрешается подачей на его вход 17 управляющего сигнала логического О, которым соответствующим образо Активизируется блок 15 управления и г|роизводится подключение через комМутатор 11 кодов на входы постоянно г1о запоминающего блока 12 выходов 11-ти младших разрядов кода W рег истра 1. Цикл вычисления 1 их начинается с приходом на вход 16 преобраз вателя импульса, по которому блок 15 управления устанавливает в нуль счетчики 5 и 6 и производит запись обратного кода координаты z с регистра 2 в умножитель 13. После этого от генератора 14 импульсов через блок 15 управления на поступать импульсы на тактовМй вход умножителя 13, на числовые вХоды первого и числовые входы втоЕИэго кансшов которого с выходом бл на 12 подается соответственно 10-ра рядный код(51пЧ) и 10-разрядный кОд (cosif). По этим сигналам на вы ходе первого и выходе второго канаЛ0В умножителя 13 вырабатывается сфответственно числоимпульсный код координаты (ЧИК /ч/) и числ импульсный код координаты / х/ (ЧИК / х/) . Импульсы ЧИК /v/ подсчитываются счетчиком 5, а импульсы ЧИК / х/ счетчиком 6. Этот процесс продолжается до момента возникновения на выходе умножителя 13 признака переполнения, поступающего на один из входов блока 15 управления. По этому признаку блок 15 управления запрещает прохождение на тактовый вход умножителя 13 импульсов генератора 14 а по очередному его импульсу вырабатывает имПульс конца преобразования (ИКП) 1 по которому с выходов преобразовате. ля могут быть сняты 11-разрядные коды и х . На этом цикл вычислений заканчивается, а следующий цикл начнется тойько с приходом на вход 16 преобрайователя очередного старт-импульса Рассмотрим второй - основной режим работы преобразователя. В этом режиме преобразователь по Поразрядному коду нормированных координатS и (или /Х/;$1-2 ° регистров 3 и 4, вырабатывает 12разрядный код координаты fГоsf SILli-i и 10-разрядный код нормированной координаты Z. Старшие 11-е разряды регистров 3 и 4 - знаковые. Поэтому 12-й разряд кода Ч совпадает с 11-м разрядом кода разрядом 3, а 11-й разряд коfia Ч вырабатывается сумматором 9. как сумма по модулю 2 логических значений знаковых разрядов регистров 3 и 4. 10 остальных разрядов кода V определяются за 10 или менее тактов поразрядного кодирования. На каждом такте происходит формирование методом цифрового интегрирования ЧИК z{U-fsihp.j) и ЧИК где j - номер такта вычисления, и сравнение моментов времени t.- и 4, таких, что 2.()И1)| i(tx V|cosp.|--lxl При этом очевидно, что при fc.j-tyj (b., а z(t,vj) z (-txi) 2. - искомые полярные координаты. Второй режим разрешается подачей на вход 17 преобразователя управляющего сигнала логической 1, которым соответствующим образом активизируется блок 15 управления и производится подключение через коммутатор 11 кодов на входы блока 12 выхода сумматора 9 и 10-ти информационных выходов блока 7 поразрядного кодирования. С приходом на вход 16 преобразователя старт-импульса с выхода 19 блока 15 управления производится установка в нуль умножителя 13 и запись в счетчики 5 и б соответственно обратного кода ч с регистра 3 и обратного кода X с регистра 4. При этом если , то на выходах счетчика 5 и счетчика б одновременно вырабатываются признаки переполнения, которые поступают на входы 25 и 26 блока 15 управления. Блок 15 управления по этим сигналам и по старт-импульсу вырабатывает на выходе 20 импульс установки регистра числа блока поразрядного кодирования 7 в состоянии 1000000000 и генерирует импульс конца преобразования (ИКП) 2; если 0, (причло, описываемые процессы аналогичны, только меняется порядок выработки некоторых сигналов), то блок 15 управления по сигналу признака переполнения счетчика 5 и старт-импульсу генерирует при f 0 импульс навыходе 21, а при 1 импульс на выходе 22 ( -разрядный коэффициент 11-го разряда кода Ч). При этом по импульсу с выхода 21 (или 22) блока 15 управления в блоке 7 поразрядного кодирования регистр числа устанавливается в состояние 0000000000 (или состояние

1111111111, а распределитель импульсов - в состояние 11-го такта вычислений.

Через некоторое время-fe , требуемое блока 12 для воспроизведения кодов /SinЧ/ и /соаЧ/, блок 15 управления начинает пропускать на тактовый вход умножителя 13 импульсы генератора 14. В результате этого на выходе второго канала умножителя |13 вырабатываются импульсы ЧИК /X/, которые подсчитываются счетчиком 6. Как только на выходе счетчика 6 вырабатывается признак переполнения, то блок 15 управления запрещает прохождение на тактовый вход умножителя 13 импульсов генератора 14, а по очередному импульсу генератора :14, признаку переполнения счетчика 6 и признаку 11-го такта, вырабатываемому на выходе 28 блока поразрядного кодирования 7 генерирует импульс ИКП 2 .

Таким образом, после окончания вычислений с информационных выходов преобразователя 13 будет сниматься код 2./Х/, если Фо и ХФО, то счетчики 5 И 6 признаков переполнения не вырабатывают, а блок управления 15 на выходе 20 вырабатывает импульс, устанавливающий в блоке поразрядного кодирования 7 регистр числа в состоянии 1000000000,а распределитель импульсов в состояние первого такта вычислений.

Через время t., требуемое блоку 12 для воспроизведения кодов /si«p-j/ и /cosp /, блок 15 управления начинает пропускать на тактовый вход умножителя 13 импульсы генератора 14. Поэтому умножитель 13 на выходе первого канала вырабатывает числоимпульсный код 4HKfzW/SiHp (3, на выходе второго канала - ЧИК г()/cos 13. Импульсы ЧИКСг)|51И|Ъ З подсчитываютс счетчиком 5, в который по старт-импульсу был записан обратный код /V/, а импульсы ЧИК иШ/созрн подсчитываются счетчиком 6, в который по старт-импульсу был записан обратный код /X/.

В результате этого если , то так как )/ /cosp)/, на выходах счетчиков 5 и 6 сигналы признаков переполнения вырабатываются одновременно. По этим сигналам блок 15 управления затратит прохождение на тактовый вход умножителя 13 импульсо генератора 14, а по очередному импулсу генератора 14 и признакам переполнения счетчиков 5 и б вырабатывает импульс ИКП 2, если /j/ 7/Х/ (или ), то первым вырабатывается признак переполнения на выходе счетчика б (или на выходе счетчика 5). По этому признаку блок 15 управления запретит прохождение на тактовый вхо умножителя 13 импульсов генератора

14, и по очередному импульсу генератора 14 выработает на выходе 19 импульс , по которому производится установка в нуль умножителя 13 и запись в счетчики 5 и 6 соответственно обратного кода с регистра 3 и обратного кода /X/ с регистра 4, а также выработает на выходе 23 им(тульс f и на выходе 24 (или наоборот, если /Ч/ /ХД который поступает на соответствуквдий вход блока поразрядного кодирования 7, в котором в регистре числа установится код, соответствующий углу (bj . После окончания импульса на выходе 23 и 24 блока 15 управ5ления в блоке 7 поразрядного кодирования распределитель импульсов установится в состояние 2-го такта вычисления. Через время .Ъф, требуемое блоку 12 для воспроизведения кодов

0 /sin /cosp)2/, блок 15 управления снова начинает пропускать на тактовый вход умножителя 13 импульсы генератора 14 и т.д. Если в. очередном J-OM такте вычисления (J 2,3....,

5 10) одновременно вырабатываются признаки переполнения счетчиков 5 и б; то по этим сигналам блок 15 управле1ния запретит прохождение на тактовый вход умножителя 13 импульсов гене0ратора 14 выработает сигнгш ИКП 2. Если ни в одном из этих тактов признаки переполнения счетчиков 5 и б одновременно не выработаются,то после этого блок поразрядного кодирования 7 выработает признак 11-го такта

5 вычисления, который с его выхода поступит на вход 28 блока 15 управления. В 11-м такте вычисления на тактовый вход умножителя 13 поступит очередная серия импульсов генерато0ра 14.

Причем в этом такте ..вычисления импульсы генератора14 будут поступать на умножитель 13 до тех пор, пока не выработается признак пере5полнения счетчика 5 (или счетчикарегистра б), так как при /X/ (или /1/ /Х/ сумматором 10 вырабатывается признак /X/ (или / ч / /VX который с выхода сумма0тора 10 поступает.на вход 27 блока 15 управления. Поэтому в 11-м такте вычислений по признаку переполнения 5 при /ч/ /X/ (или счетчика б при ) и очередному импульсу

5 генератора 14 блок 15 управления вырабатывает сигнал ИКП 2, по которому может производиться съем с преобразователя кодов f и-г. На этом цикл вычислений заканчивается, а

0 следукмций цикл начнется с приходом на вход 16 преобразователя очередного старт-импульса.

Заметим, что окончание 11-го такта по признаку переполнения счетчика,

5 в который ранее был записан обратHijjM кодом больший из модулей или /X/, сделано с целью уменьшения относительной ошибки вычисления координаты Z. Дело в том, что если 1 ч то вычисление координаты 7 основывается на выполнении лишь одного яз равенства системы (5, а абсолютные ошибки АХ и л%4пЧ «& С05 ч.

Максимальная длительность цикла П1| еобраэования (ti +1 ) - разрядных к4дов X ич в («+2) - разрядный код Ч|И и - разрядный код Z будет

Ч « |()121С2 где к 0,±1,±2..., а длительность цикл преобразования определяется выражением. , (6)

где tf., - период повторения импульсов генератора 14; ф - время, требуемое блоку 1 для воспроизведения функции синуса и косинуса. Сравнивая выргикения (4) и (б) по.лучим: - J-T

..г 3 ii,np.l

Прложительный эффект изобретения закт ючается в том, что данный преобразоултвль имеет более высокое быстродействие по сравиению с известным (т1ем более, что оценка (7) получена с |учетом возможности применения в прйототипе поразрядного кодирования, существенно повьшающих его быстродест;вия).

Применение изобретения позволит повысить скорость обработки информации .

Формула изобретения

Цифровой преобразователь коордиHair, содержащий первый и второй регистры прямоугольных координат,первый и второй регистры полярных коор инат, первый и второй счетчики пр 1моугольных координат, постоянHBJt запоминающий блок тригонометриче :ких коэффициентов, блок управления и генератор импульсов, выход KOtoporo подключен к первому входу .блока управления, отличаюц И и с я тем, что, с целью повышения быстродействия преобразователя, он содержит три сумматора, коймутатор кодов, умножитель,блок по1 азрядного кодирования,причем входы первого сумматора подключены к Доходам двух старших разрядов регистра полярных координат входы второго суммйтора - к выходам знаковых разрядов первого и йторого регистров прямоугольных кофрдинат, входы третьего суммато| а - к выходу второго сумматора и выходу старшего разряда блока

поразрядного кодирования, выходы всех, кроме старшего, разрядов первого регистра полярных координат подключены к первой группе входов коммутатора кодов, вторая 5 группа входов которого соединена с выходом второго сумматора и с выходами блока поразрядного кодирования, а выходы подключены ко входам, постоянного запоминающего

Q блока тригонометрических коэффициентов, первая и вторая группа выходов которого соединена соответственно с первой и второй группой входов умножителя, третья группа входов которого подключена к выходам второго регистра полярных координат, первый и второй импульсные выходы которого подключены к счетным входам соответственно первого и второго счетчиков прямоугольных координат,разрядные

0 входы которых подключены к выходам первого и второго регистров прямоугольных координат соответственно, второй вход блока управления подключен к входу запуска преобразователя,

5 третий вход блока управления соединен с входом признака режима преобразователя и с управляющим входом коммутатора кодов, четвертый вход - с выходом старшего разряда коммутатора кодов, пятый и шестой входы блока управления соединены с выходами переполнения первого и второго счетчиков прямоугольных координат соответственно, седьмой вход - с выходом третьего сумматора, восьмой вход - с управляющим выходом блока поразрядного кодирования, девятый вход блока управления подключен к выходу переполнения умножителя,тактовый вход которого соединен с первым выходом блока управления,вход записи умножителя соединен со входами установки нуля счетчиков прямоугольных координат и со вторым вы. ходом блока управления, третий выход которого соединен со входом установки нуля умножителя и входами записи счетчиков прямоугольных координат, четвертый, пятый и шестой выходы блока управления подключены соответственно к первому, вгоро: и третьему установочным входам блока поразрядного кодирования, первый и второй информационные входы которого подключе«ы соответственно к седьмому и восьмому выходам блока управления.

Источники информации, принятые во внимание при экспертизе

1.Патент США № 395187, 0 кл. 235-186, 1976.

2.Авторское свидетельство СССР 453690, кл. G06 F 7/38, 1972 (прототип). Знал X Ко9 t fp Нр-знанУf 10f LlLl Под 1ЧЧ Яв9/г/ lail яр-мм I 2 -) ной

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой преобразователь координат | 1985 |

|

SU1290307A1 |

| Цифровой преобразователь координат | 1979 |

|

SU873239A1 |

| Цифровой преобразователь координат | 1979 |

|

SU842801A1 |

| Цифровой преобразователь координат | 1985 |

|

SU1257638A1 |

| Цифровой преобразователь координат | 1983 |

|

SU1141404A1 |

| Цифровой преобразователь координат | 1983 |

|

SU1163322A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1444958A1 |

| Цифровой преобразователь полярных координат в прямоугольные координаты | 1987 |

|

SU1441390A1 |

| Цифровой функциональный преобразователь | 1988 |

|

SU1543401A1 |

| Синусно-косинусный функциональный преобразователь | 1981 |

|

SU970357A1 |

Авторы

Даты

1980-06-25—Публикация

1977-08-01—Подача