1

Изобретение относится к Импульсной технике.

Известен селектор импульсов по длительности, содержащий источник аналоговых входных импульсов, первую цепь, соединенную с источником, формирующую первый сигнал, когда амплитуда одного из входных импульсов превышает первую опорную амплитуду. Вторая цепь, соединенная с источником входных импульсов, формирует второй сигнал, когда один из входных импульсов превышает вторую опорную амплитуду, отличающуюся от первой. Третья цепь, соединенная со второй цепью, преобразует второй сигнал в двоичное число. В результате вырабатывается третий сигнал, когда это число больше опорного значения минимальной длительности импульса, и четвертый сигнал, когда это число меньше опорного значения максимальной длительности импульса. Четвертая цепь, соединенная с первой и третьей цепями, реагирует на одновременно наличие первого, третьего и четвертого сигнала с целью формирования выходного импульса. На выходе устройства импульсы появляются только в том случае.

если амплитуда и длительность входного сигнала лежит в заданных пределах 1.

Однако известные устройства не обеспечивают выделение импульсных сигналов прямоугольной формы на фоне биполярной 5 помехи.

Наиболее близким по технической сущности к заявленному является селектор импульсов по длительности, содержащий источник опорного напряжения выход которого соединен с первым входом блока сравнения напряжений, второй вход которого соединен со входной щиной, а выход подключен к первому входу одного логического элемента И, второй вход которого соединен со вторым входом второго логического элемента И и с выходом источника синхроимпульсов, третьи входы упомянутых логических элементов И соединены соответственно с выходами блоков сравнения кодов, первые входы которых подключены к выходу регистра, причем второй вход одного блока сравнения кодов соединен с выходом счетчика импульсов, вход которого подключен к выходу первого логического элемента И, а выход каждого блока сравнения кодов через

формирователь импульсов соединен с одним из входов триггера 2.

Недостатком данного селектора является недостаточная помехоустойчивость.

Цель изобретения - увеличение помехоустойчивости.

Поставленная цель достигается тем, что в селектор импульсов, содержащий источник опорного напряжения, выход которого соединен с первым входом блока сравнения напряжений, второй вход которого соединен со входной шиной, а выход подключен к первому входу одного логического элемента И, второй вход которого соединен со вторым входом второго логического элемента И и с выходом источника синхроимпульсов, третьим входом упомянутых логических сов, третьи входы упомянутых логических элементов И соединены соответственно с выходами блоков сравнения кодов, первые входы которых подключены к выходу регистра, причем второй вход одного блока сравнения кодов соединен с выходом счетчика импульсов, вход которого подключен к выходу первого логического элемента И, а выход каждого блока сравнения кодов через формирователь импульсов соединен с одним из входов триггера, введены дополнительный счетчик импульсов, два дополнительных логических элемента И, инвертор, детектор и два логических элемента ИЛИ, первые входы которых через детектор соединены с источником синхроимпульсов, вторые входы подключены перекрестно к выходам формирователей импульсов, а третий вход каждого соединен с выходом соответствующего дополнительного логического элемента И, первые входы дополнительных логических элементов И соединены с выходом источника синхроимпульсов, вторые входы подключены к выходам блоков сравнения кодов, третий вход первого дополнительного логического элемента И соединен с первым входом второго логического элемента И и через инвертор с выходом блока сравнения напряжений, третий вход второго дополнительного логического элемента И соединен с выходом блока сравнения напряжений, причем дополнительный счетчик импульсов включен между выходом второго основного логического элемента И и вторым входом второго блока сравнения кодов, а второй вход каждого счетчика импульсов соединен с выходом соответствующего логического элемента ИЛИ.

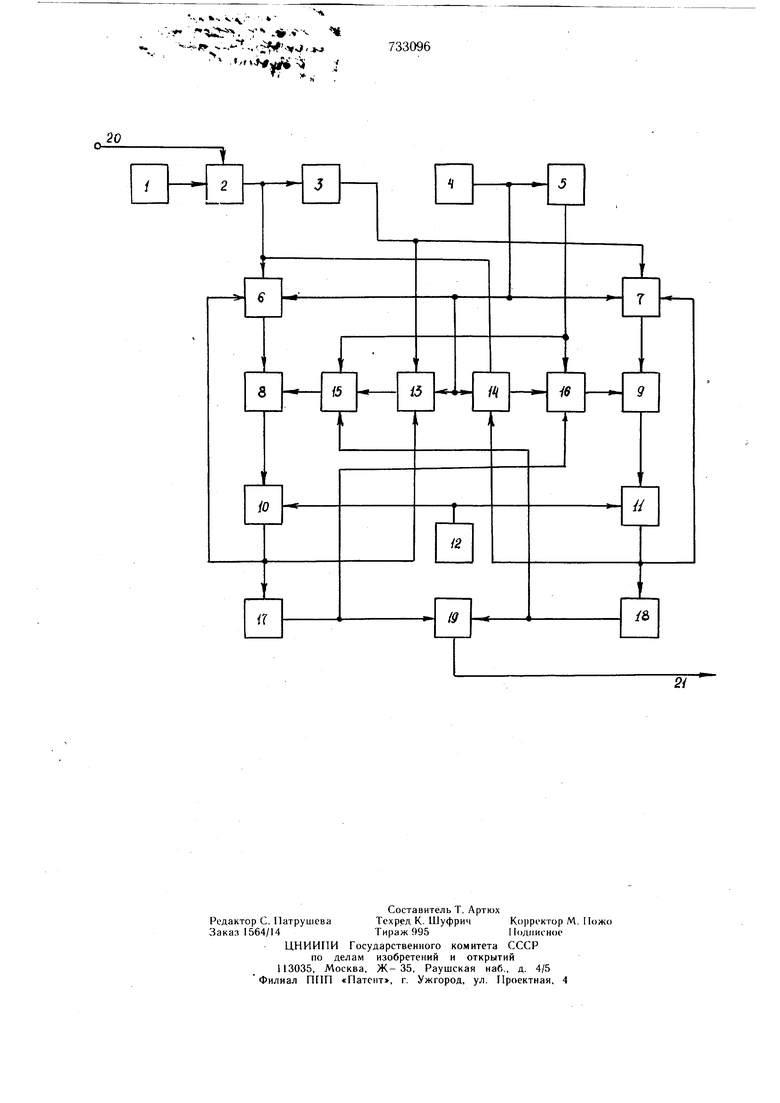

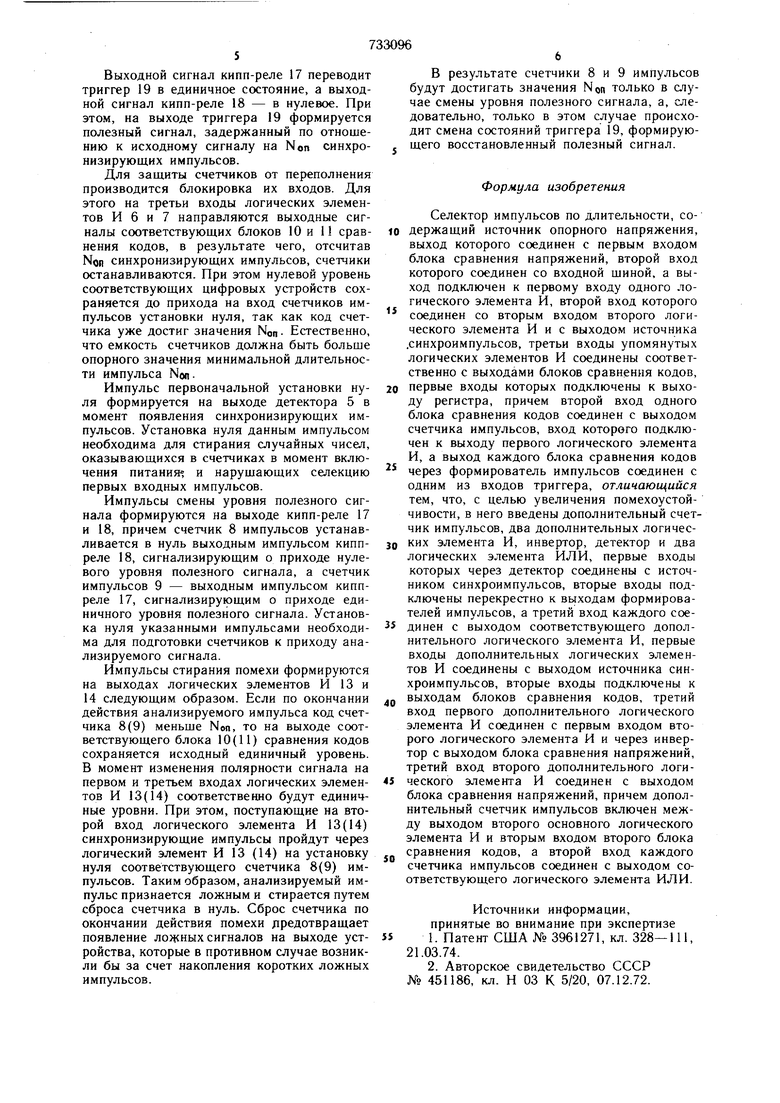

На чертеже приведена структурная электрическая схема описываемого селектора.

Селектор содержит источник 1 опорного напряжения, блок 2 сравнения амплитуд, инвертор 3, источник 4 синхроимпульсов, детектор 5, логические элементы И 6, 7, счетчики 8, 9 импульсов, блоки 10, 11 сравнения кодов, регистр 12, логические элементы И 13, 14, логические элементы ИЛИ 15,

16, формирователи импульсов например кипп реле 17, 18. триггер 19. Входной сигнал подан на входную щину 20, выходной сигнал снимается с выхода 21.

Селектор работает следующим образом. Входной сигнал, представляющий собой импульс прямоугольной формы (меандр), искаженный щумовой помехой, поступает на входную щину устройства, связанную с первым входом блока 2 сравнения амплитуд, на второй вход которого подается опорное напряжение Uon с выхода источника 1.

На выходе блока 2 сравнения амплитуд формируется сигнал, соответствующий единице, если входной сигнал Ue превышает опорное напряжение Uon и нулю при

j Uc Uon- В результате действия щумовой помехи этот сигнал содержит ложные импульсы обеих полярностей, причем ложные импульсы имеют отрицательную полярность во время следования полезного сигнала и положительную - при его отсутствии.

0 Выходной сигнал блока 2 сравнения амплитуд поступает на первый вход логического элемента И 6 и через инвертор 3 на первый вход логического элемента И 7. На вторые входы логических элеменгсж

5 И 6 и 7 направляются синхронизирующие импульсы источника 4 синхроимпульсов. Детектор 5 в момент появления синхронизирующих импульсов формирует сигнал начала работы устройства.

Сигналы, простробированные синхронн0 зирующими импульсами, поступают на сигнальные входы первого и второго счетчиков 8 и 9 импульсов соответственно.

Коды счетчиков 8 и 9 направляются на первые входы соответственно первого и второго блоков 10 и 11 сравнения кодов, на вторые входы которых поступает опорное значение минимальной.длительности импульса NOR с выхода регистра 12.

Если код счетчика 8 или 9 меньще опорного значения минимальной длительности импульса Non, то на выходе соответствующего блока 10 или 11 сравнения кодов будет единичный уровень, а если код счетчика больще или равен Non - нулевой уровень.

В момент перехода блоков 10 или 11 5 сравнения кодов из единичного состояния в нулевое на выходе соответствующего киппреле 17 или 18 формируется импульс, сигнализирующий о смене уровня полезного сигнала, причем на выходе кипп-реле 17 импульс сигнализирует о появлении полезного сигнала на входе устройства, а на вы юде кипп-реле 18 - о его окончании. За счет времени анализа длительности селектируемого сигнала, формирование импульсов на выходе кипп-реле 17 или 18 происхоДит с задержкой по отнощению к моменту смены уровня полезного сигнала. Эта задержка равна времени прохождения на вход счетчика 8 или 9 импульсов Non синхронизирующих импульсов.

Выходной сигнал кипп-реле 17 переводит триггер 19 в единичное состояние, а выходной сигнал кипп-реле 18 - в нулевое. При этом, на выходе триггера 19 формируется полезный сигнал, задержанный по отношению к исходному сигналу на Non синхронизирующих импульсов.

Для защиты счетчиков от переполнения производится блокировка их входов. Для этого на третьи входы логических элементов И 6 и 7 направляются выходные сигналы соответствующих блоков 10 и 11 сравнения кодов, в результате чего, отсчитав Non синхронизирующих импульсов, счетчики останавливаются. При этом нулевой уровень соответствующих цифровых устройств сохраняется до прихода на вход счетчиков импульсов установки нуля, так как код счетчика уже достиг значения Non Естественно, что емкость счетчиков должна быть больше опорного значения минимальной длительности импульса Non

Импульс первоначальной установки нуля формируется на выходе детектора 5 в момент появления синхронизирующих импульсов. Установка нуля данным импульсом необходима для стирания случайных чисел, оказывающихся в счетчиках в момент включения питания и нарушающих селекцию первых входных импульсов.

Импульсы смены уровня полезного сигнала формируются на выходе кипп-реле 17 и 18, причем счетчик 8 импульсов устанавливается в нуль выходным импульсом киппреле 18, сигнализирующим о приходе нулевого уровня полезного сигнала, а счетчик импульсов 9 - выходным импульсом киппреле 17, сигнализирующим о приходе единичного уровня полезного сигнала. Установка нуля указанными импульсами необходима для подготовки счетчиков к приходу анализируемого сигнала.

Импульсы стирания помехи формируются на выходах логических элементов И 13 и 14 следующим образом. Если по окончании действия анализируемого импульса код счетчика 8(9) меньше Non, то на выходе соответствующего блока 10(11) сравнения кодов сохраняется исходный единичный уровень. В момент изменения полярности сигнала на первом и третьем входах логических элементов И 13(14) соответственно будут единичные уровни. При этом, поступающие на второй вход логического элемента И 13(14) синхронизирующие импульсы пройдут через логический элемент И 13 (14) на установку нуля соответствующего счетчика 8(9) импульсов. Таким образом, анализируемый импульс признается ложным и стирается путем сброса счетчика в нуль. Сброс счетчика по окончании действия помехи лредотвращает появление ложных сигналов на выходе устройства, которые в противном случае возникли бы за счет накопления коротких ложных импульсов.

в результате счетчики 8 и 9 импульсов будут достигать значения Non только в случае смены уровня полезного сигнала, а, следовательно, только в этом случае происходит смена состояний триггера 19, формирующего восстановленный полезный сигнал.

Формула изобретения

Селектор импульсов по длительности, содержащий источник опорного напряжения, выход которого соединен с первым входом блока сравнения напряжений, второй вход которого соединен со входной шиной, а выход подключен к первому входу одного логического элемента И, второй вход которого соединен со вторым входом второго логического элемента И и с выходом источника .синхроимпульсов, третьи входы упомянутых логических элементов И соединены соответственно с выходами блоков сравнения кодов, первые входы которых подключены к выходу регистра, причем второй вход одного блока сравнения кодов соединен с выходом счетчика импульсов, вход которого подключен к выходу первого логического элемента И, а выход каждого блока сравнения кодов через формирователь импульсов соединен с одним из входов триггера, отличающийся тем, что, с целью увеличения помехоустойчивости, в него введены дополнительный счетчик импульсов, два дополнительных логических элемента И, инвертор, детектор и два логических элемента ИЛИ, первые входы которых через детектор соединены с источником синхроимпульсов, вторые входы подключены перекрестно к выходам формирователей импульсов, а третий вход каждого соединен с выходо.м соответствующего дополнительного логического элемента И, первые входы дополнительных логических элементов И соединены с выходом источника синхроимпульсов, вторые входы подключены к д выходам блоков сравнения кодов, третий вход первого дополнительного логического элемента И соединен с первым входом второго логического элемента И и через инвертор с выходом блока сравнения напряжений, третий вход второго дополнительного логического элемента И соединен с выходом блока сравнения напряжений, причем дополнительный счетчик импульсов включен между выходом второго основного логического элемента И и вторым входом второго блока сравнения кодов, а второй вход каждого счетчика импульсов соединен с выходом соответствующего логического элемента ИЛИ.

Источники информации, принятые во внимание при экспертизе 1. Патент США № 3961271, кл. 328-111, 21.03.74.

2. Авторское свидетельство СССР № 451186, кл. Н 03 К 5/20, 07.12.72.

.- -Tfc

.ч N -. V.-

.-f .. T .

-...

:i

« .733096

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для воспроизведения цифровой информации | 1976 |

|

SU587491A1 |

| Устройство для тестового контроля цифровых узлов | 1980 |

|

SU918949A1 |

| Модуляционный радиометр | 1984 |

|

SU1409953A1 |

| Устройство для измерения группового времени запаздывания в каналах связи | 1984 |

|

SU1197101A2 |

| УСТРОЙСТВО ДЛЯ ВЫЧИТАНИЯ и СЛОЖЕНИЯ ДВУХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ ИМНУЛЬСОВ | 1970 |

|

SU265187A1 |

| Преобразователь последовательности временных интервалов в цифровой код | 1981 |

|

SU1004956A1 |

| Преобразователь интервала времени в цифровой код | 1979 |

|

SU886238A1 |

| Устройство для считывания графической информации | 1986 |

|

SU1354225A1 |

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2012 |

|

RU2496228C1 |

| Устройство для измерения группового времени запаздывания в каналах связи | 1981 |

|

SU1008915A2 |

Авторы

Даты

1980-05-05—Публикация

1977-11-04—Подача