(54) УСТРОЙСТВО для ТЕСТОВОГО КОНТРОЛЯ ЦИФРОВЫХ УЗЛСЖ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля и диагностики логических блоков | 1984 |

|

SU1295401A1 |

| Формирователь тестов | 1985 |

|

SU1260963A1 |

| Многоканальное устройство тестового контроля логических узлов | 1990 |

|

SU1837295A1 |

| Устройство тестового контроля | 1982 |

|

SU1075265A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для диагностики логических блоков | 1988 |

|

SU1672452A1 |

| Устройство для тестового контроля логических узлов | 1991 |

|

SU1837297A1 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

| Устройство для контроля интегральных схем | 1983 |

|

SU1182520A1 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

. . . :

Изобретейие относится к контрюльно измерительной технике и может быть использовано при - работе систем для тестового контроля цифровых узлов электронной аппаратуры.

Известно устройство ддя контроля электрических цепей 1 .

В этом устройстве для выбора нужно- го вывода и подключения его к измерительному устройству из блока ввода и управления в регистр адреса заносится непосредственный адрес вывода, который воздействует на распределитепь и через блок переключений подается сигнал на включение соответствующего реле. В атом случае для хранения каждого из адресов, соотБетствуюишх п выводам устройства контроля, необходимо иметь п ячеек по (PocJ-n ) бит каждая, т.е. общий объем памяти для хранения адресов одного тестового набора составляетСп о яП) бит, что является нерациональным.

Наиболее близким по технической сущности к предлагаемому является устройство для тестового кбнтрюля цифровых узлов цифровой вычислительной машины, содержащее блок памяти, регистр управления, регистр тестов, формирователь, схему сравнения, дешифратор, индикатор и блок опорных напряжений 22.

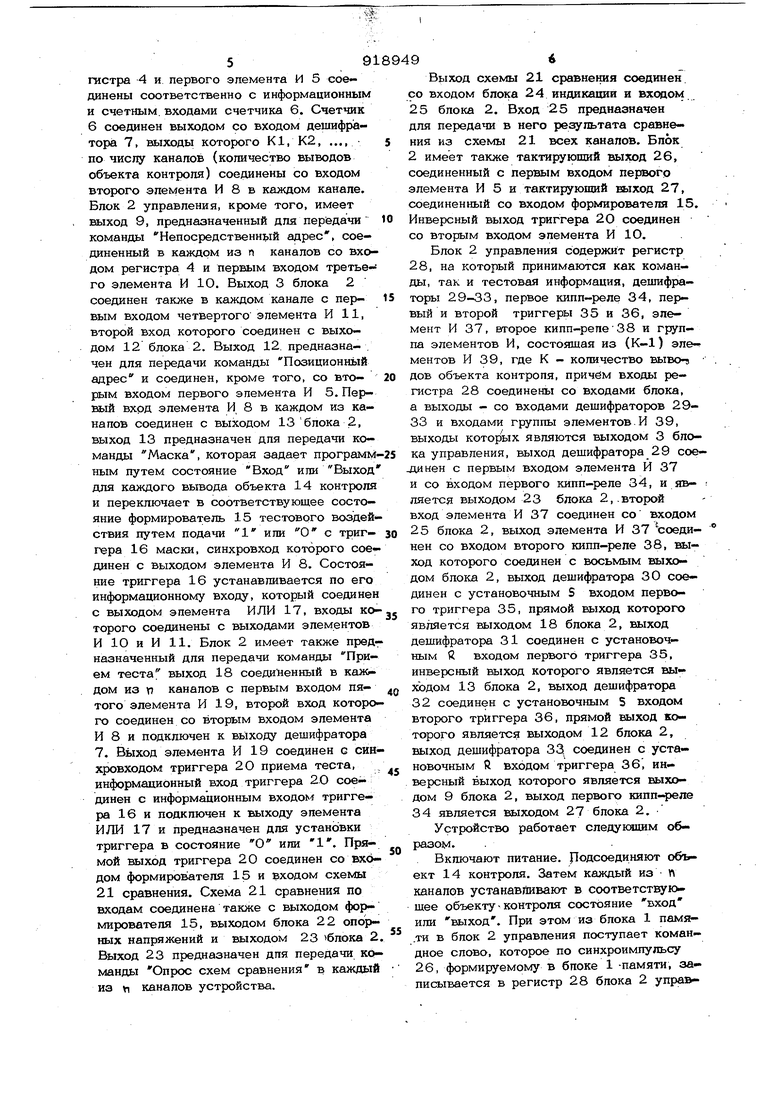

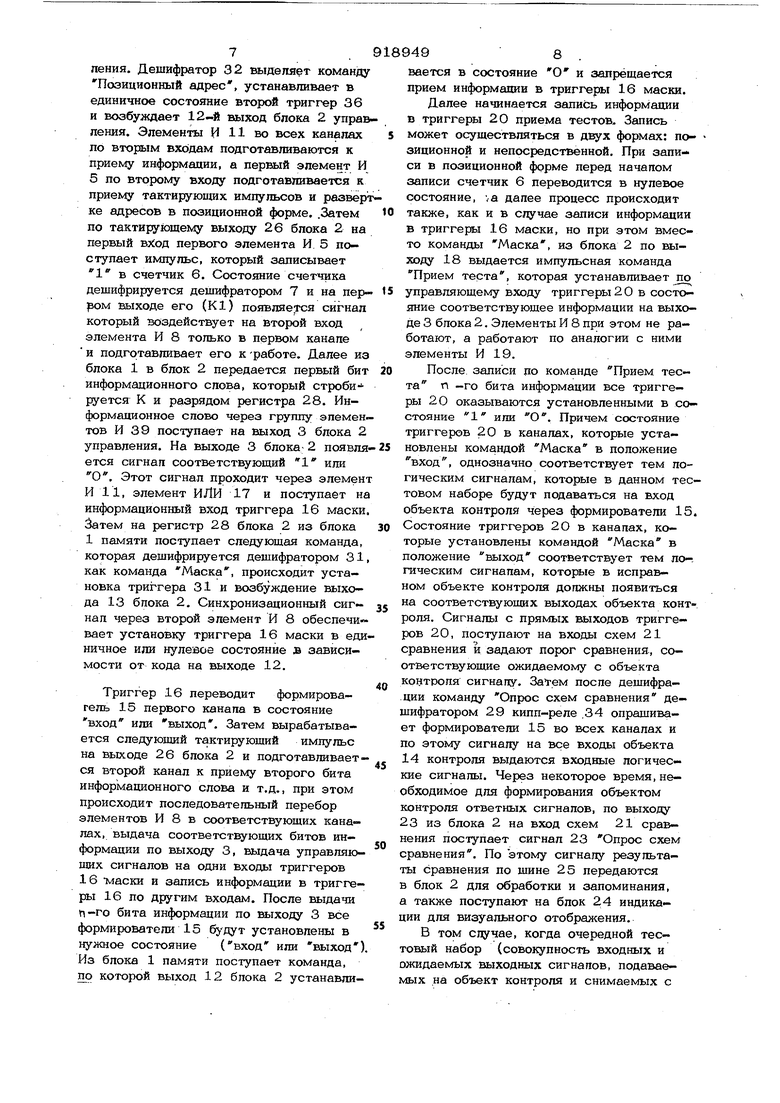

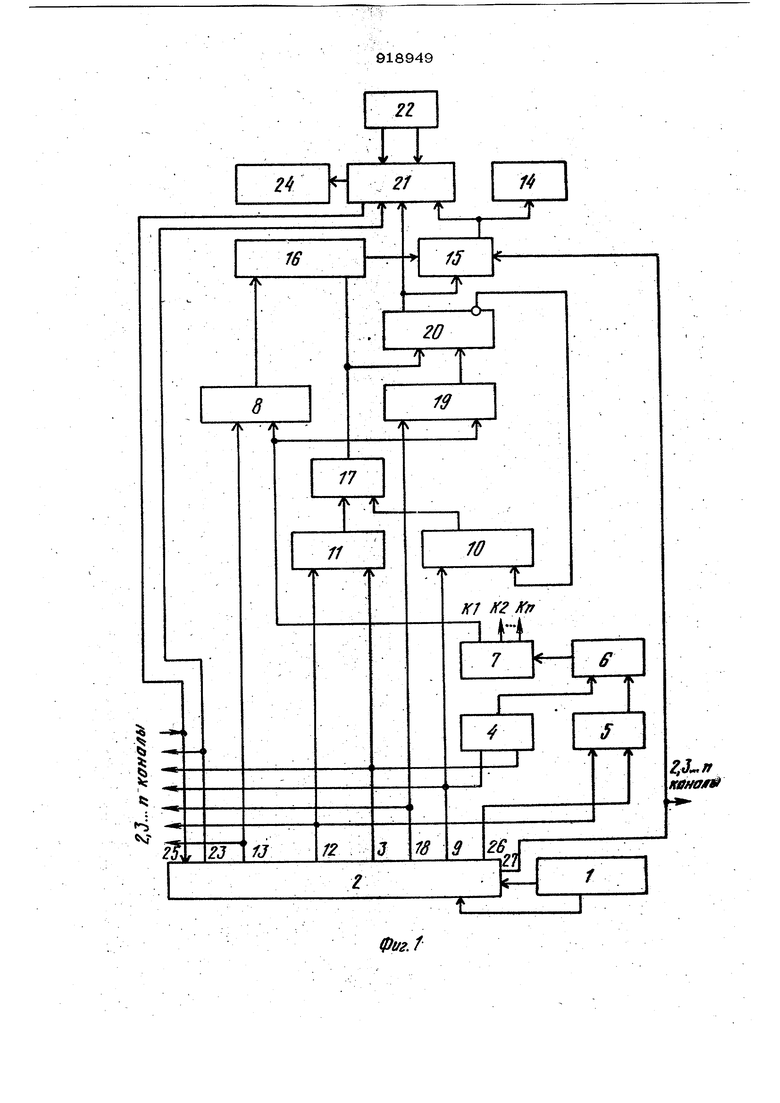

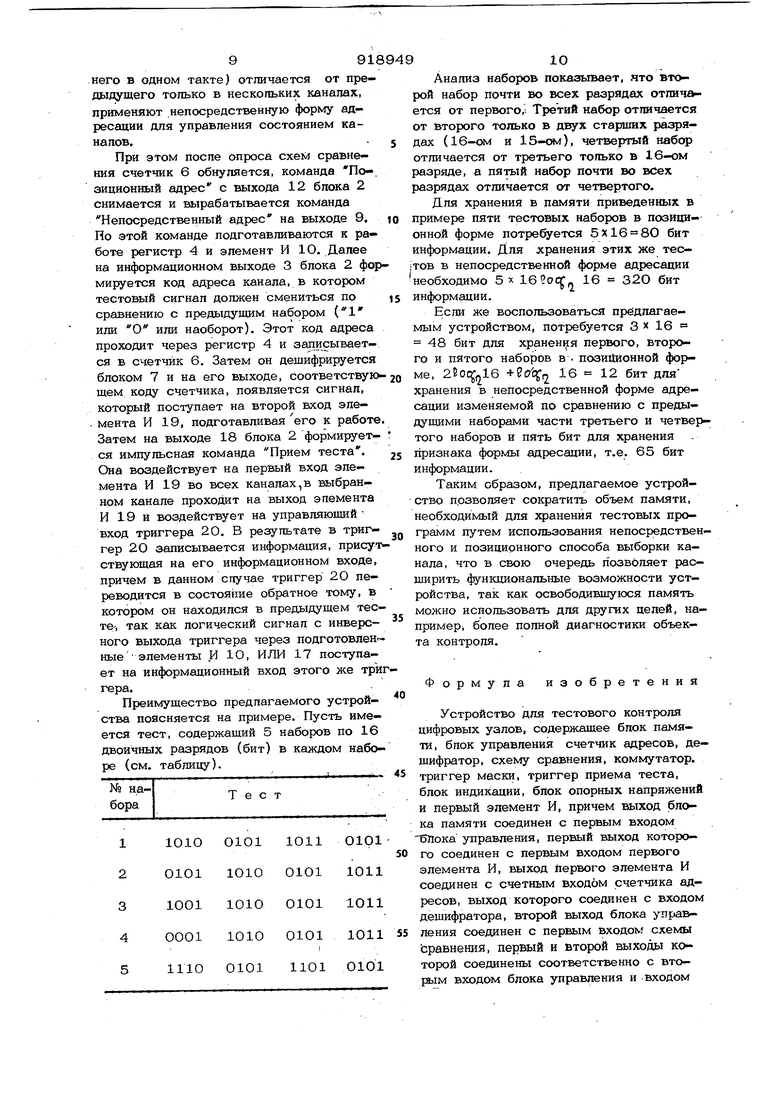

В этом устройстве изменена позиционная формула управления состоянием каналов, при которой в каждый из п к налов, соответствующих п выводам устройства для подключения объекта ковт роля, для каждого тестового набора подается по одному биту информации о состоянии канала ( или О), таким образом, для хранения одного тестового набора необходимо иметь ri бит памяти. Такая форма управления состоянием ка.налов нерациональна в тех случаях, ког.да один тестовый набор отличается от другого лишь в одном или нескольких разрядах, а большинство разрядов не Изменяют своего состояния. 39 Цепь изобретения - уменьшение объема оборудования, необходимого для хранения тестовых программ. Поставленная цепь достигается тем, что в устройство для тестового контроля цифровых узлов, содержащее блок памя- ти. блок управления, счетчик адресов, дешифратор, схему сравнения, формирователь тестового воздействия, триггер маеки, триггер приема теста, блок индикаНИИ, блок опорных напряжений и первый элемент И, причем выход блока памяти соединен с первым входом блока управления, первый выход которого соединен с первым входом первого элемента И, выход первого элемента И соединен со счетным входом счетчика, выход которого соединен со входом дешифратора, втброй выход блока управпения соединен с первым входом схемы сравнения, первый и второй выходы которой соединены соответственно со вторым входом блока управления и входом блока индикации, вы- ход блока опорных напряжений соединен со вторым входом схемы сравнения, еди- ничные выходы триггера маски и триггера приема теста соединены соответственно с первым и вторым входом форми- рователя тестового воздействия, выход которого соединен с третьим входом схемы сравнения и является выходом уст- ройства, третий выход блока управления соединен с третьим входом формирователя тестового воздействия, единичный выход триггера приема теста соединен с четвертым входом схемы сравнения, введены второй, третий, четвертый и пятый элементы И, элементы ИЛИ, регистр непосредственного адреса, причем четвертый выход блока управления соединен с первым входом второго элемента И, выход которого соединен с синхронизационным входом триггера маски, пятый выход блока управления соединен с первым входом третьего элемента И и управляющим входом регистра непосредственного адреса, выход которого соединен с информационным входом счетчика адресов, шестой выход блока управления соединен с информационным входом регистра непр- , средственного адреса и первым входом чвт вертого элемента И, выход которого сое- Ш1иен с первым входом элемента ИЛИ, выход элемента ИЛИ соединен с информа сионным входом триггера маски и триггера приема теста, седьмой выход блока ynjpas пенвя соединен со вторыми входами первого и четвертого элементов И, восьмой и девятый выходы блока управления сое49диневы соответственно со входом 5лока памята, с первым входом пятого элемента И, выход которого соединен с синхронизационным входом триггера приема теста, первый выход дешифратора соединен со вторыми входами вторюго и пятого элементов И, нулевой выход триггера приема теста соединен со вторым входом третьего элемента И, выход которого соеданен со вторым входом элемента ИЛИ, оставшиеся выходы дешифратора образуют первую группу выходов устройства, второй, четвертый, пятый, шестой, седьмой и девятый выходы блока управпения образуют вторую группу выходов устройства. Кроме того, блок управпения содержит регистр, пять дешифраторов, первый и Второй триггеры, эпемент И, первое и второе кйпп-р пе и группу элементов И причем первый вход блока соединен с информадионным входом регистра, выходы которого соединены со входами р етиифра- торов, выход первого дешифратора соеди- нен со входом первого кипп-реле, с nepvвым входом элемента И и является вторым выходом блока, выходы второго и третьего дешифраторов соединены соот- ветственно с S и R входами первого триггера, единичный и нулевой выходы которого явл5потся соответственно девя- тым и четвертым выходами блока управления, выходы четвертого и пятого дешифраторов соединены соответственно с 5 и и. входами второго триггера, единичный и нулевой выходы которого являются соответственно седьмым и пятым выходами блока, второй вход блока сое- со вторым входом -элемента И, выход которого соединен со входом второго кипп-реле, выход второго кипп-репе соединен с восьмым выходом блока, нулевой выход К-го разряда регистра соединен с первыми входами всех элементов И, единичные выходы всех остальных разрядов регистра соединены со вторыми входами соответствукнцих элементов И группы, выходы которых являются шестым выходом блока, ЕЫХОД первого киппреле является третьим выходом блока. На фиг. 1 изображено устройство для тестового контроля цифровых узлов; на фиг. 2 - блок управления. Устрсйство содержит блок 1 памяти, предназначенный для хранения тестовой программы, блок 2 управления через информацйонный выход 3 которого инфор мадия из блока 1 передается в регистр 4 непосредственного адреса. Выходы гистра 4 и первого элемента И 5 соединены соответственно с информационным и счетным, входами счетчика 6. Счетчик 6 соединен выходом со входом дешифратора 7, выходы которого К1, К2 по числу каналов (количество выводов объекта контроля) соединены со входом второго элемента И 8 в каждом канале. Блок 2 управления, кроме того, имеет выход 9, предназначенный для передачи команды Непосредственный адрес , соединенный в каждом из п каналов со вхо дом регистра 4 и первым входом третьего элемента И 10. Выход 3 блока 2 соединен также в каждом канапе с пер- вым входом четвертого элемента И 11, второй вход которого соединен с выходом 12 блока 2. Выход 12. предназна- . чен для передачи команды Позиционнь1й адрес и соединен, кроме того, со вторым входом первого элемента И 5. Первый вход элемента И 8 в каждом из каналов соединен с выходом 13 блока 2, выход 13 предназначен для передачи команды Маска, которая задает программ ным путем состояние Вход или Выход для каждого вывода объекта 14 контроля и переключает в соответствующее состояние формирователь 15 тестового воздей ствия путем подачи 1 или О с триггера 16 маски, синхровход которого соединен с выходом элемента И 8. Состояние триггера 16 устанавливается по его информационному входу, который соединен с выходом элемента ИЛИ 17, входы ко торого соединены с выходами элементов И 10 и И 11. Блок 2 имеет также предг назначенный для передачи команды Прием теста выход 18 соединенный в из V7 каналов с первым входом пятого элемента И 19, второй вход которо го соединен со вторым входом элемента И 8 и подключен к выходу дешифратора 7. Выход элемента И 19 соединен с син хровходом триггера 2 О приема теста, информационный вход триггера 2.0 соединен с информационным вxoдo f триггера 16 и подключен к выходу элемента ИЛИ 17 и предназначен для установки триггера в состояние О или . Прямой триггера 20 соединен со входом формирователя 15 и еходом схемы 21 сравнения. Схема 21 сравнения по входам соединена также с выходом формирователя 15, выходом блока 22 опорных напряжений и выходом 23 блока 2 Выход 23 предназначен для передачи команды Опрос схем сравнения в каждый из VI каналов устройства. Выход схемы 21 сравнения соединен со входом блока 24 индикации и входом. 25 блока 2. Вход 25 предназначен для передачи в него результата сравнения из схемы 21 всех каналов. Блок 2 имеет также тактирующий вызюд 26, соединенный с первым входом первого элемента И 5 и тактирующий выход 27, соединенный со входом формирователя 15. Инверсный выход триггера 20 соединен со вторым входом элемента И 1О. Блок 2 управления содержит регистр 28, на который принимаются как команды, так и тестовая информация, дешифраторы 29-33, первое кипп-реле 34, первый и второй триггеры 35 и 36, элемент И 37, второе кипп-реле38 и группа элементов И, состоящая из (К-1) элементов И 39, где К - количество выво-i . дов объекта контроля, причём входы регистра 28 соединены со входами блока, а выходы - со входами дешифраторов 2933и входами группы элементов.И 39, выходы которых являются выходом 3 блока управления, выход дешифратора 29 соеР нен с первым входом элемента И 37 и со входом первого кипп-реле 34, и яв- пяется выходом 23 блока 2,.второй вход элемента И 37 соединен со входом 25 блока 2, выход элемента И 37 соеди- нен со входом второго кипп-реле 38, выход которого соединен с восьмым выходом блока 2, выход дешифратора 30 соединен с установочным S входом первого триггера 35, прямой выход которого является выходом 18 блока 2, выход дешифратора 31 соединен с установочным и входом первого триггера 35, инверсный выход которого является выходом 13 блока 2, выход дешифратора 32 соединен с установочным 5 входом второго триггера 36, прямой выход которого являете выходом 12 блока 2, выход дешифратора 33. соединен с установочным R входом триггера 36, инверсный выход которого является выходом 9 блока 2, выход первого кипп-реле 34является выходом 27 блока 2. . Устройство работает следующим образом. Включают питание, родсоединяют 14 контроля. Затем каждый из П каналов устанавйивают в соответстнуюшее объекту - контроля состояние вход или выход. При этом из блока 1 памя.ти в блок 2 управления поступает командное слово, которое по синхроимпульсу 26, формируемому в блоке 1 -памяти, записывается в регистр 28 блока 2 управпения. Дешифратор 32 выделяет команду Позиционный адрес , устанавливает в единичное состояние второй триггер 36 и возбуждает 12-й выход блока 2 управ ления. Элементы И 11 во всех каналах по вторым входам подготавливаются к приему информации, а первый элемент И 5 по второму входу подготавливается к приему тактирующих импульсов и разверт ке адресов в позиционной форме. .Затем по тактирующему выходу 26 блока 2 на первый вХод первого элемента И 5 поступает импульс, который записывает I в счетчик 6. Состояние счетчика дешифрируется дешифратором 7 и на перром выходе его (К1) появляется сигнал который воздействует на второй вход элемента И 8 только в первом канале и подготавливает его к -работе. Далее из блока 1 в блок 2 передается первый бит информационного слова, который cтpoби руется К и разрядом регистра 28. Информационное слово через группу эпемен тов И 39 поступает на выход 3 блока 2 управления. На выходе 3 блока- 2 появля ется сигнал соответствующий I или О. Этот сигнал проходит через элемен И 11, элемент ИЛИ 17 и поступает на информационный вход триггера 16 маски Затем на регистр 28 блока 2 из блока 1 памяти поступает следующая команда, которая дешифрируется дешифратором 31 как команда Маска, происходит установка триггера 31 и возбуждение выхода 13 блока 2, Синхронизационный сигнал через второй элемент И 8 обеспечивает установку триггера 16 маски в еди ничное или нулевое состояние s зависимости от кода на выходе 12. Триггер 16 переводит формирователь 15 первого канала в состояние вход или выход. Затем вырабатывается следующий тактирующий импульс на выходе 26 блока 2 и подготавливается второй канал к приему второго бита информационного слова и т.д., при этом происходит последовательный перебор элементов И 8 в соответствующих каналах, выдача соответствующих битов информации по выходу 3, выдача управляющих сигналов на одни входы триггеров 16 тласки и запись информации в триггеры 16 по другим входам. После выдачи П-го бита информации по выходу 3 все формирователи 15 установлены в нужное состояние (вход или выход) Из блока 1 памяти поступает команда, по которой выход 12 блока 2 устанавливается в состояние О и запрещается прием информации в триггеры 16 маски. Далее начинается запись информации в триггеры 20 приема тестов. Запись может осуществляться в двух формах: по- зиционной и непосредственной. При записи в позиционной форме перед началом записи счетчик 6 переводится в нулевое состояние, va далее процесс происходит также, как и в случае записи информации в триггеры 16 маски, но при этом вместо команды Маска, из блока 2 по выходу 18 выдается импульсная команда Прием теста, которая устанавливает jio управляющему входу триггеры 2 О в состояние соответствующее информации на выходе 3 блока 2. Элементы И 8 при этом не работают, а работают по аналогии с ними элементы И 19. После записи по команде Прием теста п -го бита информации все триггеры 20 оказываются установленными в состояние 1 или О. Причем состояние триггеров 20 в каналах, которые установлены командой Маска в положение вход, однозначно соответствует тем логическим сигналам, которые в данном тестовом наборе будут подаваться на вход объекта контроля через формирователи 15. Состояние триггеров 2О в каналах, которые установлены командой Маска в положение выход соответствует тем ло-. гическим сигналам, которые в исправном объекте контроля должны появиться на соответствующих выходах объекта контроля. Сигналы с прямых выходов триггеров 20, поступают на входы схем 21 сравнения и задают порог сравнения, соответствующие ожидаемому с объекта КОНТРОЛЯ сигналу. Затем после дешифра- -ции команду Опрос схем сравнения дешифратором 29 кипп-реле .34 опрашивает формирователи 15 во всех каналах и по этому сигналу на все входы объекта 14 контроля выдаются входные логические сигналы. Через некоторое время, необходимое для формирования объектом контроля ответных сигналов, по выходу 23 из блока 2 на вход схем 21 сравнения поступает сигнал 23 Опрос схем сравнения. По этому сигналу результаты сравнения по шине 25 передаются в блок 2 для обработки и запоминания, а также поступают на блок 24 индикации для визуального отображения. В том случае, когда очередной тестовый набор (совокупность входных и ожидаемъ1х выходных сигналов, подаваемых на объект контроля и снимаемых с 991 него в одном такте) отличается от предыдущего только в нескольких каналах, применяют .непосредственную форму адресации для управления состоянием каналов. При этом после опроса схем сравнения счетчик 6 обнуляется, команда По- зиционный адрес с выхода 12 блока 2 снимается и вырабатывается команда Непосредственный адрес на выходе 9. По этой команде подготавливаются к работе регистр 4 и элемент И 10. Далее на информационном выходе 3 блока 2 фо мируется код адреса канала, в котором тестовый сигнал должен смениться по сравнению с предыдущим набором (1 или О или наоборот). Этот код адреса проходит через регистр 4 и записывается в счетчик 6, Затем он дешифрируется блоком 7 и на его выходе, соответствую щем коду счетчика, появляется сигнал, который поступает на второй вход элемента И 19, подготавливая его к работе Затем на выходе 18 блока 2 формируется импульсная команда Прием теста. Она воздействует на первый вход элемента И 19 во всех каналах,в выбранном канале проходит на выход элемента И 19 и воздействует на управляющий вход триггера 20. В результате в триггер 2О записывается информация, присут ствующая на его информационном входе, причем в данном случае триггер 2О переводится в состоя1ше обратное тому, в котором он находился в предыдущем тесте-, так как логический сигнал с инверсного выхода триггера через подготовлен™ ныеэлементы И 1О, ИЛИ 17 поступает на информационный вход этого же три гера. Преимущество предлагаемого устройства поясняется на примере. Пусть имеется тест, содержащий 5 наборов по 16 двоичных разрядов (бит) в каждом наборе (см. таблицу). Анализ наборов показывает, .что второй набор почти во всех разрядах отличается от первого, Третий набор отличается от второго только в двух старших разрядах (16-c8vr и 15-ом), четвертый набор отличается от третьего только в 16-ом разряде, а пятый набор почти во всех разрядах отличается от четвертого. Для хранения в памяти приведенных в примере пяти тестовых наборов в позиционной форме потребуется 5x16 80 бит информации. Для хранения этих же тесJTOB в непосредственной форме адресации необходимо 5 х 16 32О бит информации. Если же воспользоваться предлагаемым устройством, потребуется 3 х 16 48 бит для хранени я первого, второго и пятого наборов в . позиционной форнме, .iQ 16 12 бит для хранения в непосредственной форме адресации изменяемой по сравнению с предыдущими наборами части третьего и четвер)- того наборов и пять бит для хранения признака формы адресации, т.е. 65 бит информации. Таким образом, предлагаемое устройство позволяет сократить объем памяти, необходимый для зфанения тестовых программ путем использования непосредственного и позиционного способа выборки канала, что в свою очередь позволяет рас- щирить функциональные возможности устройства, так как освободивщуюся память можно использовать для других целей, например, более полной диагностики объекта контроля. Формула изобретения Устройство для тестового контроля цифровых узлов, содержащее блок памяти, блок управления счетчик адресов, де- щифратор, схему сравнения, коммутатор, триггер маски, триггер приема теста, блок индикации, блок опорных напряжений и первый элемент И, причем выход блока памяти соединен с первым входом блока управления, первый выход которо- го соединен с первым входом первого элемента И, выход первого элемента И соединен с счетным входом счетчика адресов, выход которого соединен с входом дешифратора, второй выход блока упра&ления соединен с первым входом схемы Ьравнения, первый и второй выходы которой соединены соответственно с вторым входом блока управления и входом

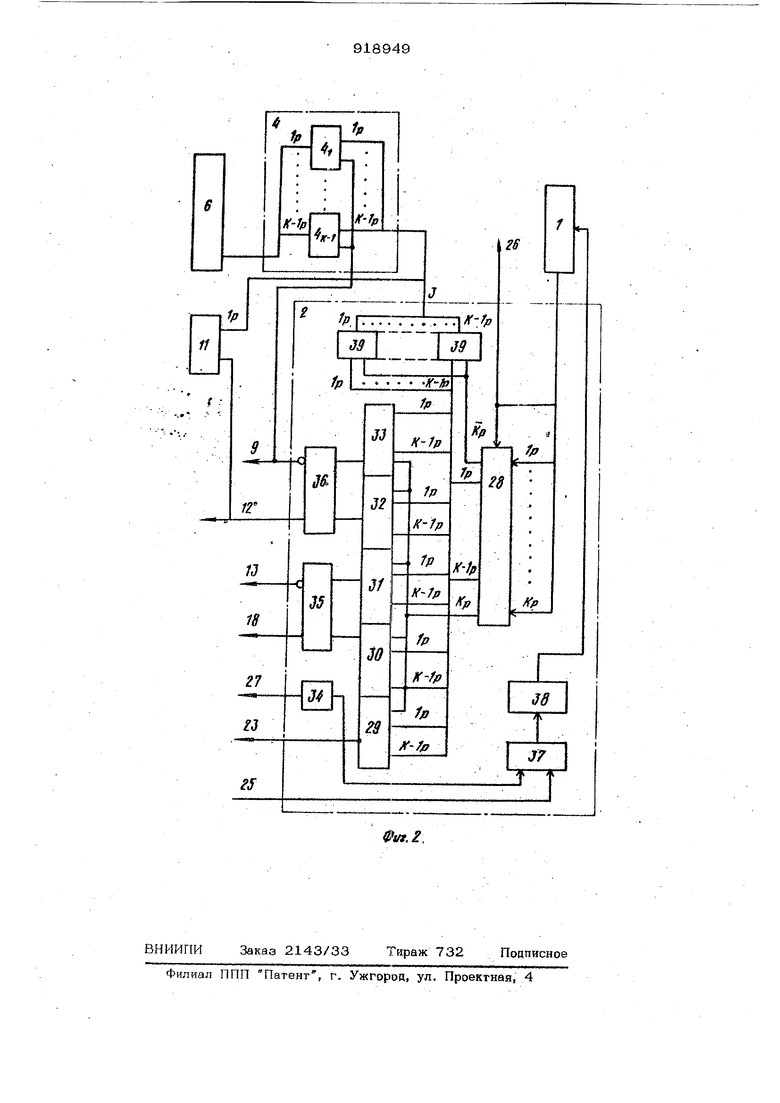

блока индикации, выход блока; опорных напряжений соединен с вторым входом схемы сравнения, единичные выходы триггера маски и триггера приема теста соединены соответственно с первым и вторым входом коммутатора, выход которого соединен с третьим входом схемы сравнения и является выходом устройст ва, третий выход блока управления соединен с третьим входом коммутатора действия, единичный выход триггера приема теста соединен с четвертым входом схемы сравнения, отличающееся тем, что, с цепью уменьшения объема оборуцотвапия в него введены второй, третий, четверть1й и пятый элементы И, элемент ИЛИ, регистр непосредственного адреса, причем четвертый выход блока управления соединен с первым входом второго элемента И, выход котог рого соединен с синхронизационным входом триггера маски, пятый выход блока управления соединен с первым входом третьего элемента И и управляющим входом регистра непосредственного адреса, выход которого соединен с информационным входом счетчика адресов, шестой выход блока управления соединен с мационным входом регистра н посредственного адреса и первым входом четвертого элемента И, выход которого соединен с первым входом элемента И/1И, выход элемента ИЛИ соединен с информаЩ1онным входом триггера маски и триг- гера приема теста, седьмой выход бпо ка управления соединен с вторыми входами первого и четвертого элементов И, восьмой и девятьй выходы блока управления соединены соответственно с вхо дом блока памяти, f первым входом пя того элемента И, выход которого соединен с синхронизационным входом триггера приема теста, первый выход дешифратора соединен с вторыми входами второго и пятого элементов И, нулевой выход триггера приема теста соединен с вторым входом третьего элемента И, выход Которого соединен с вторым входом элемента ИЛИ, остальные выходы дешифратора образуют первую группу выходов устройНтва, второй, четвертый, пятый, шестой, седьмой и девятый выходы блока управления образуют вторую группу выходов устройства.

2, Устройство поп. 1, отличающее с я тем, что .блок управления содержит регистр, пять дешифраторов, первый и второй триггеры, элементы И, первое и второе кипп-реле и группу элементов И,- причем первый вход бпока соединен с информационным входом регистра, единичные выходы К- -f разрядов которого соединены с соответствующими входами каждого из дешифраторов, выход первого дешифратора соединен с входом первого кипп-реле, с первым входом элемента И и является вторым выходом блока, выходы второго и третьего дешифраторов соединены соответственно с 5 и R входами первого триггера, единичный и нулевой выходы которого являются соответственно девятым и четвертым выходами блока управления, выходы четвертого и пятого дешифраторов соединены соответственно с S и ft входами второго триггера, единичный и нулевой выходы которого являютс.я соответственно седьмым и пятым выходами блока, второй вход блока соединен с вторым входом элемента И, выход которого соединен с входом второго кипп-репе, выход второго кипп-реле соединен с восьмым выходом блока, нулевой выход К-го разряда регистра соединен с первыми входами всех элементов И группы, единичные выходы 1-(1-К) разрядов регистра соединены с вторыми входами соответствуюишх элементов И группы, выходы которых являются шестым выходом блока, выход первого кипп-реле является третьим выходом блока.

Источники информации, принятые во внимание при экспертизе

фиг. f

%г-,.

1

K-lp

S

IP

1P.

11

IP

f

3&

rr

/J

ne-

35

f8

К-Гр

J9

K-ta

ffl

Kp

K-lp

ffl

IP

2d

IP

K-lp

ff-ffl

ffp

ffp

27

IJ

IS

fp

K-fp

Iff

ff-fff

Фаг. г

Авторы

Даты

1982-04-07—Публикация

1980-06-30—Подача