Блок анализа сообщений содержит узел дифференцирования входного сигнала, вход которого является входом блока, а выход подключен ко входу элемента задержки первого сообщения, соединенного выходом через первый элемент И и формирователь первого сообщения с первым выходом блока, ко входу элемента задержки второго сообщения, соединенного выходом через второй элемент И и формирователь второго сообщения со вторым выходом блока, и через элемент ИЛИ ко входу счетчика, соединенного выходом со входом дешифратора, выходы которого подключены соответственно ко входам трех реле времени, первые выходы которых подключены к соответствующим выходам сброса счетчика, а вторые выходы - соответственно к управляющим входам первого и второго элементов И и входу формирователя сигнала недостоверности, соединенного выходом со вторым выходом блока.

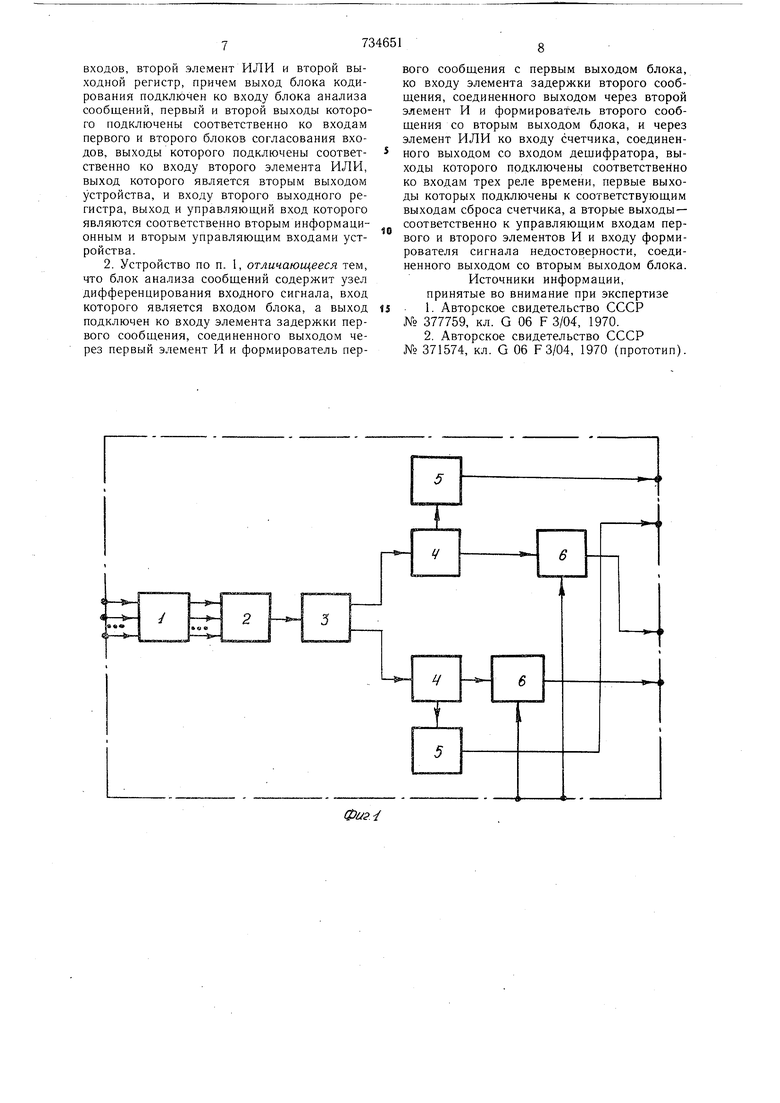

На фиг. 1 представлена блок-схема устройства; на фиг. 2 - блок-схема блока анализа сообщений.

Устройство содержит блок 1 формирования сигналов датчиков, блок 2 кодирования, блок 3 анализа сообщений, блоки 4 согласования входов, элементы 5 ИЛИ и выходные регистры 6.

Блок 3 анализа сообщений состоит из узла 7 дифференциирования входного сигнала, элемента 8 задержки первого сообщения, первого элемента 9 И, формирователя 10 первого сообщения, элемента 11 задержки второго сообщения, второго элемента 12И, формирователя 13 второго сообщения, элемента 14 ИЛИ, счетчика 15, дешифратора 16, первого, второго и третьего реле 17- 19 времени и формирователя 20 сигнала недостоверности.

Блок 1 предназначен для формирования стандартных длительностей выходных сигналов по сигналам на входах, поступающим от датчиков. Блок 2 служит для преобразования выходного сигнала блока 1 в параллельный код адреса датчика; блок 4 служит для согласования выходов блока 3 со входами элемента ИЛИ 5 и выходных регистров 6.

Узел 3 формирует положительные и отрицательные импульсы в моменты прохождения через него соответственно передних и задних фронтов входных сигналов.

Устройство работает следующим образом.

В момент свершения контролируемого события срабатывает соответствующий датчик и на один из входов блока 1 подается импульс произвольной амплитуды и длительности. На его основе блок 1 формирует импульс строго заданной амплитуды и длительности, после чего выдает его на соответствующий вход блока 2. Здесь этот импульс преобразуется в параллельный код сигнала (сообщения), представляющий собой адрес сработавщего датчика. С выхода блока 2 код сообщения по общему для всех датчиков каналу связи поступает на вход блока 3. Поскольку каждый из датчиков срабатывает в произвольные моменты времени,

за промежуток времени передачи отдельного сообщения возможно срабатывание нескольких датчиков. Импульсы с их выходов передаются на соответствующие входы блока 2, который в этом случае формирует паралл ельный код, в общем случае не совпадающий ни с одним из требуемых. Блок 3 позволяет выявить эти ситуации и может работать в трех режимах.

Первый режим работы блока 3 имеет место, когда через блок передается код сообщения, сформированный на основе импульса одного сработавщего датчика. В этом случае передние и задние фронты импульсов параллельного кода совпадают во времени. Оценив это, блок 3 выдает сообщение на вход первого блока 4 и через него на входы

0 соответствующих элемента 5 ИЛИ и выходного регистра 6. Элемент 5 ИЛИ на основе поступившего параллельного кода сообщения формирует импульс, который сигнализирует вычислительной машине о записи очередного сообщения в выходной регистр 6. Получив такой сигнал, вычислительная машина осуществляет перезапись содержимого выходного регистра 6 в свою оперативную память и устанавливает в нуль триггеры этого регистра.

0 В правильно рассчитанном устройстве вероятность наложения сообщений нескольких датчиков представляет собой малую величину, а поэтому первый режим является главным режимом работы блока 3.

S Второй режим работы блока 3 возникает тогда, когда через него передается код сообщения, сформированный на основе двух перекрывающихся одиночных импульсов с датчиков. Блок 3 при этом путем дифферен- цирования передних и задних фронтов разрядных импульсов кода формирует параллельные коды первого и второго сообщения И выдает их на первый и второй блоки 4 согласования. С выхода этих блоков каждое сообщение поступает на соответствующие

5 элементы 5 ИЛИ и выходные регистры 6. По командам с выходов элементов 5 ИЛИ вычислительная мащина переписывает в свою очередь память последовательно первое и второе сообщения с каждого из выходных регистров 6.

Очень редко встречается режим работы блока 3, когда через него передается сообщение, сформированное из налагающихся во времени трех и более одиночн л. импульсов, J поступающих с датчиков. В /--JM режиме с помощью блока 3 уже не удается выделить каждое из требуемых сообщений. Упомянутым блоком выдается на свой первый выход параллельный код сообщения, соответствующий адресу первого из сработавших датчиков, а на второй - параллельный код сигнала о наложении нескольких сообщений при их передаче через устройство. Дальнейшее следование сообщений в вычислительную мащину описано при рассмотрении второго режима работы блока 3.

Работа блока 3 заключается в следующем.

В первом режиме, когда через блок передается только одно сообщение, на выходе узла 7 появляются группы -положительных и отрицательных импульсов, соответствующих чпередним и задним фронтам входных сигналов. В элементах 8 и 1 задержки импульсы задерживаются, а элемент 14 ИЛИ на их основе формирует одиночный импульс положительной полярности при прохождении переднего фронта сообщения и отрицательной полярности при передаче заднего фронта сообщения. С выходов элемента ИЛИ 14 эти импульсы поступают на входы счетчика 15, раздельно считающего число продифференцированных передних и задних фронтов проходящих сигналов. В первом режиме передача каждого сигнала связана с появлением на выходе элемента 14 ИЛИ одного положительного и сдвинутого на время, равное длительности сигнала отрицательного импульса. Уже после того, как счетчик 15 зафиксирует появление положительного импульса, дещифратор 16 подаст напряжение на первое реле 17. С первого выхода этого реле будет подан разрещающий потенциал на управляющий вход первого элемента 9 И, через который положительные импульсы пройдут на вход формирователя 10. Здесь на их основе восстанавливается параллельный код передаваемого сообщения с требуемой амплитудой и длительностью, и выдается на первый выход блока. После этого первое реле 17 сбросит счетчик 15. При этом отрицательные импульсы через закрытые первый и второй элементы 9 и 12 И не проходят.

Во втором режиме работы блока 3 элемент 14 ИЛИ формирует два положительных и два отрицательных импульса или один положительный и два отрицательных импульса. В любом случае, после -поступления первого положительного импульса на счетчик 15, дешифратор 16 подает напряжение на первое реле 17, которое обеспечит передачу на первый выход блока первого из передаваемых сообщений. Однако во втором режиме еще до этого момента времени счетчик 15 зафиксирует поступление еще одного положительного или двух отрицательных импульсов. Дешифратор 16 снимет управляющее напряжение с первого реле 17 и подаст его на вход второго реле 18. Это не повлияет на передачу через блок первого из сообщений, но импульс сброса счетчика 15 на втором выходе первого реле 17 не появится.

После включения второго реле 18, которое в требуемый момент времени подаст разрешающий потенциал на второй элемент 12И и обеспечит прохождение отрицательных импульсов на формирователь 13, эти импульсы обеспечивают выдачу на второй выход блока 3 второго из одновременно проходящих через этот блок сообщений.

В третьем режиме, когда через блок одновременно передается более двух -сообщений, элемент 14 ИЛИ формирует более двух положительных или отрицательных импульсов. После поступления первого положительного импульса на вход счетчика 15 дешифратор 16 подает управляющее напряжение на вход первого реле 17, что обеспечивает передачу через блок первого из поступивщих сообщений (аналогично передаче первого сообщения во втором режиме работы блока). До окончания этого процесса на счетчик 15 поступит второй положительный или отрицательный импульсы. Дещифратор 16 включит в работу второе реле 18, которое начнет подготовку блока к выдаче второго из проходящих через блок сообщений. Однако, еще до того, как это произойдет, на счетчик 15 подает третий положительный или отрицательный импульсы. Дешифратор 16, снимая управляющее напряжение, прекращает работу второго реле 18 и подает с третьего выхода напряжение на третье реле 19.

Через требуемое время это реле выдает на свои выходы два одиночных импульса. Сначала импульс с первого выхода подается на формирователь 20, который на его основе формирует параллельный код, извещающий о наложении сообщений и передает его на второй выход блока. Импульс со второго выхода третьего реле 19 устанавливает в нуль счетчик 15.

Таким образом, устройство обеспечивает выявление ситуаций положения входных сигналов датчиков (сообщений) и коррекцию этих сообщений в случаях наложения двух сигналов.

Формула изобретения

1. Устройство для сопряжения вычислительной машины с импульсными датчиками, содержашее блок формирования сигналов датчиков, группа входов которого является группой входов устройства, а группа выходов подключена к соответствующим входам блока кодирования, первый блок согласования входов, выходы которого подключены соответственно ко входу первого элемента ИЛИ, выход которого является первым выходом устройства, и входу первого выходного регистра, выход и управляющий вход которого являются соответственно первым информационным и первым управляющим входами устройства, отличающееся тем, что, с целью повышения достоверности работы устройства, в него введен блок анализа сообшений, второй блок согласования

входов, второй элемент или и второй выходной регистр, причем выход блока кодирования подключен ко входу блока анализа сообщений, первый и второй выходы которого подключены соответственно ко входам первого и второго блоков согласования входов, выходы которого подключены соответственно ко входу второго элемента ИЛИ, выход которого является вторым выходом устройства, и входу второго выходного регистра, выход и управляющий вход которого являются соответственно вторым информационным и вторым управляющим входами устройства.

2. Устройство по п. 1, отличающееся тем, что блок анализа сообщений содержит узел дифференцирования входного сигнала, вход которого является входом блока, а выход подключен ко входу элемента задержки первого сообщения, соединенного выходом через первый элемент И и формирователь первого сообщения с первым выходом блока, ко входу элемента задержки второго сообщения, соединенного выходом через второй элемент И и формирователь второго сообщения со вторым выходом блока, и через элемент ИЛИ ко входу счетчика, соединенного выходом со входом дещифратора, выходы которого подключены соответственно ко входам трех реле времени, первые выходы которых подключены к соответствующим выходам сброса счетчика, а вторые выходы- соответственно к управляющим входам первого и второго элементов И и входу формирователя сигнала недостоверности, соединенного выходом со вторым выходом блока.

Источники информации, принятые во внимание при экспертизе 1 Авторское свидетельство СССР № 377759, кл. G 06 F 3/04, 1970.

2. Авторское свидетельство СССР № 371574, кл. G 06 F3/04, 1970 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения вычислительной машины с аналоговыми датчиками | 1981 |

|

SU972497A1 |

| Устройство для сопряжения вычислительной машины с датчиками | 1981 |

|

SU999036A2 |

| Устройство для сопряжения вычислительной машины с датчиками | 1982 |

|

SU1096634A2 |

| Устройство для сопряжения источников информации с приемниками | 1979 |

|

SU938276A1 |

| Устройство для ввода информации от аналоговых датчиков | 1985 |

|

SU1287141A1 |

| Устройство для сопряжения вычислительной машины с аналоговыми датчиками | 1983 |

|

SU1095166A1 |

| Устройство для сопряжения вычислительной машины с датчиками | 1980 |

|

SU926643A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ | 1991 |

|

RU2037964C1 |

| Устройство для ввода информации от контактных датчиков | 1981 |

|

SU972498A1 |

| Устройство для формирования адресов датчиков | 1977 |

|

SU732873A1 |

Авторы

Даты

1980-05-15—Публикация

1977-11-23—Подача