Изобретение относится к области кодирования импульсных последовательностей, а именно к обнаружению нарушений в закономерностях импульс ных последовательностей (например, нарушения случайности в флуктуациях амплитуд), и может быть использовано для обнаружения сигнала на фоне слу чайных помех при анализе последовательности независимых импульсов oitpe деленного объема. Известно устройство обработки информации, в котором в памяти, вы полненной на ферритовых сердечниках хранятся две анализируемое последовательности общим объемом 2N , расп ложенные с помощью аналого-цифровог преобразователя и схемы сравнения с соответствующим управлением выводом из памяти и перезаписью в таком порядке, что адреса их по одной координате- соответствуют рангу каждото входного импульса в общей последовательности, а ацрес по другой координате соответствует номеру поступления данного импульса. При считывании из памяти вычисляется разность этих координат, возводится в квадрат, суммируется и сравнивается с порогом для выноса решения о случайности флуктуации амплитуды (сигнала нет, у 0) или неслучайности ( 1) Ц , Недостатком устройства является то, что после аналого-цифрового преобразования, определения рангов путем перебора всех элементов в двойной выборке (2N элементов) и сравнения с HOBfciM элементом снижается быстродействие устройства, затрудняя использование обнаружите ля в реальном масштабе времени. Цель изобретения - повышение быстродействия за счет сокращения времени на определение разности между . номером импульса в последовательности и его рангом. Поставленная цель достигается тем, что в устройство для контроля последовательности импульсов, содержащее блок запоминания, блок управления, блок вычитания, квадратор, накопитель, решающий блок и цифроаналоговый преобразователь, причем вход устройства соединен с первыми входами блока запоминания и блока управления, синхронизирующий вход которого соединен с соответствующим

входом блока запоминания, выход квадратора соединен через накопитель с информационным входом решающего блока, управляющий вход которого и управляющие входы накопителя и блока вычитания соединены с соответствующими выходами блока упра.вления, введены амплитудный дискриминатор и счетчик, причем выход блока sanojvMнания соединен с информационными входами амплитудного дискриминатора и счетчика,, управляющие входы которых соединены с cooтвeтcтвyющимli выходами блока управления, а выходы - соответственно с первым и вторым входами блока вычитания, выход которого через цифроаналоговый преобразователь соединен со входом квадратора, и тем, что блок запоминания содержит видикон, соединенный с блоками развертки и гашения, генератором стирания, блоком смещения начала строки и коммутатором, ин11юрмационные вход и выход которого являются входом и выходом блока запоминания, управляющие входы блока смещения начала строки, блока разверки, блока гашения, блока стирания ;И коммутатора соединены с синхронизирующим входом блока запоминания.

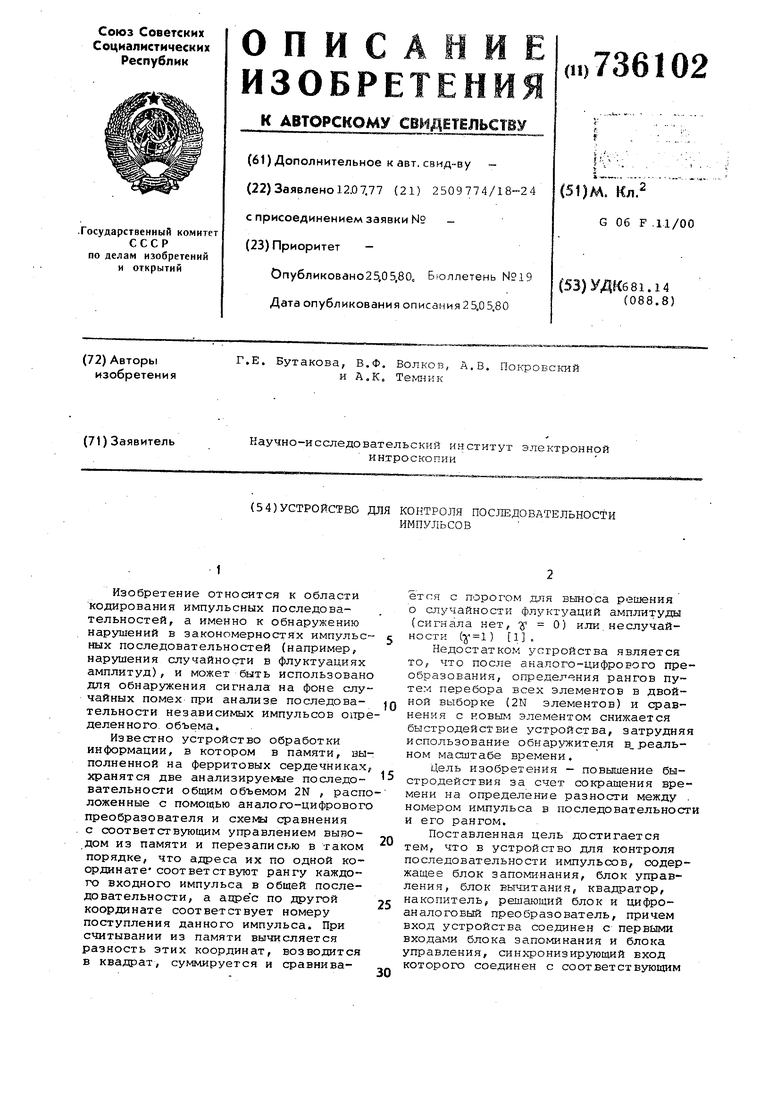

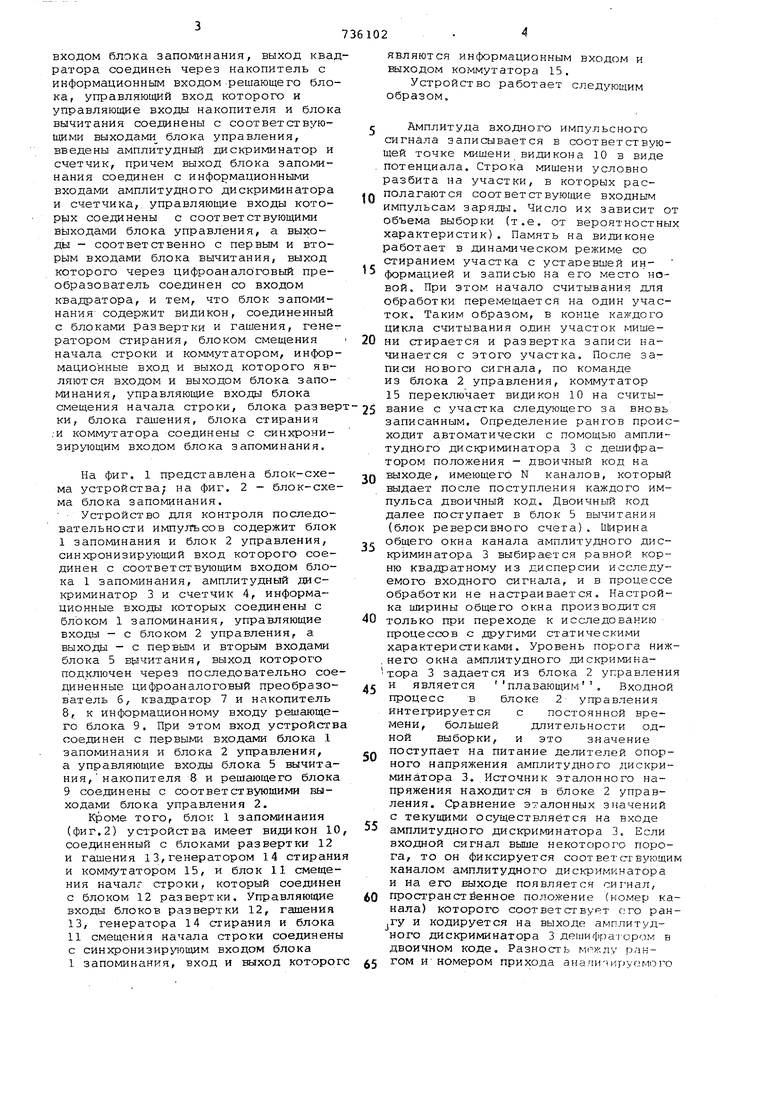

На фиг. 1 представлена блок-схема устройства; на фиг. 2 - блок-схема блока запоминания.

Устройство для контроля последовательности импульсов содержит блок 1 запоминания и блок 2 управления, синхронизирующий вход которого соединен с соответствующим входом блока 1 запоминания, амплитудный дисгфиминатор 3 и счетчик 4, информационные входы которых соединены с блоком 1 запоминания, управляющие входы - с блоком 2 управления, а, выходы - с первым и вторым входами блока 5 вычитания, выход которого подключен через последовательно соединенные цифроаналоговый преобразователь б, квадратор 7 и накопитель 8, к информационному входу решанвдего блока 9. При этом вход устройств соединен с первыми входами блокс1 1 запоминания и блока 2 управления, а управляющие входы блока 5 вычитания, накопителя 8 и решающего блока 9 соединены с соответствующими зьаходами блока управления 2.

Кроме того, блок 1 запоминания (фиг.2) устройства имеет видикон 10 соединенный с блоками развертки 12 и гашения 13,генератором 14 стирани и коммутатором 15, и блок 11 смещения началг строки, который соед1-1нен с блоком 12 развертки. Управляющие входы блоков развертки 12, гашения 13, генератора 14 стирания и блока 11 смещения начала строки соединены с синхронизирующим входом блока 1 запоминания, вход и выход которог

являются информационным входом и выходом коммутатора 15.

Устройство работает следующим образом.

Амплитуда входного игипульсного сигнала записывается в соответствующей точке мишени видикона 10 в виде потенциала. Строка мишени условно разбита на участки, в которых располагаются соответствующие входным импульсам заряды. Число их зависит о объема выборки (т.е. от вероятностны характеристик). Память на видиконе работает в динамическом режиме со стиранием участка с устаревшей информацией и записью на его место новой. При этом начало считывания для обработки перемещается на один участок. Таким образом, в конце каждого цикла считывания один участок мишени стирается и развертка записи начинается с этого участка. После записи нового сигнала, по команде из блока 2 управления, коммутатор 15 переключает видикон 10 на считывание с участка следующего за вновь записанным. Определение рангов происходит автоматически с помощью амплитудного дискриминатора 3 с дешифратором положения - двоичный код на выходе, имеющего N каналов, который выдает после поступления каждого импульса двоичный код. Двоичный код далее поступает в блок 5 вычитания (блок реверсивного счета) . Шрина общего окна канала амплитудного дискриминатора 3 выбирается равной корню квадратному из дисперсии исследуемого входного сигнала, и в процессе обработки не настраивается. Настройка ширины общего окна производится только при переходе к исследованию процессов с другими статическими характеристиками. Уровень порога ниж.него окна амплитудного дискриминатора 3 задается из блока 2 управлени и является плавающим. Входной процесс в блоке 2 управления интегрируется с постоянной времени, большейдлительности одной выборки, и это значение поступает на питание делителей опорного напряжения амплитудного дискриминатора 3..Источник эталонного напряжения находится в блоке 2 управления. Сравнение эталонных значений с текущими осуществляется на входе амплитудного дискриминатора 3. Если входной сигнал выше некоторого порога, то он фиксируется соответсгвующи каналом амплитудного дискриминатора и на его выходе появляется си г-н ал, пространстйенное положение (номер канала) которого соответствует его и кодируется на выходе амплитудного дискриминатора 3 де1иифра1 ором в двоичном коде. Разность мяжлу рангом и- номером прихода анализируемого импульса на выходе блока 5 вычитани преобразуется в блоке 6 в аналоговую величину (напряжение), которая возво дится в квадрат в блоке 7 и накапли вается в течение строки считывания в блоке 8. Подачей сигнала из блока 2 управления 2 в накопитель 8 происходит выдача результата на решающее устройство 9, которое выдает результат 2 -If если сумма больше порога К,.и у 0, если сумма меньше порога К. Затем происходит сброс накопителя 8 в нуль. Одновременно с этим генератор 14 стирания и блок 13 гашения стирают первый из исследуемой выборки элемент. Блок 11 смещения начала строки с помощью блока 12 развертки устанавливает начало строки записи в положение стертого элемента После записи по команде из блока 2 управления 2 коммутатор 15 переключает видикон 10 на считывание с учас ка следующего за вновь записанным, процесс считывания повторяется в описанном порядке. Определение рангов элементов выборки происходит за одно считывание элемента, без перебора всех элементо Анализ в устройстве производится непрерывно после прихода каждого импульса на его вход. Продолжительность обработки информации в выборке определяют частоту следования входных импульсов. Организация динамического режима запоминающего устройства и сокращение времени на вычисле ние статистики устройства с. дешифратором положения - двоичный код на выходе и счетчика позволяет обеспечить большее быстродействие, чем устройство с определением рангов путем последовательного перебора всех элементов двух выборок. Кроме того, в устройстве величина порога зависит только от двух параметров : сА - заданной вероятности ложных тревог и N. в случае расширения диапазона использования устройства при различных сЛ и N в блоке управления можно предусмотреть клавишную матрицу, столбцы которой соответствуют значениям о., строки-N. При нажатии любой клавиши меняется порог К. Формула .изобретения 1, Устройство для контроля последовательности и myльcoв, содержащее блок запоминания, блок управления, блок вычитания, квадратор, накопитель, решающий блок и цифроаналоговый преобразователь, причем вход устройства соединен с первЕлми входами блока запоминания и блока управления, синхронизирующий вход которого соединен с соответствующим входом блока запоминания, выход квадратора соединен чер.ез накопитель с информационным входом решающего блока, . управляющий вход которого и управляющие входы накопителя и блока вычитания соединены с соответствующими выходами блока управления, отличающее ся тем,что, с целью повышения быстродействия, в него введены амплитудный дискриминатор и счетчик, причем выход блока запоминания соединен с информационными входами амплитудно.го дискриминатора и счетчика, управляющие входы которых соединены с соответствующими выходами блока управления, а выходы - соответственно с первым и вторым входами блока вычитани-я, вьдход которого через цифроаналоговый преобразователь соединен со входом квадратора., . 2. Устройство по П.1, о т л и- . чающееся тем, что блок запоминания содержит видикон, соединенный с блоками развертки и гашег . ния, генератором стирания, блоком смещения начала строки и коммутатором, информационные вход и выход которого являются входом и выходом блока запоминания, управляющие входы блока смещения начала строки, блока развертки, блока гашения, блока стирания и коммутатора соединены с синхронизируюищм входом блока запоминания. Источники информации, принятые во внимание при экспертизе 1. .Неразрушающие методы и средства контроля и их применение в промышленности . Минск, 1973, с 362 . (прототип).

L - - - -

Фш. i

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЯ | 1992 |

|

RU2045781C1 |

| Устройство для считывания изображений | 1987 |

|

SU1481816A2 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЙ ПО БАЗОВОМУ ИНТЕГРАЛЬНОМУ МЕТОДУ (БИМ) | 1996 |

|

RU2162247C2 |

| Телевизионная камера | 1977 |

|

SU660299A1 |

| Устройство для распознавания геометрических фигур | 1977 |

|

SU652580A1 |

| Адаптивный статистический анализатор | 1987 |

|

SU1434453A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЙ ПО БАЗОВОМУ ИНТЕГРАЛЬНОМУ МЕТОДУ (БИМ) | 1996 |

|

RU2162248C2 |

| Анализатор амплитудно-временных параметров случайных сигналов | 1983 |

|

SU1179228A1 |

| Устройство для контроля видеосигнала | 1982 |

|

SU1069190A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЙ | 1992 |

|

RU2051416C1 |

Авторы

Даты

1980-05-25—Публикация

1977-07-12—Подача