jib

СО

ij

4 СП

СО

1434453

Изобретение относится к специализированным средствам автоматики и вычислительной техники, предназначенноко эл

ному входу элемента И 31, второй вход которого объединен с инверсным входом элемента И 14, вторым входом элемен

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный анализатор плотности распределения амплитуд | 1981 |

|

SU1001110A1 |

| Адаптивный амплитудный анализатор | 1982 |

|

SU1078435A1 |

| АНАЛИЗАТОР СЛУЧАЙНЫХ ПРОЦЕССОВ | 1991 |

|

RU2012052C1 |

| Цифровой анализатор спектра | 1987 |

|

SU1413545A1 |

| Устройство для контроля и управления технологическими процессами | 1984 |

|

SU1193641A1 |

| Многофункциональный анализатор случайных процессов | 1986 |

|

SU1399766A1 |

| Адаптивный анализатор плотности распределения вероятностей | 1986 |

|

SU1310841A1 |

| Устройство автоматизированной подготовки программ для станков с ЧПУ | 1986 |

|

SU1354160A1 |

| Устройство для обучения | 1987 |

|

SU1559366A1 |

| Цифровой генератор | 1986 |

|

SU1347164A1 |

Изобретение относится к специализированным средствам автоматики и вычислительной техники, предназначенным для вычисления плотности распределения вероятностей и ее параметров в условиях недостатка информации о свойствах сигнала. С целью по- вьппения точности вычислений в условиях недостатка априорной информации о частотных и амплитудных свойствах сигнала в анализатор введены второй регистр микрокоманд, последовательно соединенные блок выборки и запоминания, блок вычитания, первый коммутатор, дискр;иинатор знака, элемент 2И-Ш1И, цифроаналоговый преобразователь и второй коммутатор. При этом выходы коммутаторов подключены соот- ветственно к информационному и опор- g ному входам аналого-цифрового преобразователя. 1 з.п. ф-лы, 3 ил. (Л

ным для определения характеристик слу-, та И 19 и подключен к инверсному вычайных процессов в условиях недостатка априорной информации, например, в океанологии, радиофизике, системах связи;

Целью изобретения является повышение точности оценки плотности распределения вероятности.

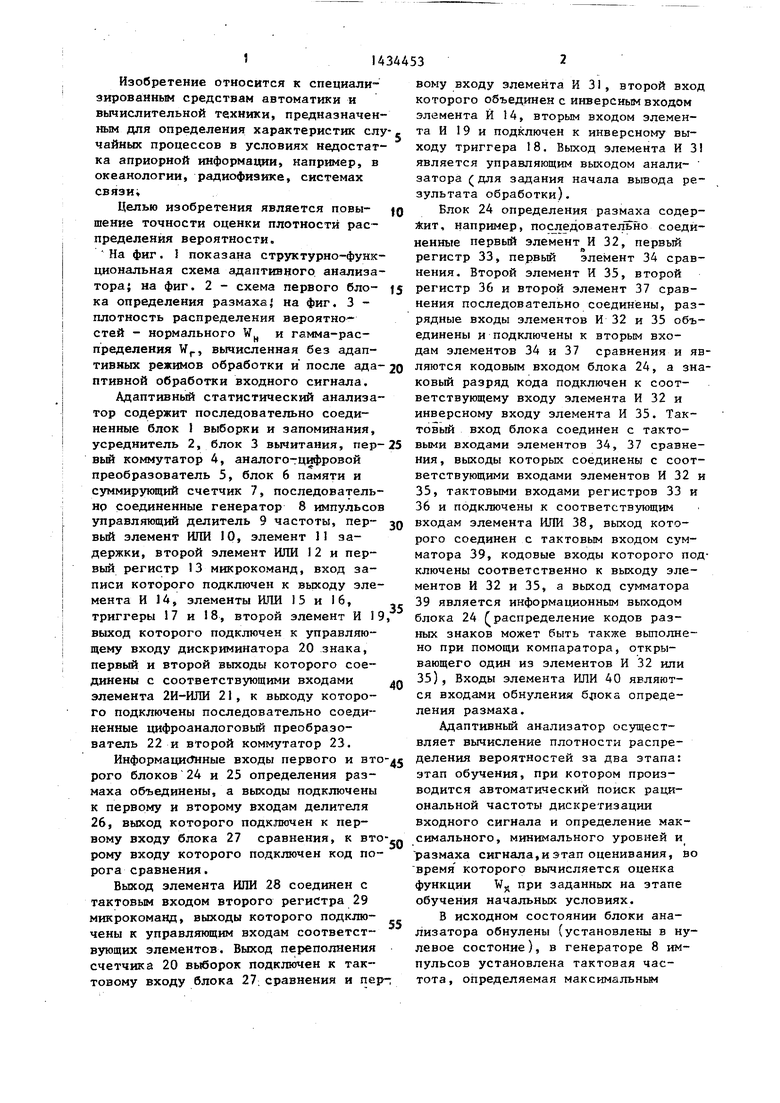

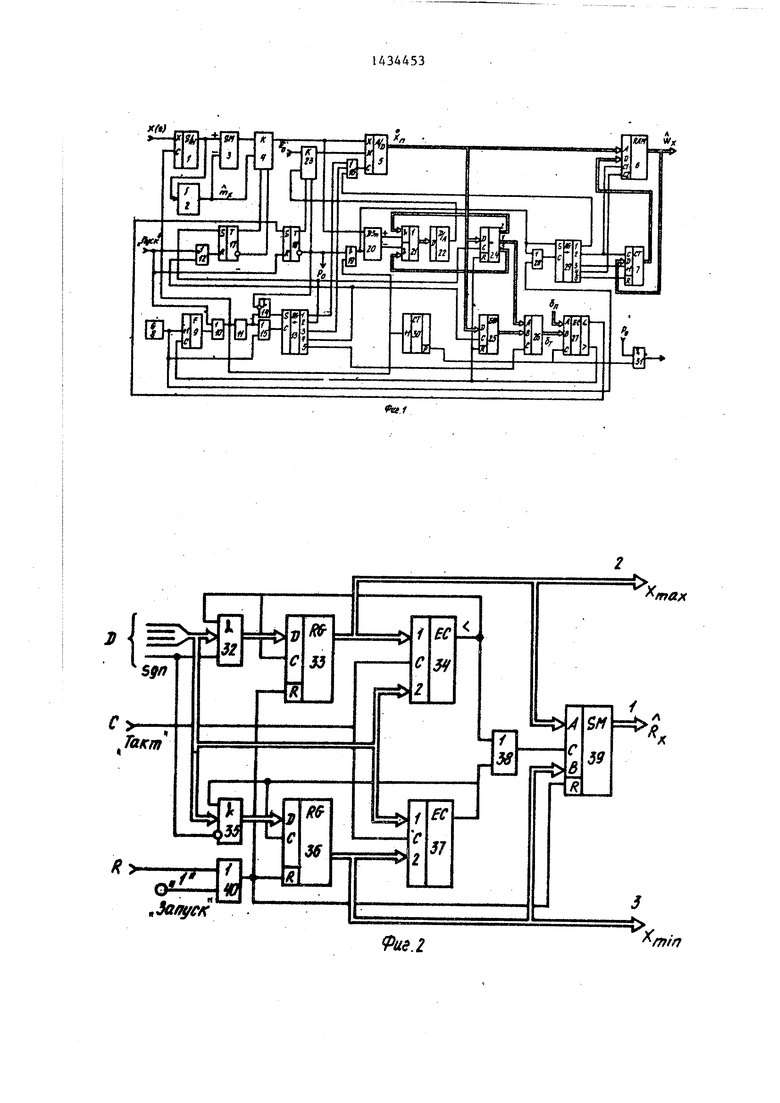

На фиг. 1 показана структурно-функциональная схема адаптивного анализаходу триггера 18. Выход элемента И 3 является управляющим выходом анали- затора (для задания начала вьшода ре зультата обработки),

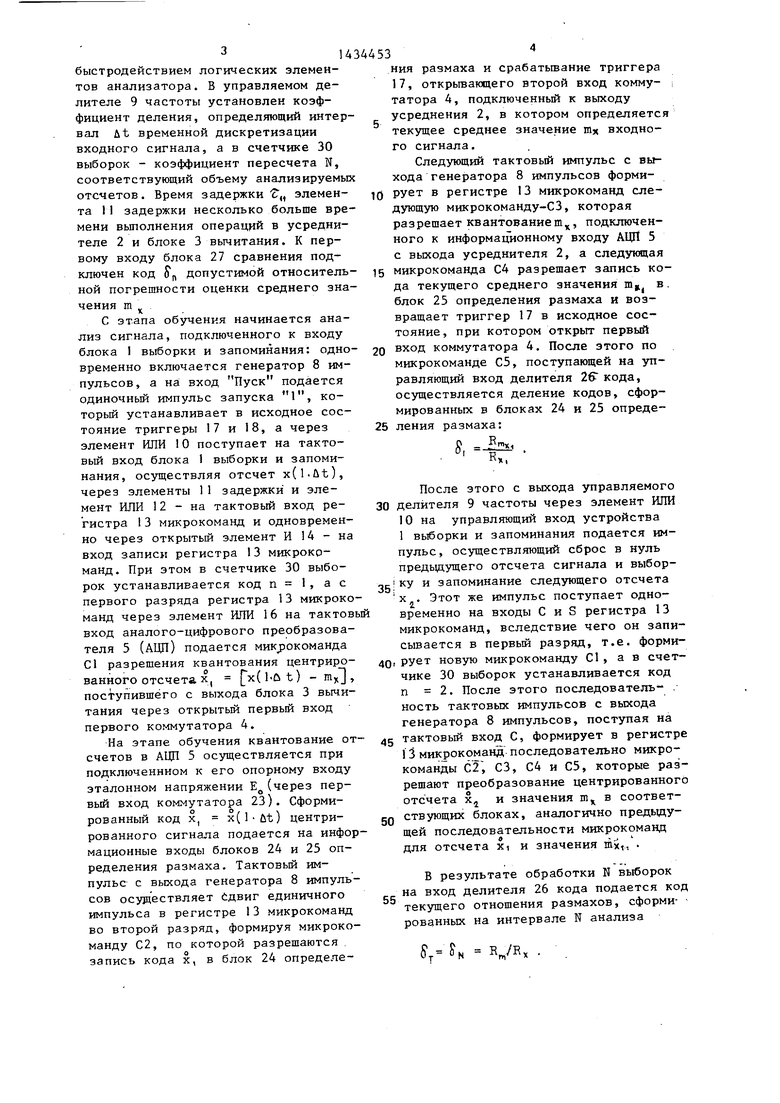

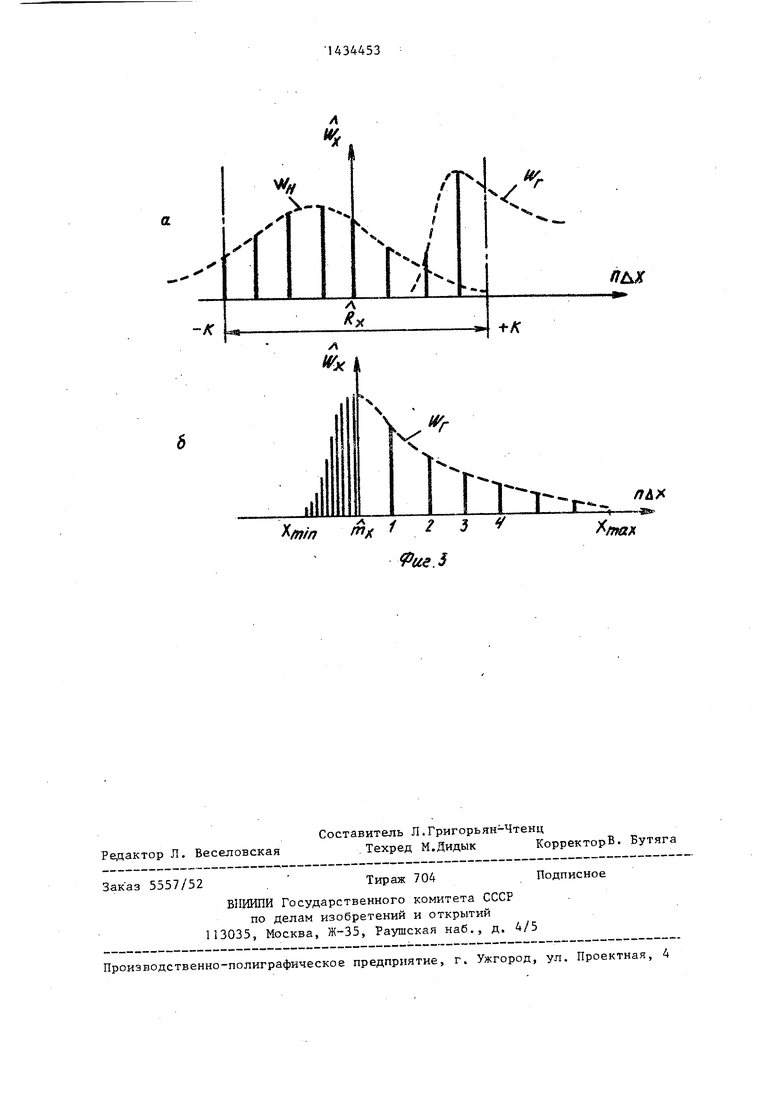

10 Блок 24 определения размаха содер жит, например, по следов aTejfbHo соеди ненные первый элемент И 32, первый регистр 33, первый элемент 34 срав нения. Второй элемент И 35, второй

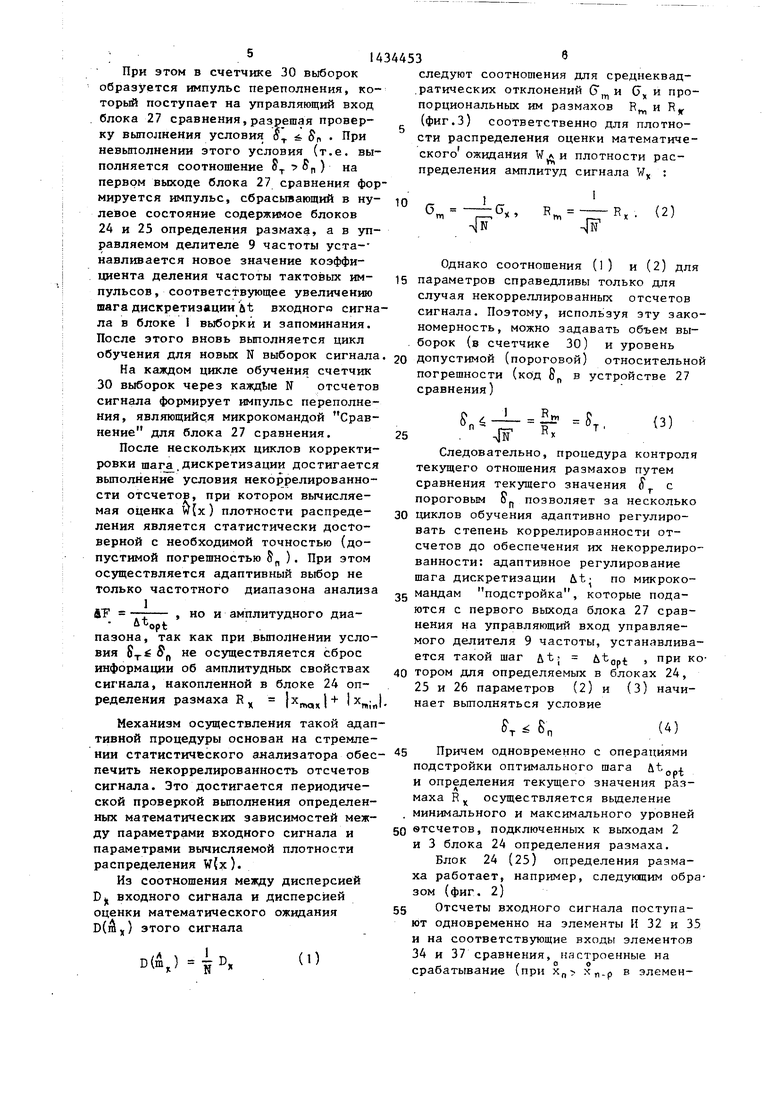

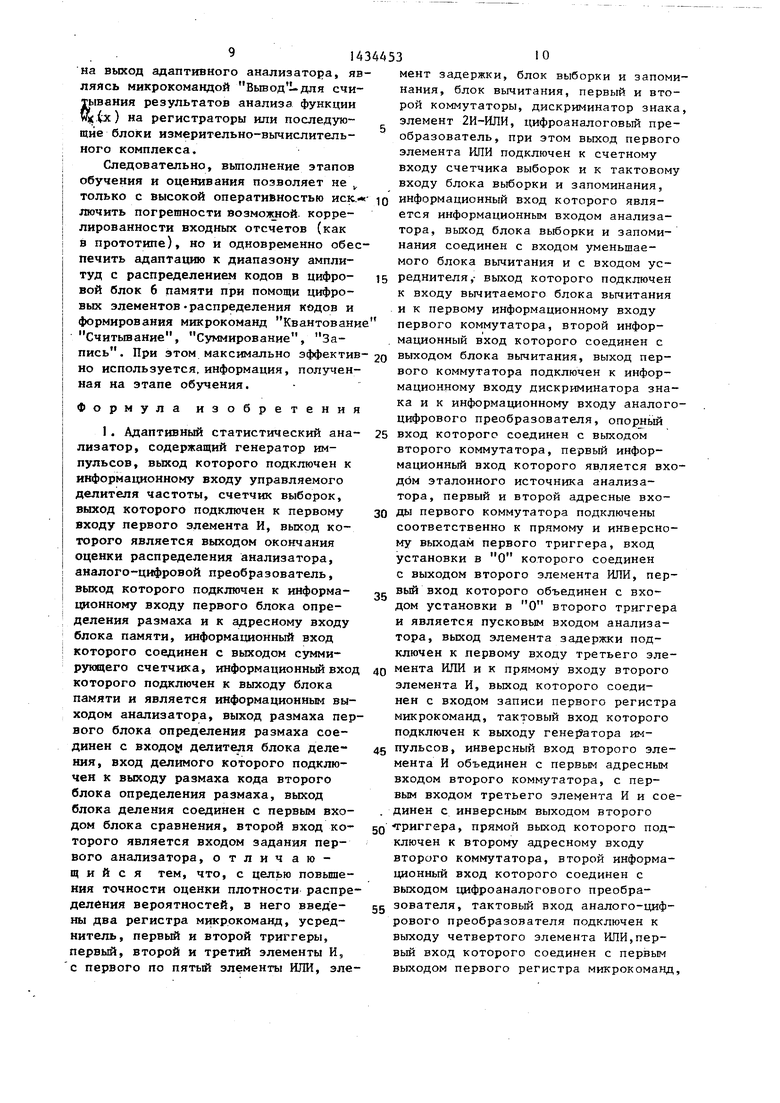

тора; на фиг. 2 - схема первого бло- 15 регистр 36 и второй элемент 37 срав- ка определения размаха| на фиг, 3 - плотность распределения вероятностей - нормального W и гамма-распределения W, вычисленная без адапнения последовательно соединены, разрядные входы элементов И 32 и 35 объединены и подключены к вторым входам элементов 34 и 37 сравнения и явтивных режимов обработки и после ада- 20 ляются кодовым входом блока 24, а зна- птивной обработки входного сигнала.

Адаптивный статистический анализатор содержит последовательно соединенные блок I выборки и запоминания, усреднитель 2, блок 3 вычитания, пер-25 вьй коммутатор 4, аналого-цифровой преобразователь 5, блок 6 памяти и суммирующий счетчик 7, последовательно соединенные генератор 8 импульсов управляющий делитель 9 частоты, пер- JQ вый элемент ШТИ 10, элемент 11 задержки, второй элемент ИЛИ 12 и первый регистр 13 микрокоманд, вход записи которого подключен к выходу элемента И 14, элементы ИЛИ 15 и 16, триггеры 7 и 18, второй элемент И 19, выход которого подключен к управляющему входу дискриминатора 20 знака, первый и второй выходы которого соединены с соответствующими входами элемента 2И-ИЛИ 21, к выходу которого подключены последовательно соединенные хщфроаналоговый преобразователь 22 и второй коммутатор 23.

35

40

ковый разряд кода подключен к соответствующему входу элемента И 32 и инверсному входу элемента И 35, Тактовый вход блока соединен с тактовыми входами элементов 34, 37 сравнения, выходы которых соединены с соответствующими входами элементов И 32 и 35, тактовыми входами регистров 33 и 36 и подключены к соответствующим входам элемента ИЖ 38, вькод которого соединен с тактовым входом сумматора 39, кодовые входы которого подключены соответственно к выходу элементов И 32 и 35, а выход сумматора 39 является информационным выходом блока 24 распределение кодов разных знаков может быть также выполнено при помощи компаратора, открывающего один из элементов И 32 или 35), Входы элемента ИЛИ 40 являются входами обнуления бдюка определения размаха.

Адаптивный анализатор осуществляет вычисление плотности распреИнформациЛ1ные входы первого и деления вероятностей за два этапа:

рого блоков 24 и 25 определения размаха объединены, а выходы подключены к первому и второму входам делителя 26, выход которого подключен к первому входу блока 27 сравнения, к вто-, рому входу которого подключен код порога сравнения.

Выход элемента ИЛИ 28 соединен с тактовым входом второго регистра 29 микрокоманд, выходы которого подключены к управляющим входам соответствующих элементов. Выход переполнения счетчика 20 выборок подключен к тактовому входу блока 27, сравнения и пер-;

этап обучения, при котором производится автоматический поиск рациональной частоты дискретизации входного сигнала и определение максимального, минимального уровней и размаха сигнала,и этап оценивания, в время которого вычисляется оценка функции W при заданных на этапе обучения начальных условиях,

В исходном состоянии блоки анализатора обнулены (установлены в ну левое состоние), в генераторе 8 импульсов установлена тактовая частота, определяемая максимальньм

ходу триггера 18. Выход элемента И 3 является управляющим выходом анали- затора (для задания начала вьшода результата обработки),

Блок 24 определения размаха содержит, например, по следов aTejfbHo соединенные первый элемент И 32, первый регистр 33, первый элемент 34 сравнения. Второй элемент И 35, второй

регистр 36 и второй элемент 37 срав-

нения последовательно соединены, разрядные входы элементов И 32 и 35 объединены и подключены к вторым входам элементов 34 и 37 сравнения и являются кодовым входом блока 24, а зна-

ковый разряд кода подключен к соответствующему входу элемента И 32 и инверсному входу элемента И 35, Тактовый вход блока соединен с тактовыми входами элементов 34, 37 сравнения, выходы которых соединены с соответствующими входами элементов И 32 и 35, тактовыми входами регистров 33 и 36 и подключены к соответствующим входам элемента ИЖ 38, вькод которого соединен с тактовым входом сумматора 39, кодовые входы которого подключены соответственно к выходу элементов И 32 и 35, а выход сумматора 39 является информационным выходом блока 24 распределение кодов разных знаков может быть также выполнено при помощи компаратора, открывающего один из элементов И 32 или 35), Входы элемента ИЛИ 40 являются входами обнуления бдюка определения размаха.

Адаптивный анализатор осуществляет вычисление плотности распределения вероятностей за два этапа:

этап обучения, при котором производится автоматический поиск рациональной частоты дискретизации входного сигнала и определение максимального, минимального уровней и размаха сигнала,и этап оценивания, во время которого вычисляется оценка функции W при заданных на этапе обучения начальных условиях,

В исходном состоянии блоки анализатора обнулены (установлены в нулевое состоние), в генераторе 8 импульсов установлена тактовая частота, определяемая максимальньм

быстродействием логических элементов анализатора. В управляемом делителе 9 частоты установлен коэффициент деления, определяющий интервал At временной дискретизации входного сигнала, а в счетчике 30 выборок - коэффициент пересчета N, соответствующий объему анализируемы отсчетов. Время задержки б,, элемента 1 задержки несколько больше времени вьтолнения операций в усреднителе 2 и блоке 3 вычитания. К первому входу блока 27 сравнения подключен код У допустимой относительной погрешности оценки среднего значения m

С этапа обучения начинается анализ сигнала, подключенного к входу блока I выборки и запоминания: одновременно включается генератор 8 импульсов, а на; вход Пуск подается одиночньй импульс запуска 1, который устанавливает в исходное состояние триггеры 17 и 18, а через элемент ИЛИ 10 поступает на тактовый вход блока 1 выборки и запоминания, осуществляя отсчет x(l.Ut), через элементы 1 1 задержки и элемент ИЛИ 12 - на тактовый вход регистра 13 микрокоманд и одновременно через открытый элемент И 14 - на вход записи регистра 13 микрокоманд. При этом в счетчике 30 выборок устанавливается код п 1, ас первого разряда регистра 13 микрокоманд через элемент ИЛИ 16 на тактов вход аналого-цифрового преобразователя 5 (АЦП) подается микрокоманда С1 разрешения квантования центрированного отсчета х, x(but) - m, поступившего с выхода блока 3 вычитания через открытьй первьй вход первого коммутатора 4.

На этапе обучения квантование отсчетов в АЦП 5 осуществляется при подключеннном к его опорному входу эталонном напряжении Е(через первый вход коммутатора 23). Сформированный код X, x(l ut) центрированного сигнала подается на информационные входы блоков 24 и 25 определения размаха. Тактовьй импульс с выхода генератора 8 импульсов осуществляет йдвиг единичного импульса в регистре 13 микрокоманд во второй разряд, формируя микрокоманду С2, по которой разрешаются запись кода х, в блок 24 определения размаха и срабатьтание триггера 17, открьгеающего второй вход комму- i татора 4, подключенньй к выходу усреднения 2, в котором определяется текущее среднее значение Шх входного сигнала.

Следующий тактовьй импульс с выхода генератора 8 импульсов формирует в регистре 13 микрокоманд следующую мккрокоманду-СЗ, которая разрешает квантованиет, подключенного к информационному входу АЦП 5 с выхода усреднителя 2, а следующая

микрокоманда С4 разрешает запись кода текущего среднего значения т в. блок 25 определения размаха и возвращает триггер 17 в исходное состояние, при котором открыт первый

вход коммутатора 4. После этого по микрокоманде С5, поступающей на управляющий вход делителя 26 кода, осуществляется деление кодов, сформированных в блоках 24 и 25 определения размаха:

После этого с выхода управляемого 30 делителя 9 частоты через элемент ИЛИ 10 на управляющий вход устройства 1 выборки и запоминания подается импульс, осуществляющий сброс в нуль предыдущего отсчета сигнала и выбор35;

ку и запоминание следующего отсчета X . Этот же импульс поступает одновременно на входы С и S регистра 13 микрокоманд, вследствие чего он записывается в первьй разряд, т.е. форми40 рует новую микрокоманду С1, а в счетчике 30 выборок устанавливается код п 2. После этого последователь . ность тактовых импульсов с выхода генератора 8 импульсов, поступая на

45 тактовьй вход С, формирует в регистре 13 микрокоманд последовательно микрокоманды С2, СЗ, С4 и С5, которые разрешают преобразование центрированного отсчета х и значения ш в соответствующих блоках, аналогично предьщу50

щей последовательности микрокоманд для отсчета xi и значения шх,,

В результате обработки N выборок на вход делителя 26 кода подается код текущего отношения размахов, сформи- рованных на интервале N анализа

6,N . .

При этом в счетчике 30 выборок образуется импульс переполнения, который поступает на управляющий вход блока 27 сравнения,разрешая проверку выполнения условия а 8 При невьшолнении этого условия (т.е. выполняется соотношение S : п ) нэ первом выходе блока 27 сравнения формируется импульс, сбрасьшающий в нулевое состояние содержимое блоков 24 и 25 определения размаха, а в управляемом делителе 9 частоты уста-- навливается новое значение коэффициента деления частоты тактовых импульсов, соответствующее увеличению шага дискретизации ut входного сигнала в блоке 1 выборки и запоминания. После этого вновь выполняется цикл

следуют соотношения для среднеквад- ,ратических отклонений 6, и G и пропорциональных им размахов R и R (фиг.З) соответственно для плотности распределения оценки математического ожидания WA и плотности рас1

пределения амплитуд сигнала W :

10

С5. -

m г- -ч л|К

G.,

«т

(2)

Однако соотношения (l) и (2) для 15 параметров справедливы только для случая некорреллированных отсчетов сигнала. Поэтому, используя эту закономерность, можно задавать объем вы. борок (в счетчике 30) и уровень обучения для новых N выборок сигнала. 2о допустимой (пороговой) относительной На каждом цикле обучения счетчик погрешности (код 8„ в устройстве 27

сравнения)

30 выборок через каждЬге N отсчетов сигнала формирует импульс переполнения, являющийся микрокомандой Сравнение для блока 27 сравнения.

После нескольких циклов корректировки marj.дискретизации достигается выполнение условия некоррелированности отсчетов, при котором вычисляемая оценка w(x) плотности распределения является статистически достоверной с необходимой точностью (допустимой погрешностью §„ ). При этом осуществляется адаптивный выбор не

25

S,

л|

(3)

Следовательно, процедура контроля текущего отношения размахов путем сравнения текущего значения S с пороговым Sf, позволяет за несколько 30 циклов обучения адаптивно регулировать степень коррелированности отсчетов до обеспечения их некоррелированности: адаптивное регулирование шага дискретизации &t; по микрокотолько частотного диапазона анализа мандам подстройка, которые подаiT

&t

opt

, но и амплитудного диапазона, так как при вьшолнении условия S-r п ие осуществляется сброс информации об амплитудных свойствах

сигнала, накопленной в блоке 24 оп-

ределения размаха R t moxl niirt - нает выполняться условие

ются с первого выхода бл нения на управляющий вход мого делителя 9 частоты, ется такой шаг ut; t 40 тором для определяемых в 25 и 26 параметров (2)

т Sn

(4)

Механизм осуществления такой адаптивной процедуры основан на стремлении статистического анализатора обес- 45 Причем одновременно с операциями

подстройки оптимального шага it,

печить некоррелированность отсчетов сигнала. Это достигается периодической проверкой вьтолнения определенных математических зависимостей между параметрами входного сигнала и параметрами вычисляемой плотности распределения W(x).

Из соотношения между дисперсией Dj( входного сигнала и дисперсией оценки математического ожидания D(AX) этого сигнала

op-t

и определения текущего значения размаха R осуществляется вьщеление минимального и максимального уровней

50 втсчетов, подключенных к вьгкодам 2 и 3 блока 24 определения размаха.

Блок 24 (25) определения размаха работает, например, следукщкм обр зом (фиг. 2)

55 Отсчеты входного сигнала поступают одновременно на элементы И 32 и 3 и на соответствующие входьг элементов 34 и 37 сравнения, настроенные на срабатывание (при х,, х„.р в элеменD(m,)

(О

следуют соотношения для среднеквад- ,ратических отклонений 6, и G и пропорциональных им размахов R и R (фиг.З) соответственно для плотности распределения оценки математического ожидания WA и плотности рас1

пределения амплитуд сигнала W :

С5. -

m г- -ч л|К

G.,

«т

(2)

Однако соотношения (l) и (2) для параметров справедливы только для случая некорреллированных отсчетов сигнала. Поэтому, используя эту закономерность, можно задавать объем вы25

S,

л|

(3)

Следовательно, процедура контроля текущего отношения размахов путем сравнения текущего значения S с пороговым Sf, позволяет за несколько 30 циклов обучения адаптивно регулировать степень коррелированности отсчетов до обеспечения их некоррелированности: адаптивное регулирование шага дискретизации &t; по микроко

нает выполняться условие

ются с первого выхода блока 27 сравнения на управляющий вход управляемого делителя 9 частоты, устанавливается такой шаг ut; tgn , при ко- 40 тором для определяемых в блоках 24, 25 и 26 параметров (2) и (3) начи т Sn

(4)

дновременно с операциями

подстройки оптимального шага it,

op-t

и определения текущего значения размаха R осуществляется вьщеление минимального и максимального уровней

0 втсчетов, подключенных к вьгкодам 2 и 3 блока 24 определения размаха.

Блок 24 (25) определения размаха работает, например, следукщкм образом (фиг. 2)

5 Отсчеты входного сигнала поступают одновременно на элементы И 32 и 35 и на соответствующие входьг элементов 34 и 37 сравнения, настроенные на срабатывание (при х,, х„.р в элементе 34, а при в элементе 37 сравнения). Результат текущего сравнения поступает на один из входов элемента И 32 (35) и на тактовый вход регистра 33 (36), в котором запоминается новое экстремальное значение отсчета, а через элемент ИЛИ 38 управляющий импульс разрешает операцию сложения в сумматоре 39, в ко- тороМдформируется новое значение размаха R . Перед началом работы и в течение циклов обучения элементы устанавливаются в нулевое состояние по импульсам пуска или обнуления, поступающим через элемент ИЛИ 40. При

Rr

вьшолнении условия

регистрах 33 и 36 остаются записанные экстремальные значения (минимальные и максимальное) кодов от- .счетов, необходимые для использования на цикле оценивания.

Выполнение условия (4) в блоке 27 сравнения характеризует окончание циклов обучения: на втором выходе блока 27 сравнения формируется микрокоманда Начало оценивания, которая подается на второй вход триггера 18.

На этапе оценивания опорньй вход АЦП 5 подключен к выходу цифроана- логового преобразователя 22, закрыт элемент И 14 и открыты элемент: И 31

элемент И 19, через который импульс ячейку блока 6 памяти, а по микрокоманде С5 осуществляется обнуление суммирующего счетчика 7,

дискретизации подается для записи в первый разряд регистра 29 микрокоманд .

Одновременно первый импульс дискретизации с выхода управляемого делителя 9 частоты поступает на вход счетчика 30 выборки, устанавливая его содержимое равным п 1, и на управляющий вход устройства 1 выборки и запоминания, на выходе которого формируется отсчет сигнала х. х и( 1 ). Блок 3 вычитания осуществляет центрирование с использованием оценки математического ожидания

Vл

л

т.

/ X.

z

v i

v i

где Z - знаковая функция (sgn +

или sgn -1 ).

Аналогично формируется ряд отсчетов на -интервале анализа 1,Nj.

С выхода блока 3 вычитания каждый центрированный отсчет (Z-x) через коммутатор 4 подается на информационный, вход AUn 5 и на вход дискриминатора 20 знака, который срабатьшает, открывая первый или второй вход элемента 2И-ИЛИ 21, в зависимости от знака центрированного отсчета. При этом к опорному ВХОДУ АЦП 5 через элемент 2И-ИЛИ 2 , цифроаналоговьй преобразователь 22 и коммутатор 23 подключается напряжение х

или X

выхода 2 или 3 блока 24 (фиг. 2), задающее амплитудный диапазон квантования отсчета х в АЦП 5,

По микрокоманде С1 с первого выхода регистра 29 микрокоманд в АЦП 5 осуществляется преобразование отсчета х в код, который подключен к адресному входу блока 6 памяти. При сдвиге импульса в регистре 29 микрокоманд во второй разряд формируется микрокоманда С2, которая поступает на первый управляющий вход блока b памяти, разрешая считывание предыдущего содержимого ячейки, определяемой кодом адреса Ay , и его запись

в суммирующий счетчик 7. Следующий тактовый импульс, поступающий на вход с регистра 29 микрокоманд, формирует микрокоманду СЗ, разрешающую операцию суммирования в суммирующем

счетчике 7; его содержание увеличивается на единицу и становится равным W

+ 1. По микрокоманде С4 разрешазапись этого кода с выхода суммирующего счетчика 7 в ту же п-ю

Г|

а тс я

с ячейку блока 6 памяти, а по микроко

манде С5 осуществляется обнуление суммирующего счетчика 7,

Таким образом, дискрш- инатор 20 знака осуществляет подключение к опор40 ному входу АЦП 5 определенного уровня напряжения или с выхода АЦП 22 (в зависимости от знака анализируемого текущего отсчета к сигнала), т.е. управляет шагом кван4g тования по амплитуде и соответствующим распределением этих данных в оп-. ределенные ячейки блока памяти 6 (фиг. Зб). Благодаря этим операциям в блоке 6 памяти накапливается оценка

gQ функции W(х) по некоррелированным отсчетам, т.е. с высокой статистической достоверностью и в широком диапазоне амплитуд анализа вследствие накапливания отдельно левой и правой ветвей гистограммы (фиг.Зб).

После обработки TJ-ro отсчета сигнала в счетчике 30 выборок формируется импульс переполнения, который по- студает через открытый элемент И 31

55

на выход адаптивного анализатора, являясь микрокомандой Вьшод -для считывания результатов анализа функции Ц(.(л;) на регистраторы или последующие блоки измерительно-вычислительного комплекса.

Следовательно, вьшолнение этапов обучения и оценивания позволяет яе только с высокой оперативностью иск. лючить погрешности возможной корре- лированности входных отсчетов (как в прототипе), но и одновременно обеспечить адаптацию к диапазону амплитуд с распределением кодов в цифровой блок 6 памяти при помощи цифровых элементов-распределения кодов и формирования микрокоманд Квантование Считьшание, Суммирование, За

пись . При этом максимально зффектив- 2о выходом блока вычитания, выход перио используется, информация, полученная на этапе обучения.

Формула изобретения

35

вого коммутатора подключен к информационному входу дискриминатора знака и к информационному входу аналого цифрового преобразователя, опорный вход которого соединен с выходом второго коммутатора, первый информационный вход которого является вхо дом эталонного источника анализатора, первый и второй адресные вхо30 ДЫ первого коммутатора подключены соответственно к прямому и инверсному выходам первого триггера, вход установки в О которого соединен с выходом второго элемента ИЛИ, первый вход которого объединен с входом установки в О второго триггера и является пусковым входом анализатора, выход элемента задержки подключен к первому входу третьего эле4Q мента ИЛИ и к прямому входу второго элемента И, выход которого соединен с входом записи первого регистра микрокоманд, тактовый вход которого подключен к выходу гене1Уатора им45 пульсов, инверсный вход второго элемента И объединен с первым адресным входом второго коммутатора, с первым входом третьего элемента И и сое динен с инверсным выходом второго

5Q триггера, прямой выход которого подключен к второму адресному входу второго коммутатора, второй информационный вход которого соединен с выходом цифроаналоговorо преобразователя, тактовый вход аналого-цифрового преобразователя подключен к выходу четвертого элемента ИЛИ,первый вход которого соединен с первым выходом первого регистра микрокоманд

55

мент задержки, блок выборки и запоминания, блок вычитания, первый и второй коммутаторы, дискриминатор знака, элемент 2И-ИЛИ, цифроаналоговый преобразователь, при этом выход первого элемента ИЛИ подключен к счетному входу счетчика выборок и к тактовому входу блока выборки и запоминания,

информационный вход которого является информационным входом анализатора, выход блока выборки и запоминания соединен с входом уменьшаемого блока вычитания и с входом усреднителя,- выход которого подключен к входу вычитаемого блока вычитания и к первому информационному входу первого коммутатора, второй информационный вход которого соединен с

5

5

вого коммутатора подключен к информационному входу дискриминатора знака и к информационному входу аналого- цифрового преобразователя, опорный вход которого соединен с выходом второго коммутатора, первый информационный вход которого является входом эталонного источника анализатора, первый и второй адресные вхо0 ДЫ первого коммутатора подключены соответственно к прямому и инверсному выходам первого триггера, вход установки в О которого соединен с выходом второго элемента ИЛИ, первый вход которого объединен с входом установки в О второго триггера и является пусковым входом анализатора, выход элемента задержки подключен к первому входу третьего элеQ мента ИЛИ и к прямому входу второго элемента И, выход которого соединен с входом записи первого регистра микрокоманд, тактовый вход которого подключен к выходу гене1Уатора им5 пульсов, инверсный вход второго элемента И объединен с первым адресным входом второго коммутатора, с первым входом третьего элемента И и соединен с инверсным выходом второго

Q триггера, прямой выход которого подключен к второму адресному входу второго коммутатора, второй информационный вход которого соединен с выходом цифроаналоговorо преобразователя, тактовый вход аналого-цифрового преобразователя подключен к выходу четвертого элемента ИЛИ,первый вход которого соединен с первым выходом первого регистра микрокоманд.

5

второй выход которого подключен к входу установки в 1 первого триггера и к тактовому входу первого блока определения размаха, выход максимсшьного кода которого соединен с первым входом элемента 2И-ИЛИ, выход которого подключен к входу циф- роаналогового преобразователя, вто-. рой вход элемента 2И-ИЛЙ соединен с положительным выходом дискриминатора знака, отрицательный выход которого соединен с третьим входом элемента 2И-ИЛИ, четвертый вход которого под

ключен к выходу минимального кода nep-ig чающийся тем, что блок опревого блока определения размаха, входы установки в О первого и второго блоков определения размаха объединены и подключены к выходу Больше блока сравнения, тактовый вход которого соединен с выходом переполнения счетчика выборок, второй вход четвертого элеме1|та ИЛИ подключен к третьему выходу первого регистра микрокоманд, четвертый выход которого соединен с вторым входом второго элемента ИЛИ и тактовым входом второго блока определения размаха, информационный вход которого подключен к выходу аналого-цифрового преобразователя, выход первого элемента ИЛИ соединен с входом элемента задержки и с вторым входом третьего элемента И, выход которого подключен к тактовому входу дискриминатора знака, к первому входу пятого элемента ИЛИ и входу записи второго регистра микрокоманд, тактовый вход которого соединен с выходом пятого элемента ИЛИ, второй вход которого подключен к выходу генератора импульсов ,третий вход четвертого элемента ИЛИ соединен с первым выходом второго регистра микрокоманд, второй выход которого подключен к входу считывания блока памяти и тактовому входу суммирующего счетчика, счетный вход которого соединен с третьим выходом второго регистра микрокоманд, четвертый выход которого подключен к входу счи- тьшания блока памяти, пятый выход второго регистра микрокоманд соединен с входом установки в О суммирующего счетчика, выход Меньше или

20

25

30

35

40

45

50

деления размаха содержит два элемента И, два регистра, два 3(лемента сравнения, два элемента ИЛИ и сумматор , выход которого является выходом размаха кода блока, тактовыми входами которого являются входы элементов сравнения, выход Меньше первого элемента сравнения соединен с входом синхронизации первого регистра и с первыми входами первого элемента ИЛИ и первого элемента И, выход которого соединен с информационным входом первого регистра, выход которого соединен с первыми входами сумматора и первого элемента сравнения и является выходом максимального кода блока, входом установки в О которого является первый вход второго элемента ИЛИ, вьпсод которого под- лючен к входам сброса регистров и сумматоров, выход второго регистра соединен с первь м входом второго элемента сравнения и с вторым входом сумматора и является выходом минимального кода блока, информационный вход .которого подключен к вторым информа- цио-нным входам первого и второго элементов сравнения и к второму входу первого и первому входу второго элементов И, выход которого соединен с информационным входом второго регистра, выход Больше или равно втб- рого элемента сравнения подключен к второму входу первого элемента ИЛИ, к входу синхронизации второго регистра и к второму входу второго элемента И, второй вход второго элемента ИЛИ является входом пуска блока.

равно блока сравнения подключен

к входу установки в 1 второго счетчика, инверсный выход которого соединен с вторым входом первого элемента И, выход управляемого делителя частоты соединен с первым входом первого элемента ИЛИ, второй вход которого является входом пуска анализатора, пуска блока определения размаха, выход Больше блока сравнения подключен к тактовому входу управляемого делителя частоты.

5

0

5

0

5

0

деления размаха содержит два элемента И, два регистра, два 3(лемента сравнения, два элемента ИЛИ и сумматор , выход которого является выходом размаха кода блока, тактовыми входами которого являются входы элементов сравнения, выход Меньше первого элемента сравнения соединен с входом синхронизации первого регистра и с первыми входами первого элемента ИЛИ и первого элемента И, выход которого соединен с информационным входом первого регистра, выход которого соединен с первыми входами сумматора и первого элемента сравнения и является выходом максимального кода блока, входом установки в О которого является первый вход второго элемента ИЛИ, вьпсод которого под- лючен к входам сброса регистров и сумматоров, выход второго регистра соединен с первь м входом второго элемента сравнения и с вторым входом сумматора и является выходом минимального кода блока, информационный вход .которого подключен к вторым информа- цио-нным входам первого и второго элементов сравнения и к второму входу первого и первому входу второго элементов И, выход которого соединен с информационным входом второго регистра, выход Больше или равно втб- рого элемента сравнения подключен к второму входу первого элемента ИЛИ, к входу синхронизации второго регистра и к второму входу второго элемента И, второй вход второго элемента ИЛИ является входом пуска блока.

KM

«ж

min - us.S

fmxK

| Авторское свидетельство СССР № 1135340, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Адаптивный анализатор плотности распределения амплитуд | 1981 |

|

SU1001110A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-10-30—Публикация

1987-04-13—Подача