(54) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ОДИНОЧНОГО ИМПУЛЬСА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выделения одиночного импульса | 1989 |

|

SU1621147A1 |

| Устройство для выделения одиночного импульса | 1978 |

|

SU744935A1 |

| Формирователь импульсов | 1989 |

|

SU1718368A1 |

| Устройство для обнаружения самовозбуждения блоков привода электронно-механических балансных часов | 1986 |

|

SU1365043A1 |

| Формирователь одиночного импульса | 1980 |

|

SU892677A2 |

| Формирователь одиночных импульсов | 1980 |

|

SU875605A1 |

| Устройство для синхронизации импульсов | 1985 |

|

SU1275746A1 |

| Устройство для контроля логических схем | 1978 |

|

SU799118A1 |

| Двоично-десятичный счетчик | 1977 |

|

SU743206A1 |

| Устройство для контроля и диагностики цифровых устройств | 1987 |

|

SU1583914A2 |

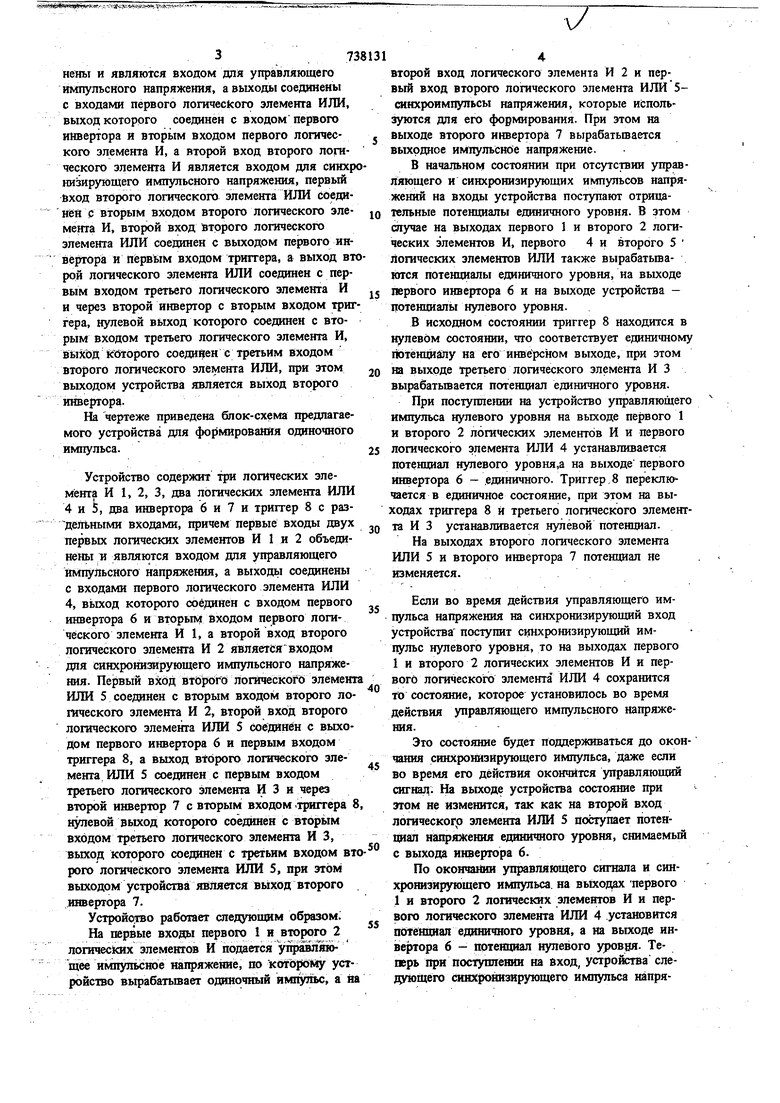

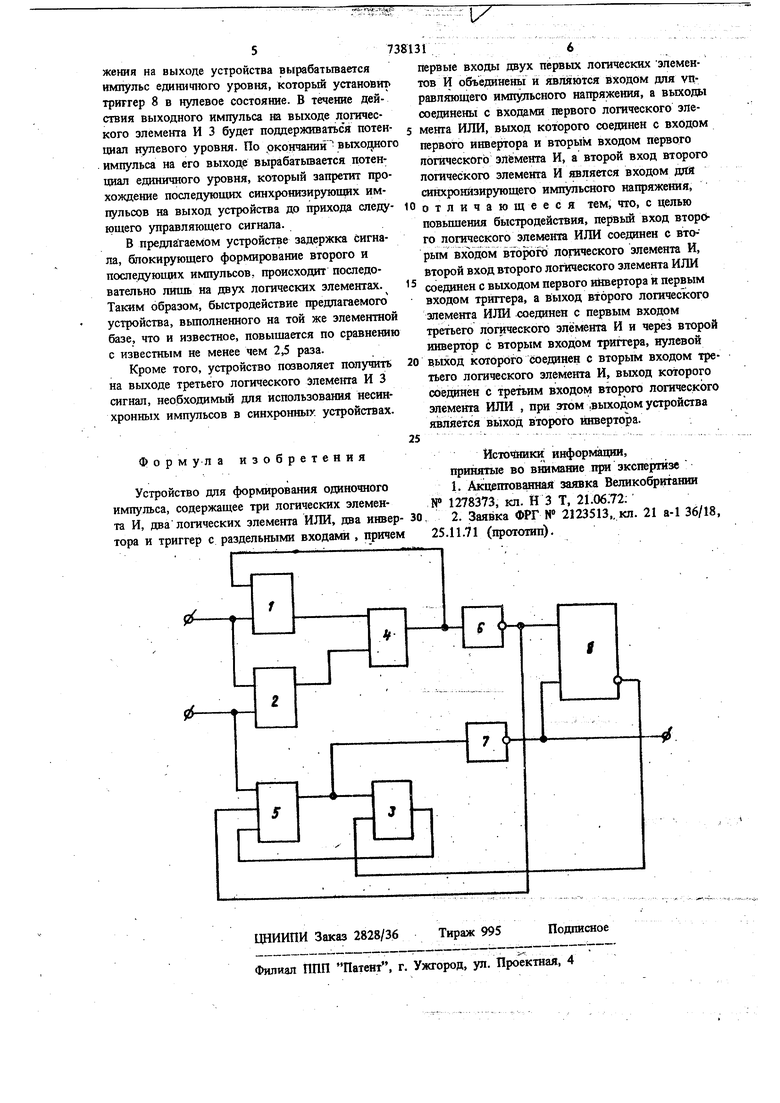

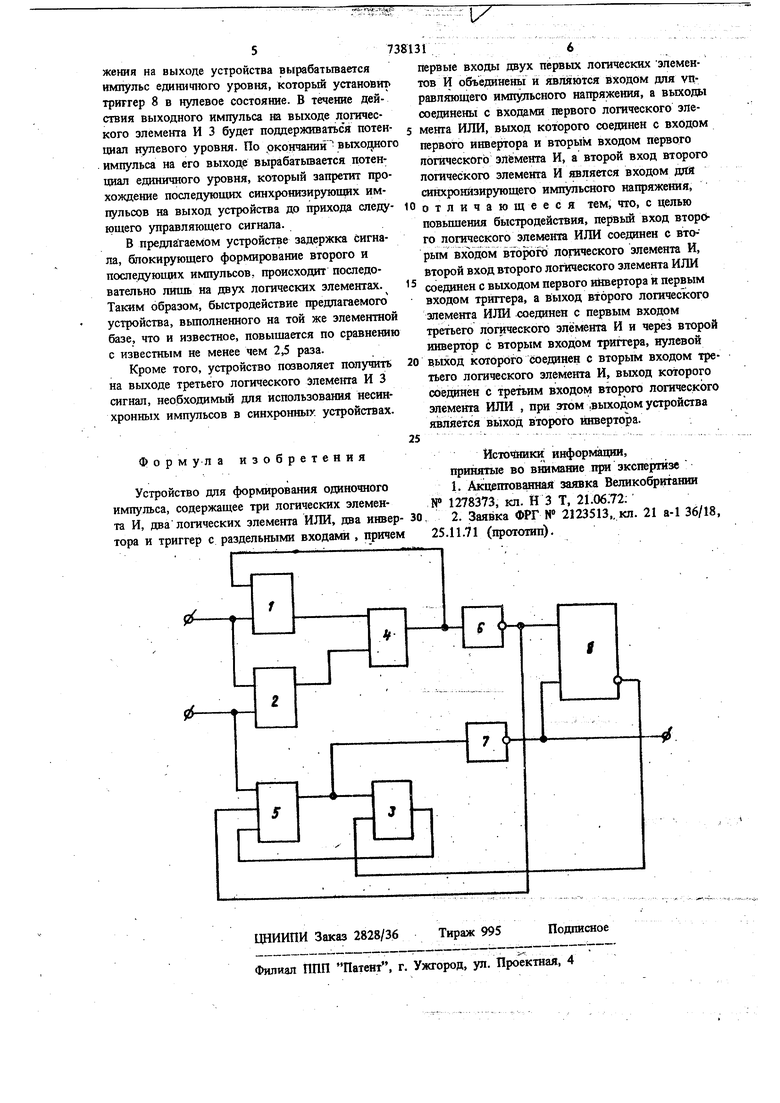

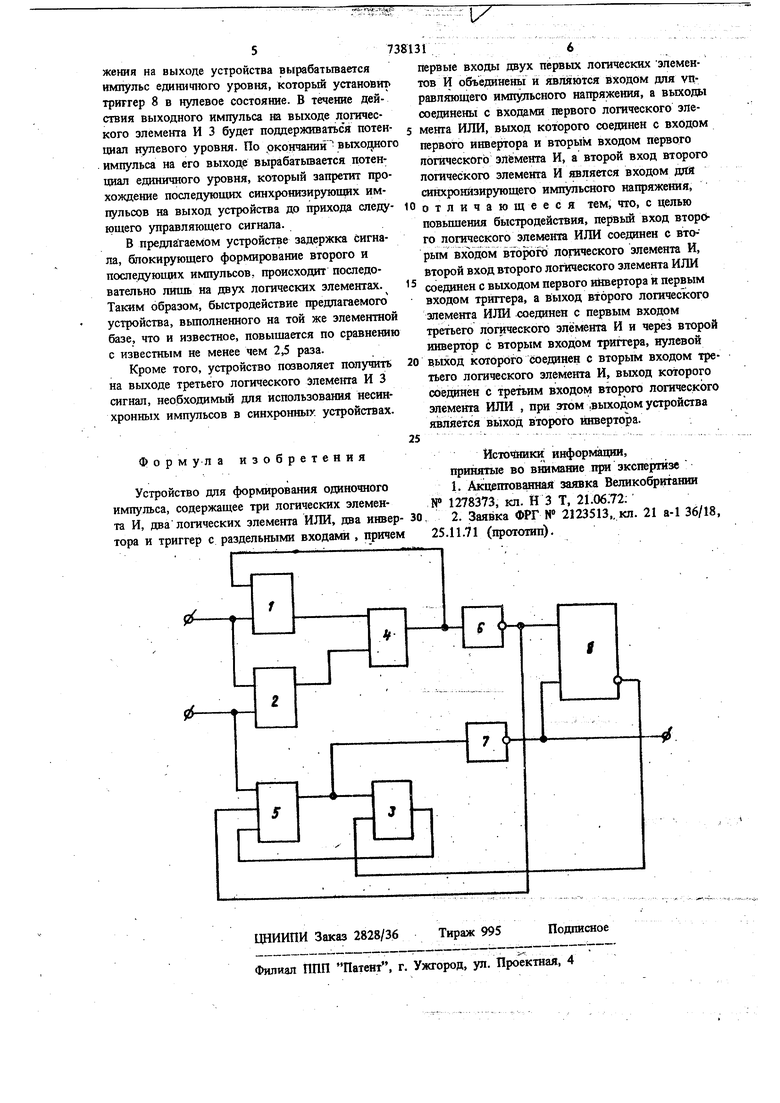

Изобретение относится К радиотехническим устройствам и может использоваться при построении управляющих систем, например, эцектронных вычислительных машин., Известно устройство для формирования, оди ночного импульса из непрерьтной серии синхро низирующих импульсов при поступлении на устройство управляющего Сигнала, содержащее триггеры и логические схемы И и ИЛИ 1. Недостатком этого устройства является низкое быстродействие из-за OTCJTTCTBHH цепей блокировки формирования первого и второго импульсов. Наиболее близким по технической сущности к предлагаемому является устройство для формирования одиночного импульса, содержащее три логических элемента И, два логических элемента ИЛИ, два инвертора и триггер с раздельными входами, причём первые входы двух первых логических элементов И объединены и являются входом для управляющего импульсно го напряжения, а выходы соединень с входами первого логического элемента ИЛИ, выход которого соединен с входом первого инвертора И вторым входом первого логического элемента И, а второй вход второго логического элемента И является входом для синхронизирующего им11уйьск6Т6 напрЖё1 т 2. Однако при поступлений на синхрбшзйрующий вход дагаюго устройства импульсов с . периодом повторения Тп 5Тз ( - время задержки распространешш сигналов на одном . логическом элементе) на выходе устройства вырабать1вается два импульса. Это происходит вследствие того, что сигнал, блокирующий формирование второго и последующих импульсов, вырабатьгеается с задержкой на пяти элементах. Целью изобрететшя является првыщениё быстродействия, а именно формирование сигналов, позволяющих производить перезапись информации из одного устройства в другое, которые работают в несинхронном . Цель достигается тем, что в устройстве для формирования одиночного импульса, содержащем три логических элемента И, два логических элемента ИЛИ, два инвертора и триггер с раздельными входами, ггричем первые входы двух первых логических элементов И объеди37йены и являются входом для управляющего импульсного напряжения, а выходы соединены с входами первого nonneckoro элемента ИЛИ, выход которого соединен с входом первого инвертора и вторым входом первого логического элемента И, а второй вход второго логического элемента И является входом для сиихр ниЬирующего импульсного напряжения, первый Вход второго логического элемента ИЛИ соедиHieft с вторым входом второго логического элемента И, второй вход второго логического элемента ИЛИ соединен с выходом первого инвертор и первым входом триггера, а выход вт рой логического элемента ИЛИ соединен с первым входом третьего логического элемента И и через второй инвертор с вторым входом триг гера, нупеъок выход которого соединен с вторым входом третьего логического элемента И, вЫхЬд которого соединен с третьим входом второго логического элемента ИЛИ, при этом выходом устройства является выход второго инвертора. На чертеже приведена блок-схема предлагаемого устройства для формирования одиночного импульса. Устройство содержит три логических элеMieHTa И 1, 2, 3, два логических элемента ИЛИ 4 и 5, два инвертора 6 и 7 и триггер 8 с раз дельными входами, причем первые Входы двух первых логических элементов И I и 2 объединены и являются входом для управляющего Импульсного напряжения, а выходь соединены с входами первого логического элемента ИЛИ 4, вьЕход которого соединен с входом первого инвертора 6 и вторым входом первого логического элеменга И 1, а второй вход второго логического элемента И 2 являетсявходом для синхронизирующего импульсного напряжения. Пе1)вый вход втЬрюгб логического элемент ИЛИ 5 соединен с вторым входом второго лошческого элемента И 2, второй вход второго логического элеменга ИЛИ 5 собдииеи с выходом первого инвертора 6 и первым входом триггера 8, а выход второго логического элемента ШШ 5 соединен с первым входом третьего логического элемента И 3 и череэ второй инвертор 7 с вторым входом .триггера 8 нулевой выход которого соединен с вторьш входом третьего логического элемента ИЗ, выход которого соединен с третьим входом вто рого логического элемента ИЛИ 5, при этОм выходом устройства является вь1ход второго инвертора 7. Устройство работает следующим образом: На первые входы первого 1 и второго 2 логических элементов И подается упрШйою пдае импульсное напряжение, по которому устройство вырабатывает одиночный имщгпъс, а йа второй вход логического элемента И 2 и первый вход второго логического элемента ИЛИ 5синхроимпульсы напряжения, которые используются для его формирования. При этом на выходе второго инвертора 7 вырабатьшается выходное импульсное напряжение. В начальном состоянии при отсутстаии управляющего и синхронизирующих импульсов напряжений на входы устройства поступают отрицательные потешшалы единичного уровня. В этом случае на выходах первого 1 и второго 2 логических элементов И, первого 4 и второго 5 логических элементов ИЛИ также вырабатьшаются потенциалы единичного уровня, на выходе первого инвертора 6 и на выходе устройства - потенциалы нулевого уровня. В исходном состоянии триггер 8 находится в 1 левОм состоянии, что соответствует единичному штёниийлу на его ииверсном выходе, при этом на выходе третьего логического элемента ИЗ вырабатьтается потенциал единичного уровня. При поступлегаш на устройство управляющего импульса нулевого уровня на выходе первого 1 и второго 2 логических элементов И и первого логического элемента ИЛИ 4 устанавливается потенциал нулевого уровня,а иа выходе первого инвертора 6 - .единичного. Триггер 8 переключается в единичное состояние, при этом на выходах триггера 8 и третьего логического элеменгта И 3 устанавливается нулевой потенциал. На выходах второго логического элемента ИЛИ 5 и второго инвертора 7 потенциал не изменяется. Если во время действия управляющего имгупъса напряжения на синхронизирующий вход устройства поступит синхронизирующий импульс нулевого уровня, то на выходах первого 1 и второго 2 логических элементов И и первого логического элемента ИЛИ 4 сохранится то состояние, которое установилось во время действия управляющего импульсного напряжения. Это состояние будет поддерживаться до окоичания синхроиизирующего импульса, даже если во время его действия окончится управляющий сигнал. На выходе устройства состояние при этом не изменится, так как на вход логическогр элемента ИЛИ 5 поступает потенциал напряжения единичного уровня, снимаемый с выхода инвертора 6. По окончании управляющего сигнала и синхронизирующего импульса, на выходах первого 1 и второго 2 логических элементов И и первого логического элемента ИЛИ 4 устаиовится потенциал единичного зфовня, а иа выходе инвертора 6 - потенциал нулевого уровня. Теперь при поступлении на вход, устро11ства следующего сзгах юнизирующего импульса иапря57жения на выходе устройства вырабатьтается импульс едит1чиого уровня, который устанойит триггер 8 в нулевое состояние. В течение действия выходного импульса на выходе логического элемента И 3 будет поддерживаться потенциал нулевого уровня. По ркончаний выхофюго импульса на его выходе вырабатьшается потенциал единичного уровня, который запретит прохождение последующих синхронизирующих импульсов на выход устройства до прихода следующего управляющего сигнала. В предлагаемом устройстве задержка сигнала, блокирующего формирование второго и последующих импульсов, происходит последовательно лищь на двух логических элементах. Таким образом, быстродействие предлагаемого устройства, вьшолненного на той же элементной базе, что и известное, повыщается по сравнению с известным не менее чем 2,5 раза. Кроме того, устройство позволяет получить на выходе третьего логического элемента И 3 сигнал, необходимый для использования несинхронных импульсов в синхронных устройствах.

Форм у л а изобретения

Устройство для формирования одиночного импульса, содержащее три логических элемента И, два логических элемента ИЛИ, два инвер- 30 тора и триггер с раздельными входами , причем

Источники информации, принятые во внимание при экспертизе

1,Акцептованная заявка Великобритании № 1278373, кл. ИЗ Т, 21.06:72;

Авторы

Даты

1980-05-30—Публикация

1973-04-06—Подача