(5) ФОРМИРОВАТЕЛЬ ОДИНОЧНОГО ИМПУЛЬСА

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь одиночного импульса | 1987 |

|

SU1503065A1 |

| Многопрограмный распределитель импульсов | 1987 |

|

SU1443163A1 |

| Устройство фиксации переходов через нуль периодического сигнала | 1984 |

|

SU1187145A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Формирователь одиночного импульса | 1989 |

|

SU1621156A1 |

| Измеритель временных интервалов | 1988 |

|

SU1672411A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| Устройство измерения времени ограничения тока транзисторными коммутаторами систем зажигания | 1989 |

|

SU1758279A1 |

| Формирователь одиночных импульсов | 1978 |

|

SU999148A1 |

| Формирователь импульсов | 1990 |

|

SU1711325A1 |

Изобретение относится к импульсно технике и может быть использовано в цифровой вычислительной технике. По основному авт.св. № 595В52 известен формирователь одиночного им- .пульса, который содержит D-триггер, информационный вход которого соедине с источником управляющего сигнала, и вертор, вход которого соединен с источником тактовых импульсов и с управляющим входом D-триггера, эле мент И-НЕ, первый вход которого соединен с выходом инвертора, второй вход - с прямым выходом D-триггера, RS-триггер, единичный вход которого соединен с источником управляющего сигнала, нулевой вход - с выходом эл мента И-НЕ, а единичный выход - с нулевым входом D-триггераDl Недостатком известного формирователя является невозможность формирования одиночного импульса различной длительности при наличии только одно тактовой частоты. Цель изобретения - расширение функциональных возможностей формировйтеля путем формирования одиночного импульса различной длительности под воздействием управляющих сигналов с использованием одной тактовой частоты. Поставленная цель достигается тем, что в формирователь одиночного импульса, содержащий О-триггер, информационный вход которого соединен с источником управляющего сигнала, инвертор, вход которого соединен с источником тактовых импульсов и с управляющим входом 0-триггера, элемент И-НЕ, первый вход которого соединен с выходом инвертора, второй вход с прямым выходом 0-триггера, RSтриггер, единичный вход которого соединен с источником управляющего сигнала, нулевой вход - с выходом элемента И-НЕ, а единичный выход с нулевым входом 0-триггёра, введены элемент И, счетчик, дешифратор, элемент И-ИЛИ, причем первый вход элемента И соединен с прямым выходом D-триггера, второй вход - с источником тактовых импульсов, а выход с входом счетчика, нулевой вход которого соединен с инверсным выходом D-триггера, входы дешифратора соединены с выходами счетчика, а выходы дешифратора соединены с первыми входами групп И элемента И-ИЛИ, вторые входы которых соединены с управляющими шинами, а выход элемента И-ИЛИ соединен с третьим входом элемента И-НЕ.

Введение в формирователь одиночного импульса элемента И, счетчика, дешифратора, элемента И-ИЛИ и их соответствующих соединений позволяет получить сигнал обратной связи, формирующий длительность выходного импульса и прекращающий работу, устройства до возникновения следующего сигнала на управляющем входе.

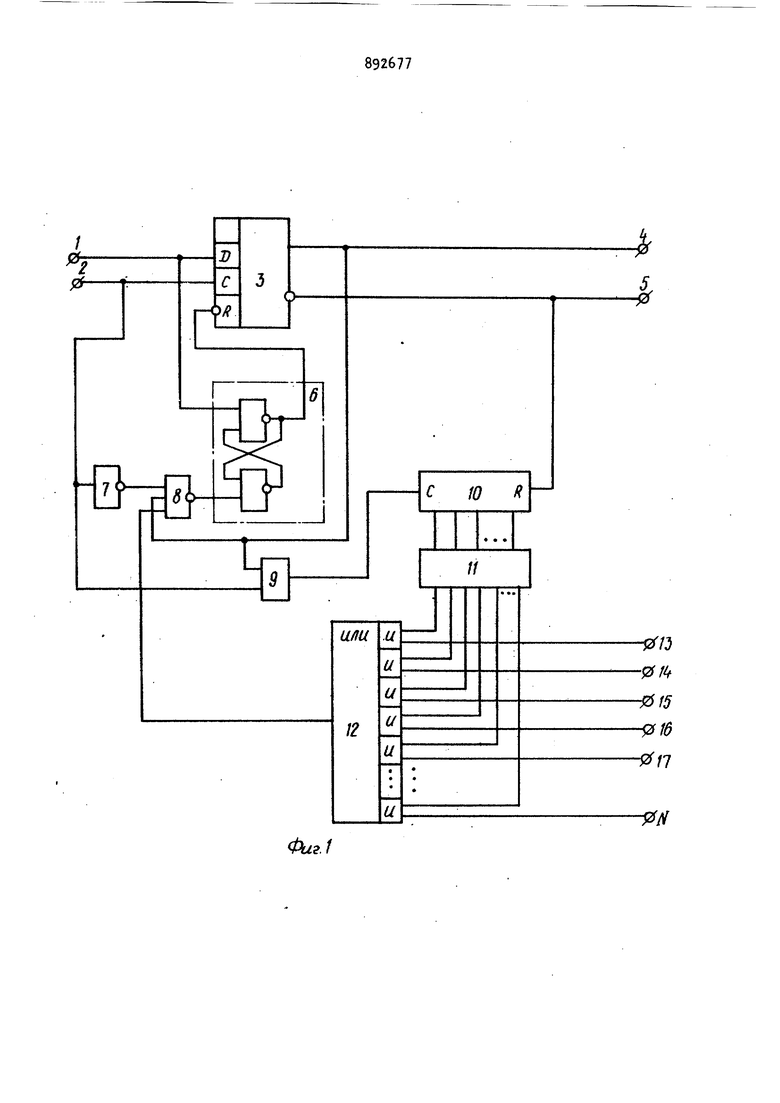

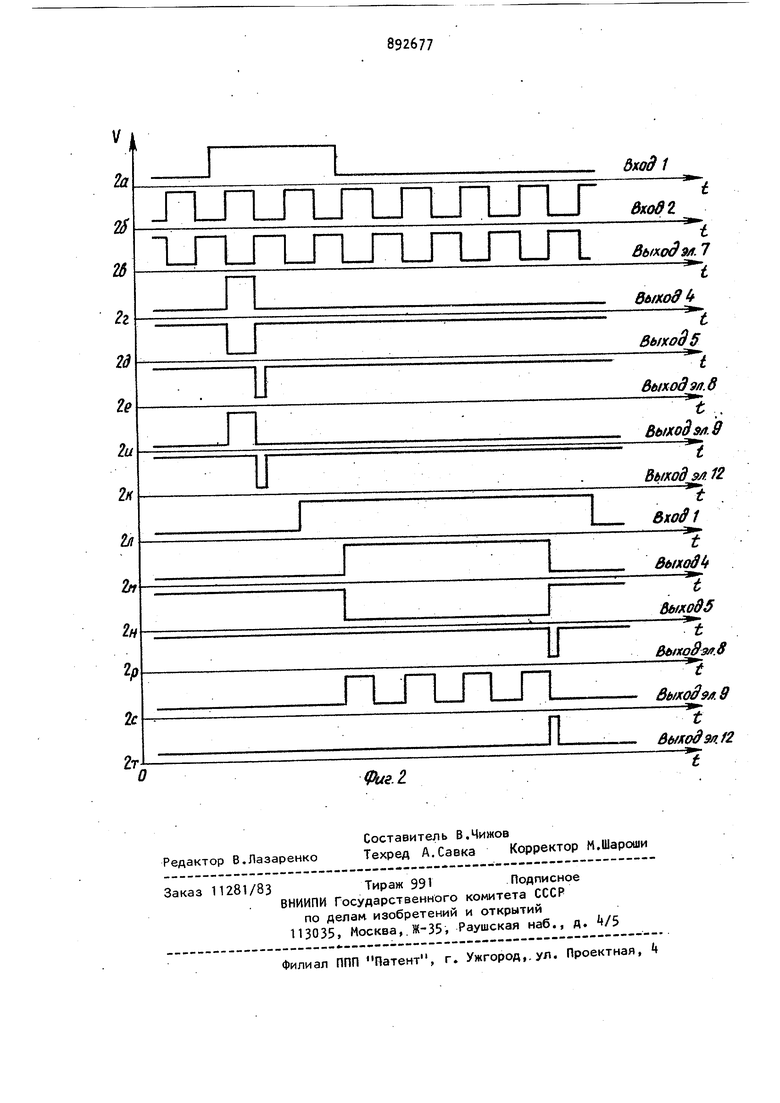

На фиг. 1 приведена структурная схема формирователя, на фиг. 2 - временные диаграммы процесса выработки одиночного импульса под воздействием разрешанмцего сигнала на разных управляющих шинах (указаны с правой стороны графиков).

Формирователь одиночного импульса содержит управляющий 1 и тактовый 2 входы, О-триггер 3 с выходами k и 5, являющиеся выходами формирователя, RS-триггер 6, инвертор 7 элемент И-НЕ 8, элемент И 9, счетчик 10 дешифратор 11, элемент И-ИЛИ 12, управляющие шины 13j Н, 15, 16, 17, ...N.

Вход 1 соединен с информационным входом 0-триггера 3 и с единичным входом RS-триггера 6, единичный выход которого соединен с нулевым входом D-триггера 3, а нулевой вход RS-триггера 6 - с выходом элемента И-ИЕ 8, первый вход которого соединен с выходом инвертора 7, второй вход - с выходом 4, а третий вход - с выходом элемента И-ИЛИ 12. Вход инвертора 7 соединен с управляющим входом D-триггера 3 и с вторым входом элемента И 9 и подключен к входу 2. Первый вхОд элемента И 9 соединен с выходом а выходс входом счетчика 10, нулевой вход которого соединен с выходом 5, а выходы - с входами дешифратора 11, выходы которого соединены с первыми входами групп U элемента И-ИЛИ 12 вторые входы групп U которого соединены с управляющими шинами 13, 1, ...N.

Формирователь работает следующим образом,

В исходном состоянии на входе 1 присутствует низкий логический уровень, D-триггер 3 тактовой частотой по входу 2 установлен в нулевое состояние, при котором на выходе присутствует низкий логический уровень, а на выходе 5 - высокий логический уровень. Низкий логический уровень.на выходе k препятствует прохождению тактовой частоты через элемент И-НЕ 8 и элемент И 9.

На единичном входе RS-триггера 6 присутствует низкий логический уровень, который удерживает его в единичном состоянии. Высокий логический уровень

на выходе 5 удерживает счетчик 10

в нулевом состоянии, которое дешифрируется дешифратором 11. В исходном состоянии на первом входе первой группы и элемента И-ИЛИ 12 присутствует

высокий логический уровень, а на

всех остальных первых входах групп U элемента И-ИЛИ 12 - низкий логический уровень.

Первый случай, когда на управляю-, щей шине 13 присутствует высокий логический уровень, а на остальных управляющих шинах 1A,15,16...N - низкий логический уровень. На выходе элемента И-ИЛИ 12 присутствует высокий логический уровень. После подачи на вход 1 управляющего положительного сигнала (фиг. 2,2а) RS-триггер 6 сохраняет свое состояние, а передний фронт очередного тактового импульса на входе 2 изменит состояние 0-три1 гера 3. На выходе k появится сигнал логической единицы (фиг.2,2г), а на выходе 5 - сигнал логического нуля (фиг.2,2д), который разблокирует счетчик 10. Отрицательный фронт этого же импульса пройдет через элемент и 9 (фиг.2,2и) и зафиксируется счетчиком 10. Отрицательный фронт этого же импульса выработает на выходе элемента И-НЕ 8 отрицательный rlepeпад (фиг.2,2е), Благодаря задержке распространения на счетчике 10, дешифраторе 11 и элементе И-ИЛИ 12 разрешающий потенциал на выходе элемента И-ИЛИ 12 исчезнет позже (фиг.2,2к), чем выработается отрицательный перепад на выходе элемента И-НЕ(фиг.2,2е). Отрицательный перепад на выходе элемента И-НЕ 8 перебросит RS-тригrep 6 в нулевое состояние, который отрицательным импульсом по нулевому входу D-триггера 3 переведет его в и ходное состояние {фиг.2,2г и 2я), и высокий потенциал на выходе 5 заблокирует счеТчик 10. Таким образом на выходе появится положительный импульс -(фиг.2,2г), а на выходе 5 отрицательный импульс (фиг.2,2д), длительность которого равна половине периода следования тактовой частоты. D-триггер 3 не изменит свое состояние до тех пор, пока RS-триггер 6 не вернется в исходное состояние после снятия управляющего сигнала на входе 1. Второй случай, когда, например, на управляющей шине 17 присутствует высокий логический уровень, а на остальных управляющих шинах - низкий логический уровень. В данном случае на выходе элемента И-ИЛИ 12 будет низкий логический уровень (фиг.2,2т) После подачи на вход 1 управляющего положительного сигнала (фиг.2,2л) передний фронт очередного тактового импульса на входе 2 изменит состояние D-триггера 3 (фиг.2,2м и 2н). Счетчик 10 разблокируется и последую щие тактовые импульсы через, элемент и 9 (фиг.2,2с) начнут поступать на счетчик 10. Состояние счетчика 10 дешифрируется дешифратором 11, на выходах которого будет циркулировать логическая единица. При совпадении логической единицы с выхода дешифратора 11 с логической единицей на управляющей шине 17, на выходе элемента И-ИЛИ 12 появится логическая единица (фиг.2,2т), которая разрешит переброс RS-триггера 6 после выработки отрицательного импульса на выходе элемента И-НЕ 8 (фиг.2,2р) D-триггер 3 перейдет в исходное состояние (фиг.2,2м и 2н) и высокий потенциал на выходе 5 заблокирует счетчик 10. Таким образом, на выходе k появится положительный импульс 77 .4 (фиг.2,2м), на выходе 5 отрицательный импульс (фиг.2,2н), длительность ,которого равна V(-f)T где п число импульсов, прошедших в счетчик 10; Т - период следования тактовой частоты по входу 2. Таким образом, введение элементов И, счетчика, дешифратора, элемента И-ИЛИ позволяет получать одиночные импульсы длительностью от Т/2 до (п- 1/2)Т с дискретностью Т тактовой частоты путем подачи разрешающего сигнала на шины управления, что позволит повысить коэффициент унификации изделия за счет примеиения одной и той же схемы. Форнула изобретения Формирователь одиночного импульса по авт.св. № 595852, отличающийся тем, что, с целью расширения функциональных возможностей, в него дополнительно введены элемент И, счетчик, дешифратор, элемент И-ИЛИ, причем первый вход элемента И. соединен с прямым выходом D-триггера, второй вход - с источником тактовых импульсов, а выход с входом счетчика, нулевой вход которого соединен с инверсным выходом D-триггера, входы дешифратора соединены с выходами счетчика, а выходы дешифратора соединены с первыми входами групп И элемента VI-ИЛИ, вторые входы которых соединены с управляющими шинами, а выход элемента И-ИЛИ соединен с третьим входом элемента И-НЕ. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СбСР № 595852, кл, Н 03 К 3/78, 19.07.76.

Фиг1

Авторы

Даты

1981-12-23—Публикация

1980-04-19—Подача