(54) ДЕЛИТЕЛЬ ЧАСТОТЫ ИМПУЛЬСОВ С УПРАВЛЯЕМЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ШКАЛЫ ВРЕМЕНИ | 1995 |

|

RU2082216C1 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1432451A2 |

| Цифровой стробоскользиметр и вычитающее устройство с цифровой индикацией | 1983 |

|

SU1257523A1 |

| МНОГОРАЗРЯДНЫЙ УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1996 |

|

RU2119248C1 |

| Управляемый делитель частоты | 1978 |

|

SU769746A2 |

| Устройство автоматической подстройки линейного закона частотной модуляции | 1984 |

|

SU1218463A1 |

| Устройство для формирования частотно-манипулированных сигналов | 1983 |

|

SU1172058A1 |

| Устройство для измерения параметров дыхания | 1990 |

|

SU1803037A1 |

| Цифровой измеритель температуры | 1982 |

|

SU1111038A1 |

| Устройство для управления многоканальным электроприводом тренажера | 1984 |

|

SU1180846A1 |

.1

Изобретение относится к импульсной технике и может быть использовано в цифровых синтезаторах частот.

Известен делитель частоты импульсов с управляемым коэффициентом деления, который содержит формирователь, п -разрядный реверсивный счетчик, на вход которогю подается сигнал, частота которого подлежит делению, вентили, считывающие (п. -1) число, соответствующее весу OCO-,Q бого кода, и вентили, сч1ггыва1ощие чиспо меньшее на единицу числа (п. -1). На вентили подается сигнал, частота которого подлежит делению,и кодовый сигнал, выражающий коэффициент деления JYJ . 15

Однако известная схема позволяет получить коэффициенты деления, которые регулируются лишь кодовым сигналрм, и не пбзвопяет производить дополнительную коррекцию коэффициентов деления с целью 20 расширения их пределов - изменения.

Наиболее близким техническим рёшёни ем к предлагаемому является делитель . Чозтоты импульсов, который содержит

формирователь, инвертор, триггеры, двоичные счетчики, погйчёскйе элементы, многоразрядньте блоки коррекции, блоки управления. Этот делитель реализует предварительное деление отнгбихения К или (К +1) и деление регулируемого отношения а с ю. , последовательностями из (К-1Лс) импульсов с ( п - П-, ) после дбвательностями из К„ импульсов 2.

- . -- . - - - - -- .---..,- .. - .

,i

. Недостатком известного делителя является ограниченный диапазон изменения дробных коэффициентов деления, так как постоянный; коэффициент регулируемого коэффициента отношения значительно меньше постоянного коэффициента пред- варитбльного коЙ1Фициента отношения. Кра, ме того, дробная часть коэффициента деления отображается в виде дроби с постоянным знаменателем, что также не ограничивает пределы изменения коэффициента деления. . .

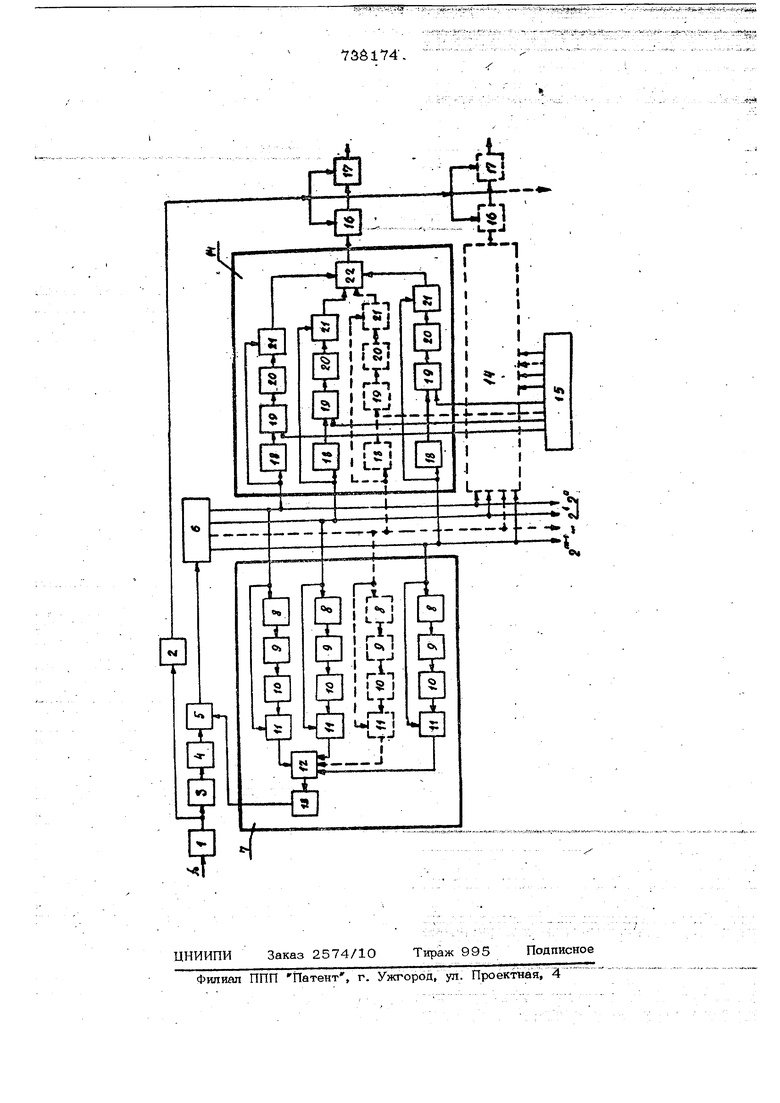

,s. Цель изобретения - расширение диапазона изменения коэффициентов деления. 37 Поставленная цепь достигается тем, что в делитель частоты импульсов с управляемым коэффициентом деления, содержащий входной формирователь иМпульсов, вход которого соединен со входной шиной, а выход которого подключен ко входам инвертора и входу первого двоичйого счетчика, выход которого через второй формирователь импул ьсов и логически элемещ- 2И-НЕ соединен со входом второго счетчика импульсов, выходы разрядов которого соединены с соответствующими входами многоразрядных блоков коррекции, входы управления которыми подключены К выходам блока управления коэффициентом деления, а выход каждого блока коррекции подключен к одному входу триггера, выход которого соединен со входом выходного логического элемента 2И-НЕ, введен многоканальный блок обратной связи, входы которого соединены соответственно с, выходами разрядов второго счетчикаимпульсоь, а вход которого подключен ко второму входу логического элемента 2И-НЕ, причем выход инверторов соединен со вторыми входами триггеров и выходных логических элементов 2И-НВ. Многоразрядный блок коррекции содержит многовходовой логический элемент И-НЕ, входы которого соединены с выходами разрядов, в каждом из которых последовательно включены логические элементы И-НЕ, 2И-НЕ, И-НЕ, и 2И-НЕ второй вход которотго соединен ср входом данного разряда, а втор,)е входы первого логического элемента 2И-НЕ подключены ко входам управления многоразрядного блока коррекции. Многоканальный блок обратной связи содержит многовходовой логический элемент И-НЕ, выход которого соединен со входом выходного логического элемента И-НЕ, а входы подключены к выходам каналов, каждый из которых состоит из трех последовательно включенйзтх логических элемеЬтов И-НЕ и логического элемента 2И-НЕ, второй вход которого соединен со входом данного канала блока обратной связи. На чертеже, представлена блок-схема дёлителя частоты импульсбв. Делитель содержит входной формирователь 1 импульсов отрицательной поляр ности и малой длительности, вход которо го соединен со входной щиной, а выход которого подключен ко входам инвертора 2 и входу первого двоичного счетчика 3 74 выход которого через второй формирователь 4 импульсов и логический элемент 5 2И-НЕ соединен со входом второго счетчика 6 импульсов, выходы разрядов которого 2, 2 ...5f соединены с соответствующими входами многоканального блока 7 обратной, связи, выход которого подключен ко второму входу логического элемента 5, многоканальный блок 7 содержит идентичные звенья, состоящие из логических элементов 8,9,10 и 11, при.чем логические элементы 8,9,10 И-НЕ последовательно включены между собой. Логический элемент 1О соединен своим выходом с одним из входов логического элемента 11 2И-НЕ, вход логического элемента 8 соединен с другим входом логического Элемента 11, а его выход соединен с одним из входов многовходового логического элемента 12 И-НЕ, выход которого соединен с входом выходного логического элемента 13 И-НЕ, К шинам 2°, 2, ..,2 счетчика 6 подключены первые входы многоразрядных блоков 14 коррекции, вторые входы управления которых подключены к выходам блока 15 управления коэффициентом деления. Выход каждого блока 14 подключен к одному из входов соответствующего триггера 16, другой вход которого, соединенный с первым входом выходного логического элемента 17 2И-НЕ, подключен к выходу инвертора 2, а выход - ко второму входу логического элемента 17, выход которого является выходом устройства.. Каждый многоразрядный блок 14 коррекции содержит идентичные звенья, состоящие из логических элементов 18, 19, 20 и 21, подключаемые к соответствующим разрядам счетчика 6, причем первым входом каждого звена является вход лЬгическрго элемента 18 И-НЕ, соединенный с -одним из входов логического элемента 21 2И-НЕ, а выход логического элемента 18 .соединен с одним из входов логического элемента 19 2И-НЕ, второй вход которого соединен с блоком 15 управления, выход логического элемента 19 . логический элемент 20 И-НЕ соединен со вторым входом логического элемента 21, выход которого в каждом звене по клйчен к одному из входов многовходового логического элемента 22 И-НЕ, ы,1ход которого является выходом блока 14. Делитель частоты импульсов работает от входного сигнала с частотой f из которого формирователь 1 формирует имnyntcbi, которыми запускается двоичный счетчик 3, осуществляющий деление частоты в п, раз; при этом на выходе второго формирователя 4 получаем отрицате ные импульсы малой длительности, когорые подаются на один Из ёхбдов логического элемента 5. Логический элемент 5 может пропускать и инвертировать импульсную последовательность, снятую с формирователя 4, если на другом его вхо де будет потенциал 1, либо обеспечивать суммирование и инвертирование двух импульсных последовательностей, если на оба его входа будут поданы отрицательные импульсы малой длительнсхзти. Предположим, Что со стороньт многоканального блока 7 к логическому элементу 5 приложен потенциал i, тогда на выходе второго счетчика 6 (шина 2) получим импульсную последовательность с частотой повторения. -где rij - коэффициент деления счетчика Задается условие О - заданный номинал частоты в шине 2°. Пользуясь (1) и (2), определяем необходимый номинал .. (3) Из (3) очевидна однозначная зависимость fp при заданном значении СИ . Частоту повторения импульсов в шинах счетчика 6 записываем следующей зависимостью- -2, где Q,,.,..((4} Сигналы с выхода счетчика 6 преобразуются логическими элементами 8, 9, 10 и-11 в отрицательные импульсы малой длительности. Иьгпульсы с каждого и логических элементов 11 подаются на соответствующие входы многовходового логического элемента 12, который осуществляет операцию сложения импульсны последовательностей, поданных на его входы, выходной логический элемент 13 инвертирует этот сигнал. , В результате с выхода логического .элемента 13 (выход многоканального блока 7) снимаются отрицательные имгульсы малой длительности, частота пов,торения которых выражается следующей

, зависимостью

f..- «-2, где i 0,1,2,. (m-1) 1(5) no

ментом 17, соответствовал О. В этом случае логический элемент 17 блокируется и первый импульс, пришедший на него 174 При воздействии сигнала с многоканального блока 7 на логический элемент 5, частота повторения импульсов на его выходеуОгфецелится в виде пtttl f. -а-г I -а-г(6) t Частота -Рр с учетом (5) и (6) определ1ятся равенством iV(«-VV) (-7) Из равенства (7) следует, что o можно неоднозначно выбирать для заданного значения. К выходам счетчика 6 подключены первые входы многоразрядньтх блоков 14 (входы логических элементов 18). Логические эпёмейы isr 19Г 20 и 21 формируют отрицательные импульсы малой длительности, причем вторые входы ло гических элементов 19 (вторые входы i многоразрядного) блока 14) управляют ся блоком управления 15, со стороны которого подайэТся команды в виде потенциаЛОВ О или 1. При команде О цепь логических элементов 19, состоящая из 20, и 21 блокируется и сиг нал с логического элемента 18 не пройде - на выход логического элемента 21, чтосоответствует отключению соответствующей шины счетчика 6. При команде I указанная цель деблокируется, и соответствующая шина счетчика 6 подключается к выходу многовходового логического элемента 22, который осуществляет операцию сложения импульсных последовательностей, снятых с логических элементов 21. В общем случае число многоразрядных блоков 14 коррекции в делителе может быть более 1, что позволяет получить от одного до нескольких диапазонов частот, набираемых с помощью блока 15 управления. Формирование сигна:ла в каждом «из диапазонов осуществляется на логическом элементе 17, на один вход которого поступает импульсная последовательность с инвертора 2 с частотой ft) , а управ„дет работой логического элемента 17 по другому ее входу триггер 16. Триггер jg включается так, чтобы каждый импупьс прищедщий на его вход с многоразрядкого блока 14 опрокидывая его в состояние, при котором потенциал плеча триг р соединенного с логическим эле77с инвертора 2 вспед за импульсом с мног разрядного блока 14, не пройдет на выхо логического элемента 17, но опрокинет триггер 16 в противоположное состояние. После этого логический элемент 17 деблокируется I и уже следующий и последующие импульсы инвертора 2 пройдут на его вьтход, т.е. на выход делителя. Логический элемент 17 деблокирован триг гером 16 до пр1й:ода 1ё)редногЬ Шпульoia с многоразрядного блока 14 на вход триггера1б.. Таким образом, каяодый импульс пришедший с многоразрядного блока 14 гасит один из и vfпульс ови выходе логического элемента 17, пришед ших с инвертора 2 что экбивалентно осуществлению опбграции Вычитания двух импульсных последовательнсхзтёй сЧаС- тотами повторения В результате на выходе делителя получим импульсную последовательность, частота повторения которой Определяется следуюн им равенством 1-1i f - а-2, 1,г,...,(т15 f f .I ых о уаг о , Для.реализаши (8) необходимо чтобы триггер 16 опрокидывался в состояние О в паузах между импульсами с частотой повторения -Рр , что достигается регулировкой задержки счетчиков 3 к в, . Дробные переменные коэффициенты де ления; на Выходе делителя определяготс я равенством , .. -,, где i,г... (rtiviv г (9) Делитель частоты импульсов позволяет реализовать одно или несколько независимых множеств Пуор , позволяет получить коэффициенты/деления, отображЭеMbje дробью с изменяемым знаменателем, что позволяет реализовать постоянный по абсолютной величине шаг приращения выходной частоты, при этом делитель позволяет независимо выбирать номинал входной частоты для получения заданного абсолютного шага приращения поделенной частоть, что позволяет широко 1йпопьз вать его в синтезаторах частот. -: . - f формула из обретения 1. Делитель чбстоть импульсов с управляемым коэффициентом деления, содер 74 8 жащий входной формироватепь импупьсов, вход которого соединен со входной шиной, а выход которого подключен ко входам инвертора и входу первого двоично го счетчика, выход которого через второй .формирова тель импульсов и логическиД элемент 2И-НЕ соединен со входом второго счетчика импульсов, выходы разрядов которого соединены с соответствуюшимн входами многоразрядных блоков коррекции, входьг управления которыми подключены к выходам блока управления коэффициентом деления, а выход каждого блока коррекции, подключен к одному входу триггера, выход которого средй Н ен со входом выходного логического элемента 2И-НВ, отличаю.щ и и с я тем, что, с целью расширения диапазона изменения коэффициентов деления, в него введены многоканальный блок обратной связи, входы которого соединены соответственно с выходами разрядов второго счетчика импульсов, а вход которого подключен ко второму вхо ду логического элементй 2И-НЕ, причем выход инвертора соединен со вторыми входами триггеров и выходных логических элементов 2И-НЕ. 2.Делитель по п. 1, о т л и ч а юЩ и и с я тем; что многоразрядный блок коррекции содержит многовходовой логический элемент И-НЕ, входы которого соединеныс выходами разрядов, в каждом из которых последовательно включены логические элементы И-НЕ, 2И-НЕ, И-НЕ, 2И-НЕ, второй вход которого соединен со входом данного разряда, а вторые входы первого логического элемента 2И-НЁ подключень ко входам управпения многоразрядного блока коррекции. 3.Делитель по пп. 1 и 2, отличающийся тем, что многоканальный блок обратной связи содержит многовходовой логический элемент И-НЕ, выход которого соединен со входом выходного логического элемента И-НЕ, а входы подключены к выходам каналов, каждый из которых сЪстоит из трех последовательно вклк)Чвннь1Х логических элементов И-НЕ и логического элемента 2И-НЕ, второй вход которого соединен со входом данного канала блока обратной связи. Источники информации, принятые во внимание при экспертизе 1.Акцептованная заявка Японии № 47-57535, кл. 98(5) С 32, 25.12.72. 2.Патент. Франции fo 2178271. кп. И 03 К 23/02, 14.12.73.

Авторы

Даты

1980-05-30—Публикация

1976-07-20—Подача