(54) ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ СБРОСА

1

Изобретение относится к автоматике и вычислительной технике, в частностик устройствам выцержкй времени, соиер-жаишм счетчики импульсов и логические элементы, требующие установки в определенное состояние при включении напряжения питания.

Известно помехоустойчивое устройство сброса, содержащее источник опорного напряжения и триггер Шмидта Г .

Это устройство формирует импульсы сброса, когда напряжение питания падает йиже опорного и не дает импульс сброса при коротких перерывах напряжения питания.

Известен формирователь импульсов сброса, содержащий резисторы, два источника питания, основной транзистор, интегрирующую , стабилитрон, дополнительный транзистор, инвертирующий транзистор 21 .

Недостатки устройства - отсутствие импульсов сброса или формирование импульсов сброса недостаточной длительности при кратковременных перерь1вах на- . пряжения питaниfl так какТсонденсатор интегрирующей цепи за время выключения напряжения питания не успевает разрядиться; недостаточная крутизна фр.онтов формируемых импульсов сброса, особенно при плавном изменении напряжений питания, что не позволяет применить это устройство для начальной установки большинства логических схем, от-

10 сутствие возможности настройки напряжения срабатывания устройства на уровень минимального рабочего напряжения логических устройство, что может при медленном увеличении напряжения пита15ния привести к отсутствию напряжения сброса в моме.нт, когда напряжение питания логических устройств достигает минимального рабочего значения.

Цель изобретения - повьпиение на20дежности работы формирователя.

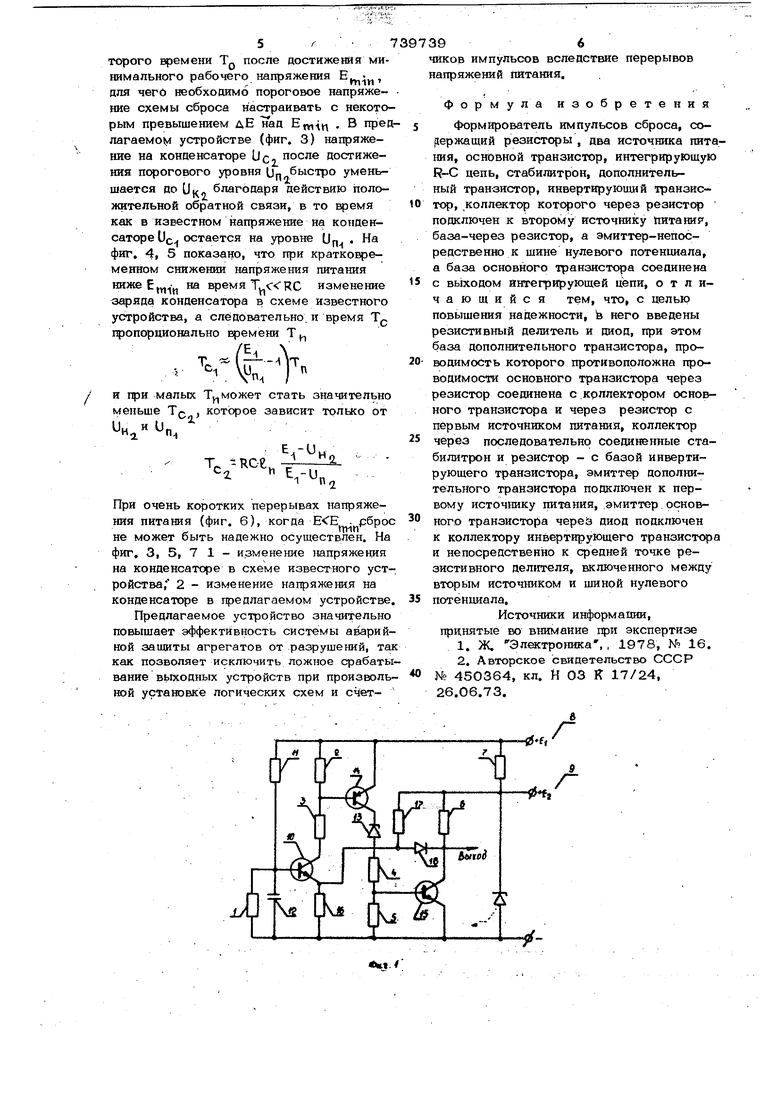

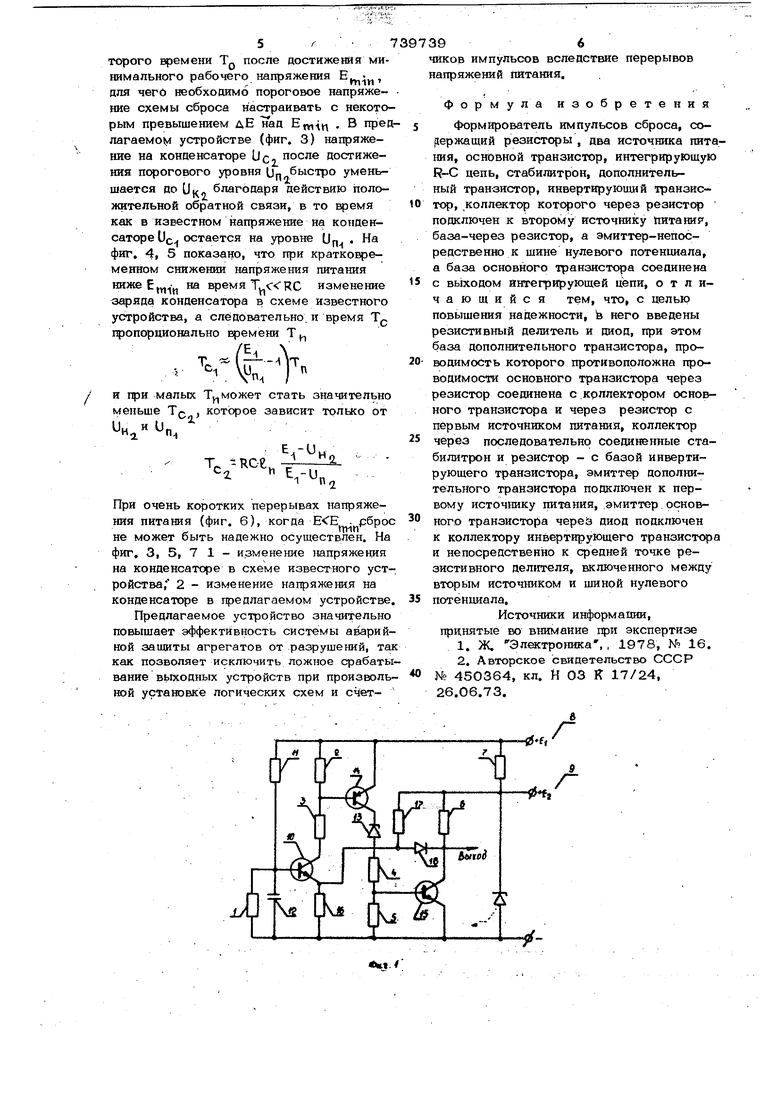

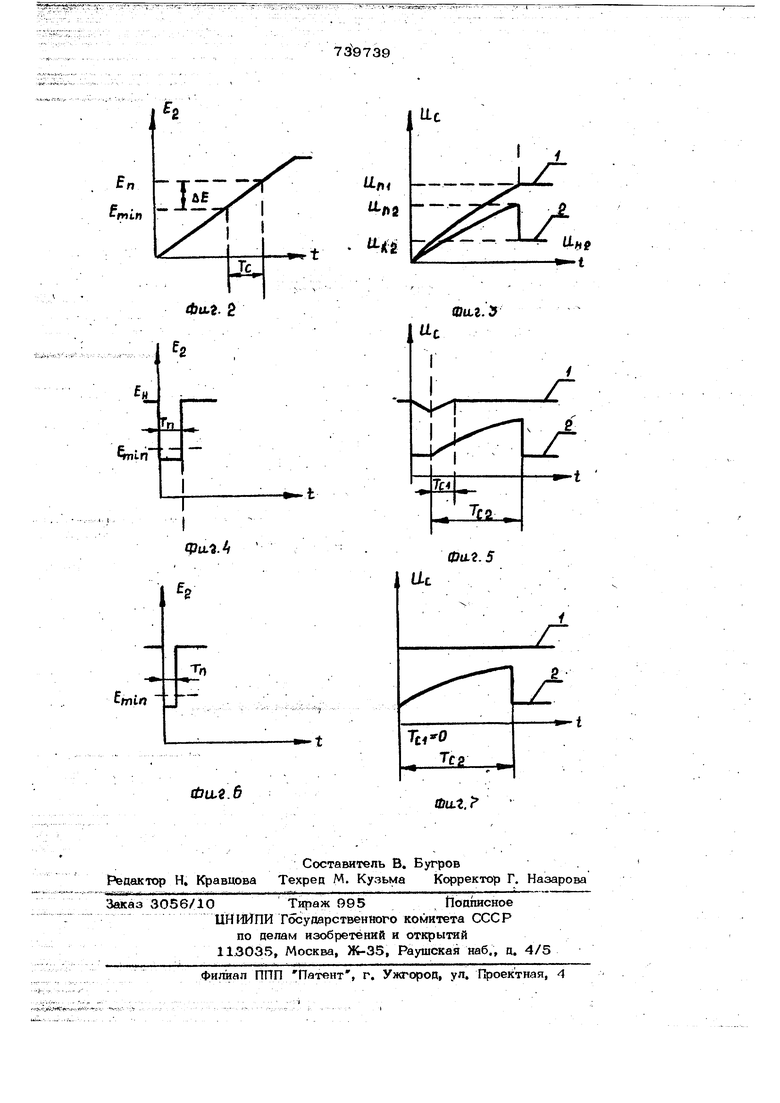

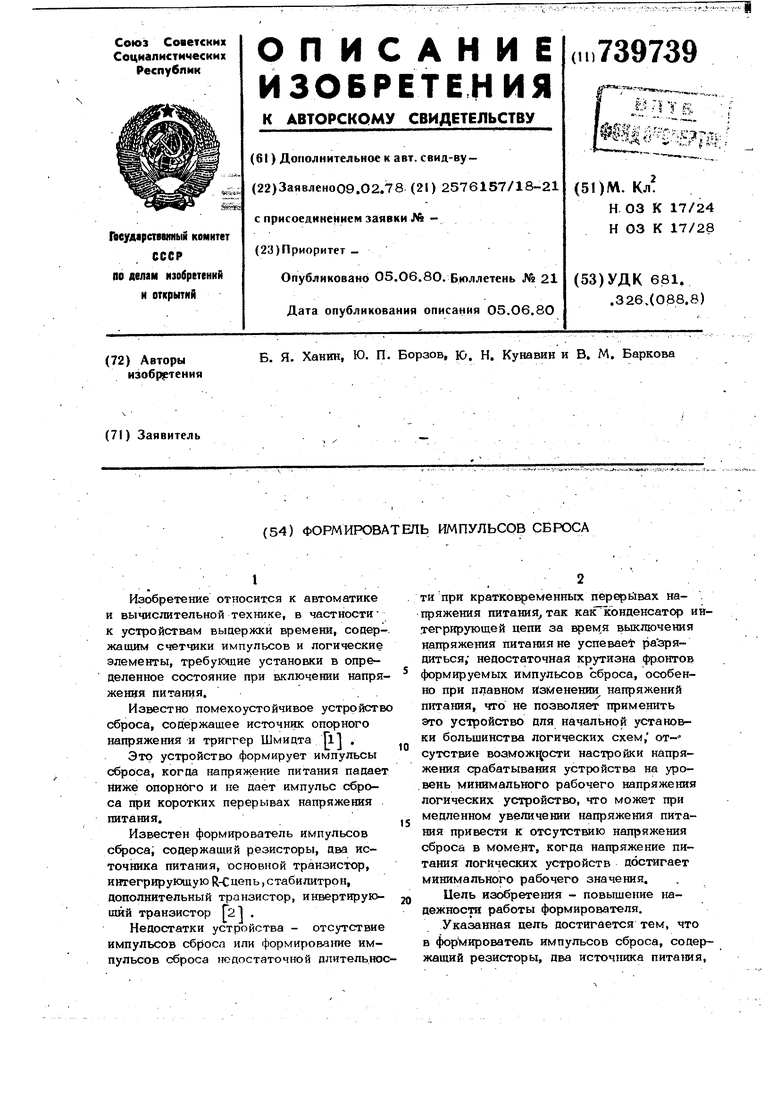

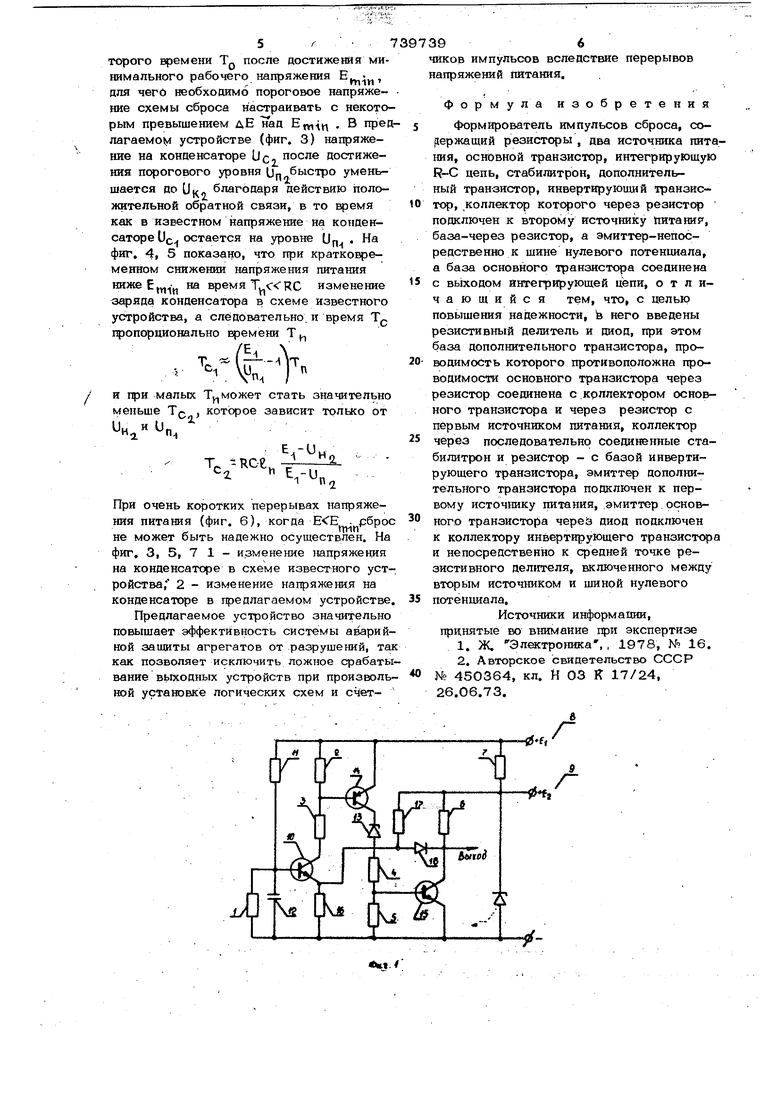

Указанная цель достигается тем, что в формирователь импульсов сброса, содержащий резисторы, два источника питания. cxSHOBHofi TpaH3Hcit)p, интегрирующую К-с. цепь, стабилитрон, дополнительный транзистор, инвертирующий транзистор, коллектор которого через резистор подключен к второму источнику питания, базачерез резистор, эмиттер - непосредственно к шине нулевого потенциала, а база основного транзистора соединена с вькодом интегрирующей цепи, введены резистивный делитель и диод, при этом база дополнительного тpaнзиcтopaj проводимос которого противоположна проводимости ос ШвнЬго транзистора, через резистор соединена с коллектором основного транзистора и через резистор с первым источником питания, коллектор через последовательно соединенные стабилитрон и резистор - с базой инвертирующего транзистора, эмиттер дополнительного транзистора подключен к первому источнику питания, причем эмиттер основного транзистора через диод подключен к коллектору инвертирующего транзистора и непосредственно к средней точке резистивного делителя, включенного между вторым источником и шиной нулевого потенциала. На фиг. 1 представлена функциональная схема устройства, на фиг. 2-7 приведены временные диаграммы, поясняющие работу устройства. Формирователь содержит резисторы 1-7, два источника 8 и 9 питания, основной транзистор 1О, интегрирующуюЯ-С цепь, состоящую из резистора 11 и конденсатора 12,стабилитрон 13, дополнительный транзистор 14, инвертирующий транзистор 15, резистивный делитель, состоящий из резисторов 16 и 17, диод 18, стабилитрон 19. Повышение надежности работы формирователя при скачкообразном изменении напряжений питания достигается за счет формированйя импульса сброса требуемой длительности и формы независимо от времени перерыва напряжения питания (дребезга). Устройство |эаботает следующим образом.: При подаче напряжений источников 8 « 9 питания конденсатор 12 начинает заряжаться от источника 8 питания через резистор 11. При этом транзисторы 10, 14, 15 закрыты и с коллектора транзистора 15 снимается высокий уровень напряжения, осуществляющий установку логических устройств в и;сходное состояние. При напряжении на конденсаторе, превышающем падение напряжения на резисторе 16, от источника 9 питания транзисторы 10, 14, 15 открываются и с коллектора транзистора 15 снимается низкий уровень напряжения, разрешающий работу логических устройств. Время заряда конденсатора цо отпирания транзистора 10 определяет длительность импульса сброса. После отпирания транзистора 15, диод 18 шунтирует резистор 16 и конденсатор 12 разряжается через эмиттерный переход транзистора 10, Диод 18 и транзистор 15. При этом транзисторы 10, 14, 15 остаются открытыми и с выхода устройства снимается низкий уровень напряжения. Благодаря положительной обратной связи с выхода на вход, крутизна фронта импульса сброса на порядок больше в сравнении с известными устройствами. При выключении напряжений питания источников 8 и 9, когда значение напряжений источника 8 питания достигает величины, меньшей напряжения пробоя стабилитрона 13, транзисторы 14 и 15, закрываются .и осуществляется установка логических устройств в исходное состояние. При кратковременных перерывах напряжений питания устройство формирует импульс сброса требуемой длительности, так как конденсатор 12 разряжается после отпирания транзисторов 10, 14 и 15 при первом включении напряжений питания, а кратковременное выключение напряжений питания и их повторное включение не меняет состояния конденсатора. При медленном увеличении напряжений Е, и ЕЛ,напряжение на выходе формирователя равно Е, до тех пор, пока Е не достигнет напряжения срабатывания Е , при KOTopot напряжение между эмиттером и базой основного транзистора меняет знак и благодаря действию положи ельной обратной связи все транзисторы скачком переходят в режим насыщения и на- , пряжение на выходе формирователя падает почти до нуля. С помощью делителя, к которому подключен эмиттеросновного транзистора, м6ждй установцть напряжешк срабатывания формирователя на уровне минимального рабочего напряжения логических схем. При этом диапазон рабочих напряжений логических схем не сужается. На фиг. 2-7 представлены временные диаграммы работы формирователя по сравнению с известным. На фиг. 2 показано, что при медленном увеличении напряжения питания, сигнал начальной установки не должен прекращаться в некоторого времени Т., после достижения минимального рабочего напряжения , для чего необходимо пороговое напряжение схемы сброса настраивать с некоторым превышением дЕ тад , В пред лагаемом устройстве (фиг. 3) напряжение на конденсаторе Ucj после достижения порогового уровня Up быстро уменьшается до UK благодаря действию положительной обратной связи, в то время как в известном напряжение на конденсаторе U остается на уровне Up.. На фиг. 4, 5 показано, что при кратковременном снижении напряжения питания ниже на время T. изменение заряда конденсатора в схеме известного устройства, а следовательно, и время Т,, пропорционально времени Т .. - ( Дт -Лч Г и при малых Ту, может стать значительно меньше Т J которое зависит только от и,,, v. При очень коротких перерывах напряжения питания (фиг. 6), когда - рброс не может быть надежно осуществлен. На фиг. 3, 5, 7 1 - изменение напряжения на конденсаторе в схеме известного устройства; 2 - изменение напряжения на конденсаторе в предлагаемом устройстве Предлагаемое устройство значительно повышает эффективность системы аварий ной защиты агрегатов от разрушений, та как позволяет исключить ложное срабаты вание вьпсодных устройств при произволь ной установке логических схем и счетиков импульсов вследствие перерывов апряжений питания, формула изобретения формирователь импульсов сброса, содержащий резисторы , два источника питания, основной транзистор, интегрирующую R-C цепь, стабилитрон, дополнительный транзистор, инвертирующий транзистор, коллектор которого через резистор подключен к второму источнику йитанир, база-через резистор, а эмиттер-непосредственно к шине нулевого потенциала, а база основного транзистора соединена с выходом интегрирующей цепи, отличающийся тем, что, с целью повышения надежности, b него введены резистивный делитель и диод, при этом база дополнительного транзистора, проводимость которого противоположна проводимости основного транзистора через резистор соединена с коллектором основного транзистора к через резистор с первым источником питанигя, коллектор через последовательно соединенные стабилитрон и резистор - с базой инвертирующего транзистора, эмиттер дополнительного транзистора подключен к первому источнику питания, эмиттер.основного транзистора через диод подключен к коллектору инвертирующего транзистора и непосредственно к средней точке резистивного делителя, включенного между вторым источ1шком и шиной нулевого потенциала. Источники информации, принятые во внимание при экспертизе 1.Ж. Электроника,, 1978, N 16. 2.Авторское свидетельство СССР № 450364, кл. Н 03 К 17/24, 26.06.73.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения частоты следования импульсов | 1974 |

|

SU497723A1 |

| ИМПУЛЬСНЫЙ СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ ПОНИЖАЮЩЕГО ТИПА | 1991 |

|

RU2006062C1 |

| Устройство для импульсно-фазового управления трехфазным тиристорным преобразователем | 1987 |

|

SU1631682A1 |

| Стабилизированный источник питания | 1981 |

|

SU1029167A1 |

| ФОРМИРОВАТЕЛЬ СИГНАЛА ВКЛЮЧЕНИЯ ПОМЕХ | 1993 |

|

RU2122281C1 |

| Формирователь импульсов | 1974 |

|

SU493906A1 |

| УСТРОЙСТВО ДЛЯ ЗАЩИТЫ ОТ ПЕРЕГРУЗКИ ПО ТОКУ | 1999 |

|

RU2179775C2 |

| Импульсный понижающий стабилизатор постоянного напряжения | 1990 |

|

SU1786477A1 |

| Устройство для заряда аккумуляторной батареи транспортного средства | 1986 |

|

SU1427483A1 |

| Генератор линейно-изменяющегося напряжения | 1974 |

|

SU497721A1 |

Авторы

Даты

1980-06-05—Публикация

1978-02-09—Подача