Изобретение относится к вычислительной технике, а именно, к аналого вым вычислительным устройствам и может быть использовано в системах и устройствах автоматики. Другой возможной областью примене ния изобретения является полупроводниковая техника, где оно может быть использовано при производстве аналоговых умножителей на основе гибридных и интегральных микросхем. Известен аналоговый полупроводниковый прибор,представляющий собой пятьдесят пар транзисторов,соединенных между собой в случайной последовательности и функционально являющийся одной парой транзисторов с улучшенными параметрами. Улучшение параметров достигается за счет усред нения параметров отдельных пар транзисторов.Недостатком описанного устройства является большое число пар транзисторов,необходимых для получения эффективного усреднения параметров при случайном законе их соединения 1 . Известен также умножитель,имеющий первую согласованную пару транзисторов, осуществляющую умножение, втору согласованную пару транзисторов, логарифмирующую входной сигнал, третью и четвертую согласованную пару .транзисторов для згщания начального тока в цепи входов, и 1Дифференциальный усилит.ель первого входного сигнала, первый операционный усилитель второго входного сигнала с транзистором на выходе, подключенным -в цепь эмиттеров умножающей пары,, второй операционный усилитель, считывающий выходной сигнал, с умножающей пары, а также ряд согласованных по параметрам резисторов в токозадающих нагрузочных и масштабных цепях 2. Недостатком данного умножителя является сильное влияние степени согласованности транзисторов, как пар ежду собой, так и внутри пары, на точность умножения. Наиболее близким техническим решением является двухквадратное ; множительное устройство, содержащее первую дифференциальную пару транзисторов , эмиттеры которых соединены между собой, база первого транзистора через первый масштабный резистор соединена с первым входом устройства,база второго транзистора через второй маештабный резистор соединена с подвижным контактом задающего потенциометра s выводы которого подключены к источнику опорного напряжения, коллектор первого транзистора соединен через третий масзитабный резистор с шиной нулевого потенциала и непосредственно с инвертирующим входом перBOJO дифференциального усилителя, в депи отрицательной обратной связи которого включен четвертый масштабный резистор, и неинвертирующий подключен к шине нулевого поте циала, а второй вход устройства пятый масштабный резистор соеди||1ен с инвертирующим входом усилитеЬя . Устройство содержит также. втрРУЮ дифференциальную пару транзисторов и третий дифференциальный усилте41ь,в цепи отрицательной обратной св|1зи которого включен шестой масштаный резистор, неинвертирующий вход соединен с шиной нулевого потенциала, инвертирующий вход непосредственно соединен с коллектором второго транзистора первой дифференциальной пары и через седьмой масштабный реристор - с выходом дифференциальноГо усилителя, а выход третьего дифференциального усилителя является; выходом устройства; базы транзис торов ВТОРОЙ дифференциальной пары соединены с третьим входом устройства, эмиттеры подключены к выходу второго дифференциального усилителя, коллектор первого транзистора соединен с эмиттерами транзисторов первой дифференциальной пары, а коллектор второго транЕистора - с инвертирующим входом второго дифференциального усилителя.

Недостатком описанного устройства является невысокая точность умножения, а также дрейф его параметров во времени,

Цель изобретения - увеличение точности умножения и уменьшение временного дрейфа параметров устройства.

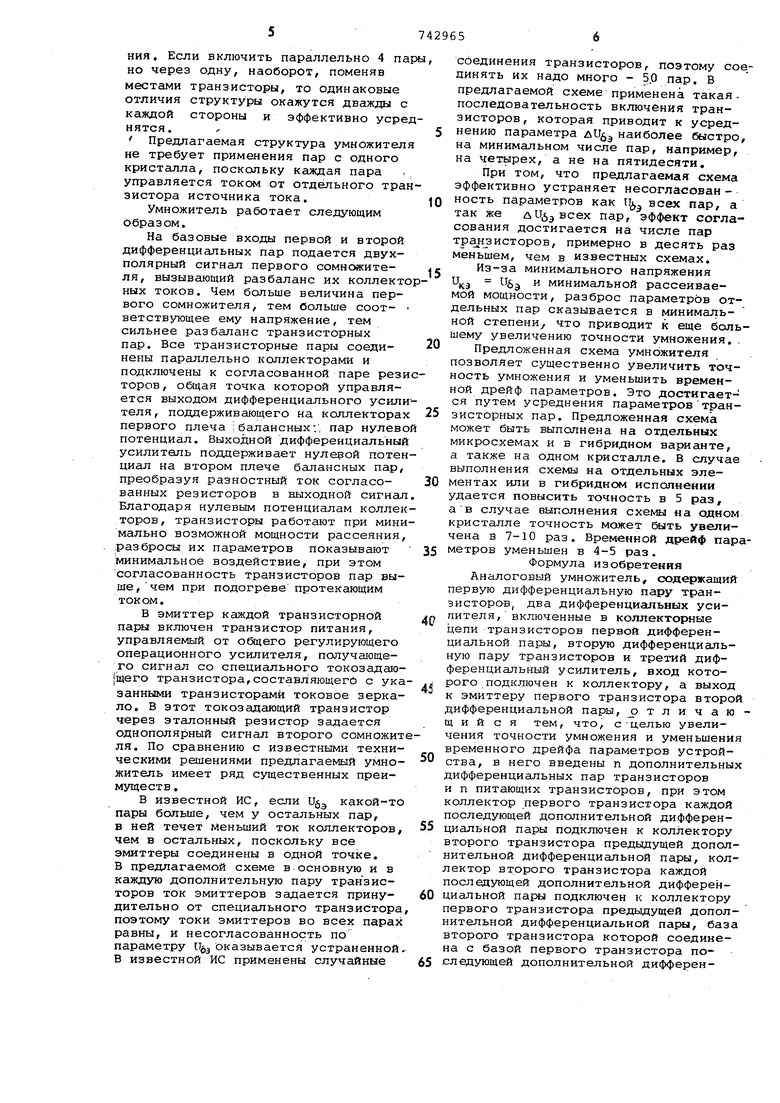

Указанная цель достигается тем1д что в аналоговый умножитель,содержащий первую дифференциальную пару транзисторов, два дифференциальных усилителя включены в коллекторные цег1и транзисторов первой дифференциальной.пары, вторую дифференциальную пару транзисторов и третий дифференциальный усилитель, вход которого подключен к коллектору аэыход к змиттеру первого транзисто ра второй дифференциальной пары, дополнительно введены п дополнительных дифференциальных пар транзисторов (где п 1,2,3.., и определяется требуемой точностью умножения), и п питающих транзисторов, при этом коллектор первого транзистора каждой последующей дополнительной дифференциальной пары подключен к коллектору второго транзистора предыдущей дополнительной дифференциальной пары, коллектор второго транзистора каждой последующей дополнительной дифференциальной пары подключен к коллектору .первого транзистора предыдущей дополнительной дифференциальной пары, баз второго транзистора которой соединен с базой первого транзистора последующей дополнительной дифференциальной пары, базы первых транзисторов нечетных дополнительных дифференциальных пар подключены к базе первого транзистора первой дополнительной дифференциальной пары, а базы первых транзисторов четных дополнительных дифференциальных пар соединены и являются входом устройства, коллекторы питающих транзисторов подключены к эмиттерам транзисторов соответствующих дополнительных дифференциалных пар, эмиттеры объединены и подключены к эмиттерам транзисторов второй дифференциальной пары, а базы объединены и подключены к базам транзисторов второй дифференциальной пары.

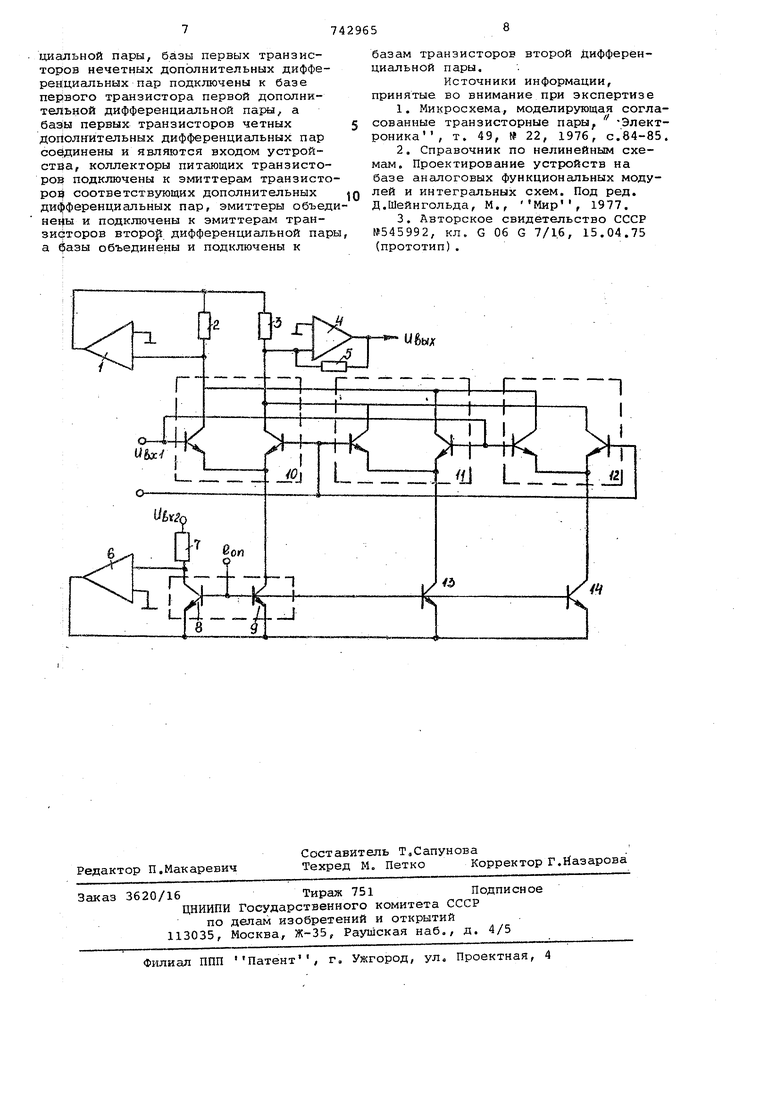

На чертеже дана схема множитель:ного устройства.

Устройство содержит первый дифференциальный усилитель 1, масштабные резисторы 2 и 3, второй дифференциальный усилитель 4, резистор 5 обратной связи, третий дифференциальный усилитель 6, входной резистор 7, вторая дифференциальная пара 8 транзисторов 9, первая дифференциальная пара 10, цепочка п дифференциальных пар транзисторов 11 и 12, п питающих транзисторов 13 и 14.

Дифференциальные пары транзисторов умножителя могут быть взяты с одного или нескольких кристаллов ИС {интегральных схем), а транзисторы для питания дифференциальных пар с одного.кристалла или с нескольких, но согласованных между собой. Порядок включения транзисторов в дифференциальных парах меняется на обратный в каждой последующей паре. Достижение эффективного усреднения параметров пар обеспечивается во много раз меньшим количеством приборов, например, четырьмя, пятью,а не пятьюдесятью, .как описано в аналоге. Этот эффект достижим потому, что интегральные транзисторные пары создаюся благодаря мультиплицированию фотошаблонов по пластине. :Иными словами создается конфигурация областей транзисторов одной пары и они размножаются сдвигом,этого этсшона по двум осям на стандартный шаг. В действительности всегда один транзистор хоть немного, но отличается от второго в паре и также чуть несогласованные пары мультиплицируются „ Если соединять их параллельно по случайному закону, то требуется большое число пар для достижения согласования. Если включить параллельно 4 па но через одну, наоборот, поменяв местами транзисторы, то одинаковые отличия структуры окажутся дважды с каждой стороны и эффективно усре нятся. Предлагаемая структура умножител не требует применения пар с одного кристалла, поскольку каждая пара управляется током от отдельного тра зистора источника тока. Умножитель работает следующим образом. На базовые входы первой и второй дифференциальных пар подается двухполярный сигнал первого сомножителя, вызывающий разбаланс их коллект ных токов. Чем больше величина первого сомножителя, тем больше соответствующее ему напряжение, тем сильнее разбаланс транзисторных пар. Все транзисторные пары соединены параллельно коллекторами и подключены к согласованной паре рези торов, общая точка которой управляется выходом дифференциального усили теля, поддерживающего на коллекторах первого плеча : балансных:, пар нулево потенциал. Выходной дифференциальный усилитель поддерживает нулевой потен циал на втором плече балансных пар, преобразуя разностный ток согласованных резисторов в выходной сигнал Благодаря нулевым потенциалам коллек торов, транзисторы работают при мини мально возможной мощности рассеяния разбросы их параметров показывают минимальное воздействие, при этом согласованность транзисторов пар выше, чем при подогреве протекающим током. В эмиттер каждой транзисторной пары включен транзистор питания, управляемый от общего регулирующего операционного усилителя, получающего сигнал со специального токозадаю|щего транзистора,составляющего с ука занными транзисторами токовое зеркало. В этот токозадающий транзистор через эталонный резистор задается однополярннй сигнал второго сомножит ля. По сравнению с известными техническими решениями предлагаемый умнО житель имеет ряд существенных преимуществ , В известной ИС, если Ug какой-то пары больше, чем у остальных пар, в ней течет меньший ток коллекторов чем в остальных, поскольку все эмиттеры соединены в одной точке. В предлагаемой схеме в основную и в каждую дополнительную пару транзисторов ток эмиттеров задается принудительно от специального транзистора поэтому токи эмиттеров во всех парах равны, и несогласованность по параметру оказывается устраненной В известной ИС применены случайные соединения транзисторов, поэтому соединять их надо много - 5.0 пар. В предлагаемой схеме применена такаяпоследовательность включения транзисторов, которая приводит к усреднению параметра ди знаиболее быстро, на минимальном числе пар, например, на четырех, а не на пятидесяти. При том, что предлагаемая схема эффективно устраняет несогласован ность параметров как П, всех пар/ а так же ди ззвсех пар, эффект согласования достигается на числе пар тра 1зисторов, примерно в десять раз меньшем, чем в известных схемах. Из-за минимального напряжения Uf, и минимальной рассеиваемой мощности, разброс параметров отдельных пар сказывается в минимальной степени, что приводит к еще большему увеличению точности умножения.. Предложенная схема умножителя позволяет существенно увеличить точность умножения и уменьшить временной дрейф параметров. Это достигается путем усреднения параметровтранзисторных пар. Предложенная схема может быть выполнена на отдельных микросхемах и в гибридном варианте, а также на одном кристалле. В случае выполнения схемы на отдельных элементах или в гибридном исполнении удается повысить точность в 5 раз, ав случае выполнения схемы на одном кристалле точность может быть увеличена в 7-10 раз. Временной дрейф параметров уменьшен в 4-5 раз. Формула изобретения Аналоговый умножитель, содержащий первую дифференциальную пару транзисторов, два дифференциальных усилителя, включенные в коллекторные цепи транзисторов первой дифференциальной пары, вторую дифференциальную пару транзисторов и третий дифференциальный усилитель, вход которого подключен к коллектору, а выход к эмиттеру первого транзистора второй дифференциальной пары, Jpтличaю щ и и с я там, что, с-целью увеличения точности умножения и уменьшения временного дрейфа параметров устройства, в него введены п дополнительных дифференциальных пар транзисторов и п питающих транзисторов, при этом коллектор первого транзистора каждой последующей дополнительной дифференциальной пары подключен к коллектору второго транзистора предыдущей дополнительной дифференциальной пары, коллектор второго транзистора каждой последующей дополнительной дифференциальной пары подключен к коллектору первого транзистора предыдущей дополнительной дифференциальной пары, база второго транзистора которой соединена с базой первого транзистора последующей дополнительной дифференциальной пары, базы первых транзисторов нечетных дополнительных дифферейциальных пар подключены к базе первого транзистора первой дополнительной дифференциальной пары, а баэы первых транзисторов четных дополнительных дифференциальных пар соединены и являются входом устройства, коллекторы питающих транзисторов подключены к эмиттерам транзисто poq соответствующих дополнительных дифференциальных пар, эмиттеры объед нейы и подключены к эмиттерам транзи(|торов BTOpo|i дифференциальной па а фазы объединены и подключены к базам транзисторов второй Дифференциальной пары. Источники информации, принятые во внимание при экспертизе 1.Микросхема, моделирующая согласованные транзисторные пары, -Электроника, т. 49, 22, 1976, с.84-85. 2.Справочник по нелинейным схемам. Проектирование устройств на базе аналоговых функциональных модулей и интегральных схем. Под ред. Д.Шейнгольда, М., Мир, 1977. 3.Авторское свидетельство СССР №545992, кл. G 06 G 7/1.6, 15.04.75 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Оптоэлектронный умножитель | 1981 |

|

SU1012287A1 |

| Управляемый масштабный преобразователь | 1990 |

|

SU1753585A1 |

| Четырехквадратный умножитель | 1981 |

|

SU978160A1 |

| Перемножающее устройство | 1983 |

|

SU1168971A1 |

| Преобразователь код-ток | 1987 |

|

SU1499498A1 |

| Электронный коммутатор | 1979 |

|

SU801249A1 |

| Устройство для определения средневзвешенного значения функции | 1976 |

|

SU636626A1 |

| Двухквадрантное множительное устройство | 1975 |

|

SU545992A1 |

| ЛОГАРИФМИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2003 |

|

RU2252452C1 |

| Электронный коммутатор | 1984 |

|

SU1188874A2 |

Авторы

Даты

1980-06-25—Публикация

1978-03-27—Подача