Изобретение относится к аналогевой вычислительной технике, к усилительной технике, а именно к устройствам с переменным коэффициентом передачи, и может быть использовано в аналоговых вычислительных мгипинах и в системах обработки данных.

Известен четырехквадрантный умножитель, содержащий четыре дифференциальных усилительных каскада, два, . генератора тока, два логарифмирующих транзистора, резистор смещения, два резистора нагрузки, балансирующий резистор.

В этом устройстве за счет балансирующего резистора, включенного между коллекторами логарифмирующих транзисторов, достигнуто определенное повышение точности перемножения и динамического диапазона входных сигналов fl.

Однако в данном умножителе недостаточно высокая точность, которая при самой тщательной настройкеимееа значение порядка +0,5%.Кроме того, в этом устройстве недостаточно широкий динамический диапазон перемножаемых входных напряжений.

Наиболее близким по технической сущности к предлагаемому является

четырехквадрантный умножитель, со держащий первый и второй входше усилительные блоки, информационные входы котсчрых являются соо ветственно первым и вторым входами устройва, два дифференциальных источника тока, входы которых подключены ссютветственно к входам питания первого и второго входных усилительных бло10ков, блок умножения, шлход которого( является выходом устройства первый вход блока умножения переключен к выходу первого входного усилительного блока, второй вход - к выходу вто15рого входного усилительного блока, выход питания блока умножения подключен к шине питания, и два логарифмирующих диода С 2 1.

В этом устройстве также недоста20точно высокая точность перемножения в широком динецъшческом диапазоне h входных напряжений, для повышения точности- умножения в нем требуется подбор логарифмирук}14их диоДов. Тре25буется такЛсе, чтобы транзисторы умножения были тщательно согласованы по своим динамическим характеристикам, в связи с этим даже в случае выполнения такогр умножителя а виде

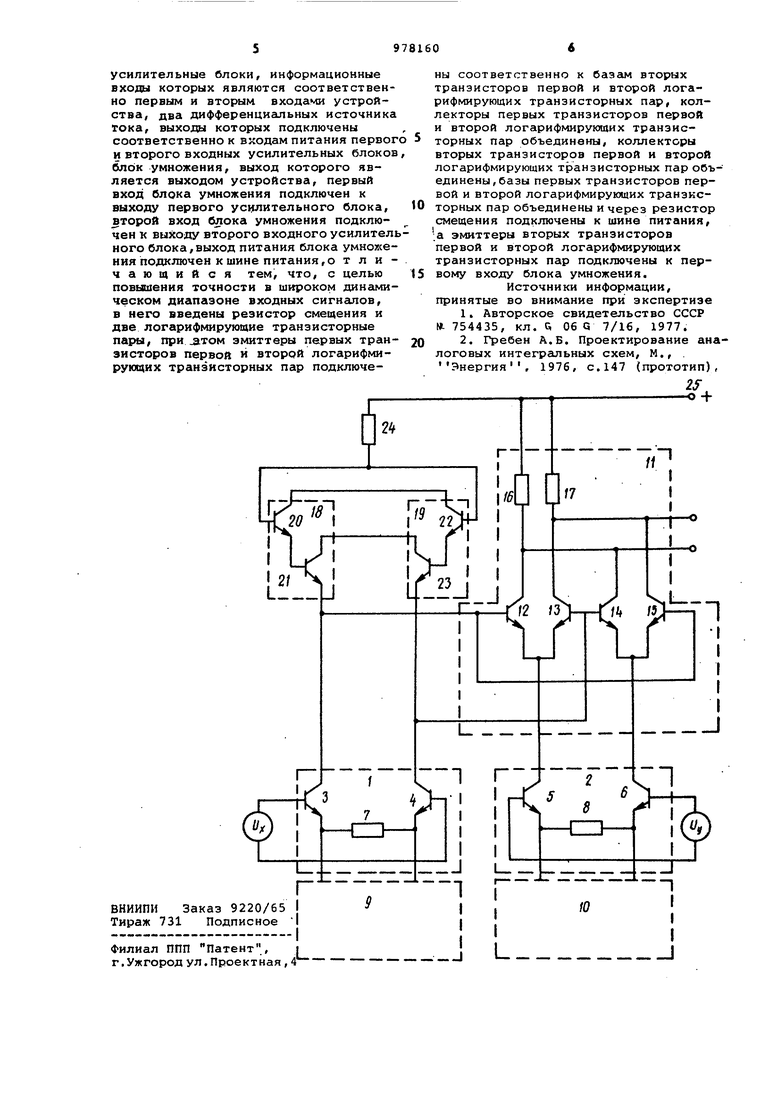

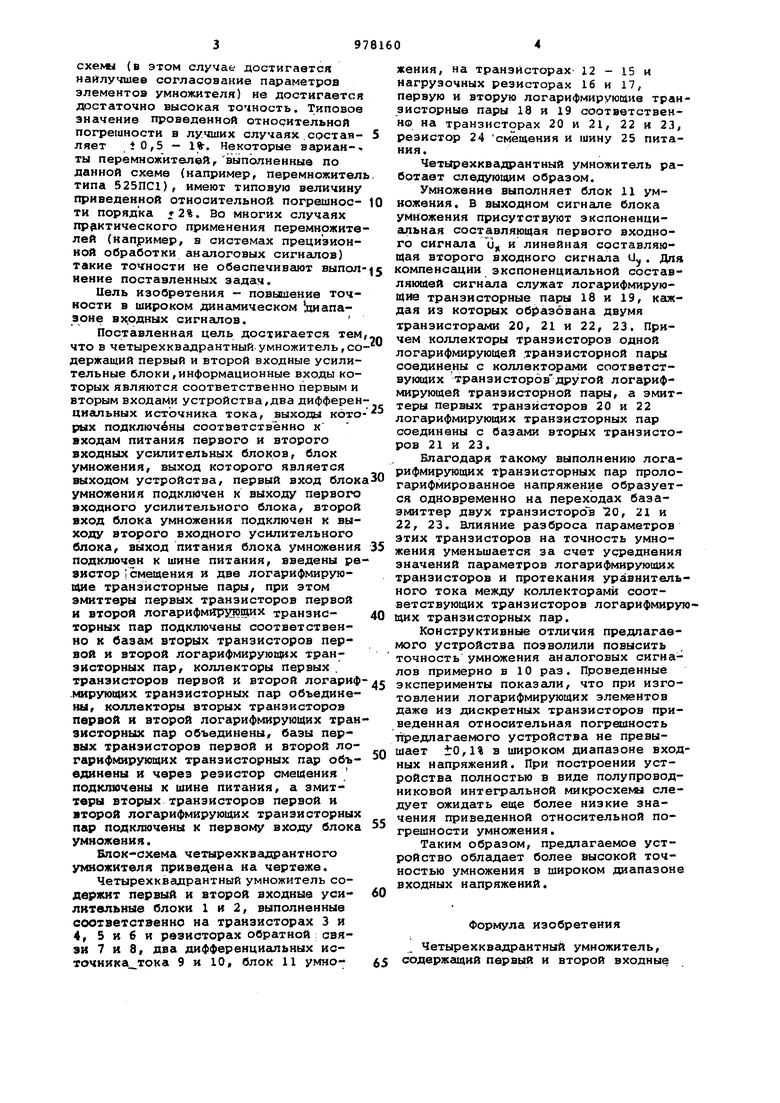

30 интегральной полупроводниковой микоосхемы (в этом случае достигается наилучшее согласование параметров элементов умнозкителя) не достигается достаточно высокая точность. Типовое значение проведенной относительной погрешности в лучших случаях .составляет ,10,5 - 1. Некоторые вариан-. ты перемножителей, выполненные по данной схеме (например, перемножител типа 525ПС1), имеют типовую величину приведенной относительной погрешности порядка 2%. Во многих случаях практического применения перемножите лей (например, в системах прецизионной обработки аналоговых сигналов) такие точности не обеспечивают выпол нение поставленных задач. Цель изобретения - повышение точности в широком динамическом диапазоне вхрдных сигналов. Поставленная цель достигается тем что в четырехквещрантный-умножитель,со держащий первый и второй входные усилительные блоки,информационные входы которых являются соответственно первым и вторым входами устройства,два дифферен циальных источника тока, выходы кото рых подключены соответственно к входам питания первого и второго входных усилительных блоков, блок умножения, выход которого является выходом устройства, первый вход блок умножения подключен к выходу первого входного усилительного блока, второй вход блока умножения подключен к выходу второго входного усилительного блока, выход питания блока умножения подключен к шине питания, введены ре зистор ;смещения и две логарифмирую14ие транзисторные пары, при этом эмиттеры первых транзисторов первой и второй логарифмирую транзисторных пар подключены соответственно к баэам вторых транзисторов первой и второй логарифмирующих транзисторных пар, коллекторы первых . транзисторов первой и второй логариф .мирующих транзисторных пар объединены, коллекторы вторых транзисторов первой и второй логарифмирующих тран зисторных пар объединены, базы первых транзисторов первой и второй логарифмирующих транзисторных пар объединены и через резистор смещения подключены к шине питания, а змиттеры вторых транзисторов первой и второй логарифмирующих транзисторных пар подключены к первому входу блока умножения. Блок-схема четырехквадрантного умможителя приведена на чертеже. Четырехквадрантный умножитель содержит первый и второй входные усилительные блоки 1 и 2, выполненные соответственно на транзисторах 3 и 4, 5 и б и резисторах обратной : связи 7 и 8, два дифференцисшьных источника тока 9 и 10, блок 11 умножения, на транзисторах 12 - 15 и нагрузочных резисторах 16 и 17, первую и вторую логарифмирующие транзисторные пары 18 и 19 соответственно на транзисторах 20 и 21, 22 и 23, резистор 24 смещения и шину 25 питания. Четырехквадрантный умножитель работает следующим образом. Умножение выполняет блок 11 умножения. В выходном сигнале блока умножения присутствуют зкспоненцисшьная составляющая первого входного сигнсша Uy и линейная составляющая второго входного сигнала U. Для компенсации экспоненциальной составляющей сигнала служат логарифмирующие транзисторные пары 18 и 19, кгикдая из которых образована двумя транзисторами 20, 21 и 22, 23. Причем коллекторы транзисторов одной логарифмирующей транзисторной пары соединены с коллекторами соответствующих транзисторов другой логарифмирующей транзисторной пары, а эмиттеры первых транзисторов 20 и 22 логарифмирующих транзисторных пар соединены с базами вторых транзисторов 21 и 23. Благодаря такому выполнению логарифмирующих транзисторных пар прологарифмированное напряжение образуется одновременно на переходах базаэмиттер двух транзисторов 70, 21 и 22, 23. Влияние разброса параметров этих транзисторов на точность умножения уменьшается за счет усреднения значений параметров логарифмирующих транзисторов и протекания уравнительного тока между коллекторами соответствующих транзисторов логарифмирующих транзисторных пар. Конструктивные отличия предлагаемого устройства позволили повысить точность умножения аналоговых сигналов примерно в 10 раз. Проведенные эксперименты показали, что при изготовлении логарифмирующих элементов даже из дискретных транзисторов приведенная относительная погрешность тфедлагаемого устройства не превышает ±0,1% в широком диапазоне входных напряжений. При построении устройства полностью в виде полупроводниковой интегральной микросхемы следует ожидать еще более низкие значения приведенной относительной погрешности умножения. Таким образом, предлагаемое устройство обладает более высокой точностью умножения в широком диапазоне входных напряжений. Формула изобретения Четырехквадрантный умножитель, содержсцдий первый и второй входные

| название | год | авторы | номер документа |

|---|---|---|---|

| Четырехквадрантный умножитель | 1988 |

|

SU1594522A2 |

| Четырехквадрантное множительное устройство | 1980 |

|

SU957225A1 |

| Аналоговый четырехквадрантный умножитель | 1982 |

|

SU1024939A1 |

| Аналоговый умножитель | 1978 |

|

SU742965A1 |

| ПРЕОБРАЗОВАТЕЛЬ МОЩНОСТИ В ЧАСТОТУ | 1992 |

|

RU2057349C1 |

| Четырехквадрантное множительное устройство | 1978 |

|

SU769559A1 |

| Аналоговый четырехквадратный умножитель | 1987 |

|

SU1474685A1 |

| Устройство с регулируемым усилением | 1988 |

|

SU1741257A1 |

| Электронное экспонометрическое устройство для зеркальных фотоаппаратов | 1976 |

|

SU591793A1 |

| Аналоговое логарифмическое вычислительное устройство | 1982 |

|

SU1095198A1 |

Авторы

Даты

1982-11-30—Публикация

1981-06-18—Подача