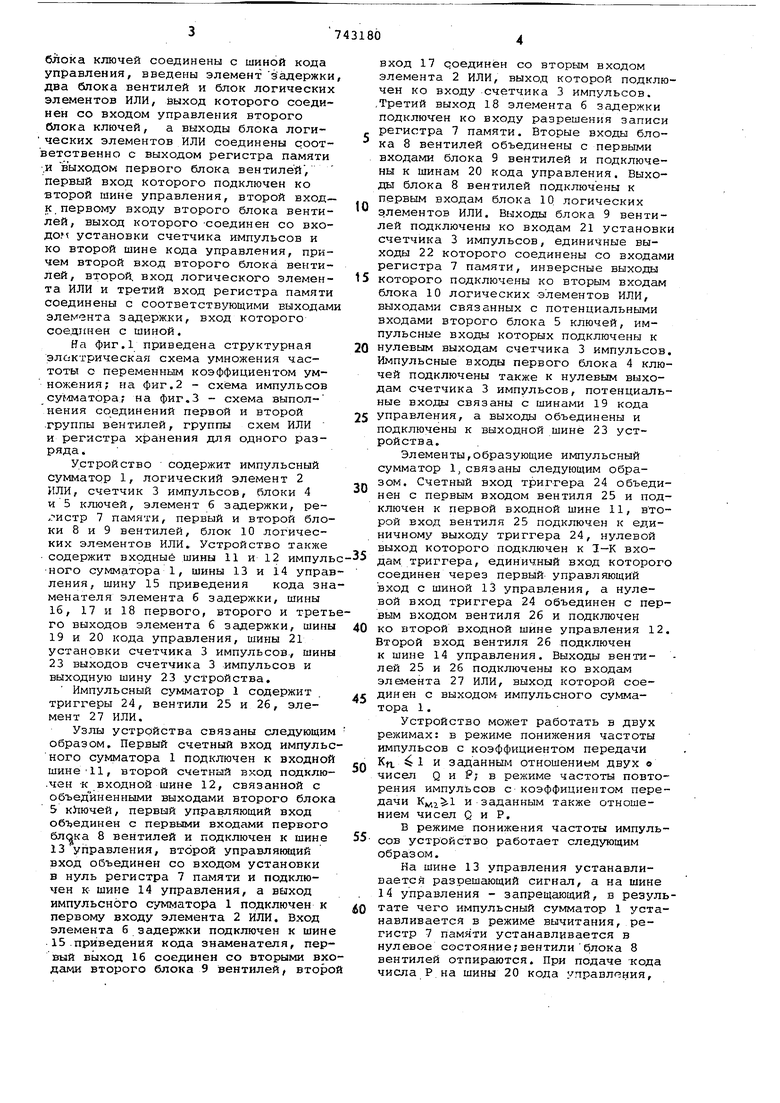

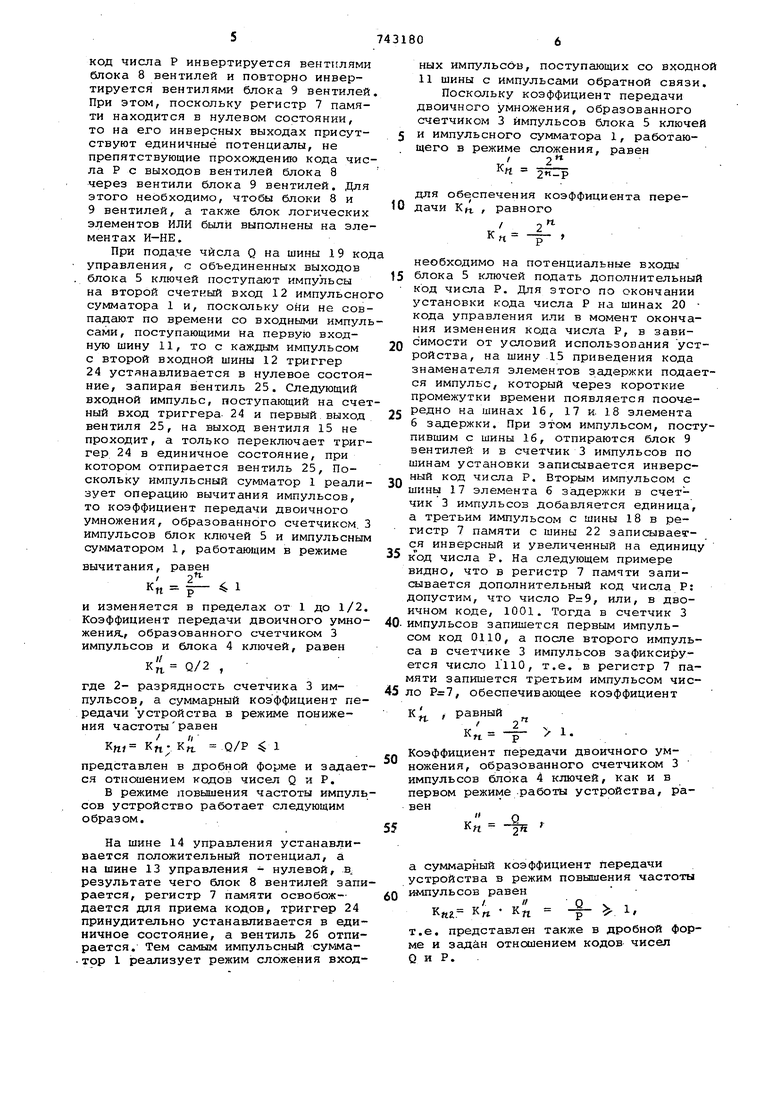

Изобретение относится к области кодирования и преобразования информации и может найти применение при разработке цифровых измерительных устройств и систем управления в качестве цифрового узла преобразования частоты повторения импульсов с пробным коэффициентом передачи. Известны умножители частоты с переменным коэффициентом умножения, содержащие счетчик, цепи установки кода в счетчик, дешифратор и элемент задержки, предназначенное для деления частоты повторения импульсов на коэффициенты,заданные кодом. Недостатком известного устройства является реализация только целочисленных коэффициентов пересчета и ограниченный диапазон их значений 1 Известны также умножитель частоты с переменным коэффициентом умножения содержащий счетчик импульсов, первый вход которого соединен с выходом логического элемента ИЛИ, а выходы соединены соответственно со входами двух блоков ключей и первым входом регистра памяти, второй вход которого соединен с первой шиной управления и первым входом импульсного сумматора. второй вход которого соединен со вто-т рой шиной управления, третий вход с входной шиной, а выход подключен к первому входу логического элемента ИЛИ, причем входы управления первого блока клзочей соединены с шиной кода управления 2 . Недостатком известного умножителя является узкий диапазон изменений коэффициента умножения. Целью настоящего изобретения является расширение диапазона изменения коэффициента умножения. Поставленная цель достигается тем, что в умножитель частоты с переменным коэффициентом умножения, содержащий счетчик импульсов, первый вход которого соединен с выходом логического элемента ИЛИ, а выходы соединены соответственно со входами двух блоков ключей и первым входом регистра памяти, второй вход которого соединен с первой шиной управления и первым входом импульсного сумматора, второй вход которого соединен со второй шиной управления, третий вход с входной шиной, а выход подключен к первому входу логическогоэлемента ИЛИ, причем входы управления первого блока ключей соединены с шиной кода управления, введены элементзадержки два блока вентилей и блок логических элементов ИЛИ, выход которого соединен со входом управления второго блока ключей, а выходы блока логических элементов ИЛИ соединены соответственно с выходом регистра памяти ,и выходом первого блока вентилей, первый вход которого подключен ко второй шине управления, второй вход- к,первому входу второго блока вентилей, выход которого -соединен со входо установки счетчика импульсов и ко второй шине кода управления, причем второй вход второго блока вентилей, второй, вход логического элемента ИЛИ и третий вход регистра памяти соединены с соответствующими выходагэлемента задержки, вход которого соединен с шиной. На фиг.1 приведена структурная электрическая схема умножения частоты с переменным коэффициентом умножения; на фиг.2 - схема импульсов cy 1мaтopa; на фиг.З - схема выполнения соединений первой и второй .группы вентилей, группы схем ИЛИ и регистра хранения для одного разряда. Устройство содержит импульсный сумматор 1/ логический элемент 2 ИЛИ, счетчик 3 импульсов, блоки 4 и 5 ключей, элемент б Зсщержки, ре.гистр 7 памяти, первый и второй блоки 8 и 9 вентилей, блок 10 логических элементов ИЛИ. Устройство также содержит вхрдныё шины 11 и 12 импуль ного сумматора 1, шины 13 и 14 упра ления, шину 15 приведения кода зн менателя элемента б задержки, шины 1б, 17 и 18 первого, второго и треть го выходов элемента б задержки, шины 19 и 20 кода управления, шины 21 установки счетчика 3 импульсов., шины 23 выходов счетчика 3 импульсов и выходную шину 23 устройства. Импульсный сумматор 1 содержит триггеры 24, вентили 25 и 26, элемент 27 ИЛИ. Узлы устройства связаны следующим образом. Первый счетный вход импуль ного сумматора 1 подключен к входной шине11, второй счетный вход подклю .чен -к входной шине 12, связанной с объедйненными выходами второго блок 5 кУгючей, первый управляющий вход обтзединен с первыми входами первого блока 8 вентилей и подключен к шине 13 управления, второй управляющий вход объединен со входом установки в нуль регистра 7 памяти и подключен к шине 14 управления, а выход импульсного сумматора 1 подключен к первому входу элемента 2 ИЛИ. Вход элемента б задержки подключен к шин 15.приведения кода знаменателя, пер вый выход 16 соединен со вторыми вх дами второго блока 9 вентилей, втор вход 17 роединён со вторым входом элемента 2 ИЛИ, выход которой подключен ко входу счетчика 3 импульсов. Третий выход 18 элемента б задержки подключен ко входу разрешения записи регистра 7 памяти. Вторые входы блока 8 вентилей объединены с первыми входами блока 9 вентилей и подключены к шинам 20 кода управления. Выходы блока 8 вентилей подключены к первым входам блока 1Q логических элементов ИЛИ. Выходы блока 9 вентилей подключены ко входам 21 установки счетчика 3 импульсов, единичные выходы 22 которого соединены со входами регистра 7 памяти, инверсные выходы которого подключены ко вторым входам блока 10 логических -элементов ИЛИ, выходами связанных с потенциальными входами второго блока 5 ключей, импульсные входы которых подключены к нулевым выходам счетчика 3 импульсов. Импульсные входы первого блока 4 ключей подключены также к нулевым выходам счетчика 3 импульсов, потенциальные входы связаны с шинами 19 кода управления, а выходы объединены и подключены к выходной шине 23 устройства. Элементы,образующие импульсный сумматор 1, связаны следующим образом. Счетный вход триггера 24 объединен с первым входом вентиля 25 и подключен к первой входной шине 11, второй вход вентиля 25 подключен к единичному выходу триггера 24, нулевой выход которого подключен к I-К входам триггера, единичный вход которого соединен через первый управляющий вход с шиной 13 управления, а нулевой вход триггера 24 объединен с первым входом вентиля 26 и подключен ко второй входной шине управления 12. Второй вход вентиля 26 подключен к шине 14 управления. Выходы венти- лей 25 и 26 подключены ко входам элемента 27 ИЛИ, выход которой соединен с выходом- импульсного сумматора 1. Устройство может работать в двух режимах: в режиме понижения частоты импульсов с коэффициентом передачи Kfi 4 1 и заданным отношением двух в чисел Q и Р; в режиме частоты повторения импульсов с коэффициентом передачи К,,1 и заданным также отношением чисел Q и Р. В режиме понижения частоты импульсов устройство работает следующим образом. На шине 13 управления устанавливается разрешающий сигнал, а на шине 14 управления - запрещающий, в результате чего импульсный сумматор 1 устанавливается в режиме вычитания, регистр 7 памяти устанавливается в нулевое состояние;вентилиблока 8 вентилей отпираются. При подаче -кода числа Р на шины 20 кода управления. код числа Р инвертируется вентилями блока 8 вентилей и повторно инвертируется вентилями блока 9 вентилей При этом, поскольку регистр 7 памяти находится в нулевом состоянии, то на его инверсных выходах присутствуют единичные потенциалы, не препятствующие прохождению кода чис ла Р с выходов вентилей блока 8 через вентили блока 9 вентилей. ,Цля этого необходимо, чтобы блоки 8 и 9 вентилей, а также блок логических элементов ИЛИ были выполнены на эле ментах И-НЕ. При пода.че числа Q на шины 19 ко управления, с объединенных выходов блока 5 ключей поступают импульсы на второй счетный вход 12 импульсно сумматора 1 и, поскольку они не сов падают по времени со входными импул сами, поступающими на первую входную шину 11, то с каждым импульсом с второй входной шины 12 триггер 24 устанавливается в нулевое состояние, запирая вентиль 25. Следующий входной импульс, поступающий на сче ный вход триггера 24 и первый выход вентиля 25, на выход вентиля 15 не проходит, а только переключает триг гер 24 в единичное состояние, при котором отпирается вентиль 25, Поскольку импульсный сумматор 1 реали зует операцию вычитания импульсов, то коэффициент передачи двоичного умножения, образованного счетчиком. импульсов блок ключей 5 и импульсным сумматором 1, работающим в режиме вычитания, равен K« F и изменяется в пределах от 1 до 1/2 Коэффициент передачи двоичного умножения., образованного счетчиком 3 импульсов и блока 4 ключей, равен Кп Q/2 , где 2- разрядность счетчика 3 импульсов, а суммарный коэффициент передачи устройства в режиме понижения частотыравен Кш Кп- . Q/P 41 представлен в дробной форме и задает ся отношением кодов чисел Q и Р. В режиме повышения частоты импуль сов устройство работает следующим образом.

На шине 14 управления устанавливается положительный потенциал, а на шине 13 управления - нулевой, в, результате чего блок 8 вентилей запирается, регистр 7 памяти освобож-дается для приема кодов, триггер 24 принудительно устанавливается в единичное состояние, а вентиль 26 отпирается. Тем самым импульсный сумма.тор 1 реализует режим сложения входа суммарный коэффициент передачи устройства в режим повышения частоты импульсов равен

/. Q -1 Kftx. К« Кп -р- 1

т.е. представлен также в дробной форме и задан отнетиением кодов чисел Q и Р. ных импульсо-в, поступающих со входной 11 шины с импульсами обратной связи. Поскольку коэффициент передачи двоичного умножения, образованного счетчиком 3 импульсов блока 5 ключей и импульсного сумматора 1, работающего в режиме сложения, равен 2 для обе спечения коэффициента передачи Kf , равного необходимо на потенциальные входы блока 5 ключей подать дополнительный код числа Р. Для этого по окончании установки кода числа Р на шинах 20 кода управления или в момент окончания изменения кода числа Р, в зависимости от условий использования устройства, на шину 15 приведения кода знаменателя элементов задержки подается импульс, который через короткие промежутки времени появляется поочередно на шинах 16, 17 и. 18 элемента 6 задержки. При этом импульсом, поступившим с шины 16, отпираются блок 9 вентилей и в счетчик 3 импульсов по шинам установки записывается инверсный код числа Р. Вторым импульсом с шины 17 элемента 6 задержки в счетчик 3 импульсов добавляется единица, а третьим импульсом с шины 18 в регистр 7 памяти с шины 22 записывается инверсный и увеличенный на единицу числа Р. На следующем примере видно, что в регистр 7 памчти записывается дополнительный код числа Р; допустим, что число , или, в двоичном коде, 1001. Тогда в счетчик 3 импульсов запишется первым импульсом код ОНО, а после второго импульса в счетчике 3 импульсов зафиксируется число 1110, т.е. в регистр 7 паяти запишется третьим импульсом чисо , обеспечивающее коэффициент равный / К« Коэффициент передачи двоичного умножения, образованного счетчиком 3 импульсов блока 4 ключей, как и в первом режиме работы устройства, равен О Кп Поскольку вторые входы блока 1 и логических элементов ИЛИ подключены к инверсным выходам регистра 7 па,мяти, то после инвертирования элемен тов И-НЕ образующими элементов 10 ИЛИ код на потенциальных входах блок 5 ключей равен коду, записанному в регистр 7 памяти с шины 22 счетчика 3 импульсов. Предлагаемое устройство обеспечи вает коэффициенты передачи, предста ленные в дробной форме отнопением кодов двух чисел и изменяющиеся в широких пределах. .изобретения Умно5китель частоты с переменным коэффициентом умножения, содержащий счетчик импульсов, первый вход кото рого соединен с выходом логического элемента ИЛИ, а выходы соединены соответственно со входами двух блоков к.лючей и первым входом регистра По1мяти, второй вход которого соединен с первой шиной управления и пер входом импульсного сумматора, второ вход которого соединен со второй шиной управления, третий вход - с входной шиной, а выход подключен к первому входу логического элемента . ИЛИ, причем входы управления первого блока ключей соединены с шиной кода управления, отличающийся тем, что, с целью расширения диапазона изменений коэффициента умножения, в него введены элемент задержки, два блока вентилей и блок логических элементов ИЛИ, выход которого соединен со входом управления второго блока ключей, а выходы блока логических элементов ИЛИ соединены соответственно с выходом регистра памяти и выходом первого блока вентилей, первый вход которого подключен ко второй шине управления, второй вход к первому входу второго блока вентилей, выход которого соединен со входом установки счетчика импульсов и ко второй шине кода управления, причем второй вход второго блока вентилей, второй вход логического элемента ИЛИ и третий вход регистра памяти соединены с соответствующими выходами элемента задержки, вход которого соединен с шиной. Источники информации, принятые во внимание при экспертизе 1.Заявка Японии №50-29306, кл. 98/5/С 31, 31.10.75. 2.Патент США №3753125,кл.307-225. 14.08.73.

Нф.

It

2

ЛЩ

17

16

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты следования импульсов | 1981 |

|

SU1037420A1 |

| Цифровой многофазный преобразователь мощности в частоту | 1989 |

|

SU1707557A1 |

| Устройство для измерения частоты повторения импульсов | 1977 |

|

SU660266A1 |

| Цифровой кодирующий преобразователь частоты следования импульсов | 1980 |

|

SU919080A1 |

| Цифровой умножитель частоты следования импульсов | 1982 |

|

SU1034146A1 |

| Цифровой частотомер | 1975 |

|

SU530263A1 |

| Устройство для измерения параметров частотных датчиков | 1989 |

|

SU1705757A1 |

| Самонастраивающееся устройство управления | 1983 |

|

SU1130830A1 |

| Умножитель частоты | 1980 |

|

SU928610A1 |

| Устройство для коррекции характеристик датчиков | 1978 |

|

SU781850A1 |

1ъ Ф-III

Авторы

Даты

1980-06-25—Публикация

1977-07-01—Подача