1707557

д

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой измеритель электрической энергии многофазной сети | 1988 |

|

SU1647443A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| Устройство для измерения электрической энергии | 1988 |

|

SU1596264A2 |

| Устройство для измерения показателей качества электроэнергии трехфазной сети | 1982 |

|

SU1064233A1 |

| Генератор сигналов сложной формы | 1985 |

|

SU1280597A1 |

| Спектральный анализатор случайных сигналов | 1984 |

|

SU1269048A1 |

| Генератор случайного процесса | 1982 |

|

SU1037249A1 |

| Устройство для отображения графической информации на газоразрядной индикаторной панели | 1982 |

|

SU1108488A1 |

| Устройство сбора данных для цифрового анализатора сигналов | 1990 |

|

SU1751683A1 |

| Цифровое устройство для управления вентильным преобразователем | 1981 |

|

SU1080243A1 |

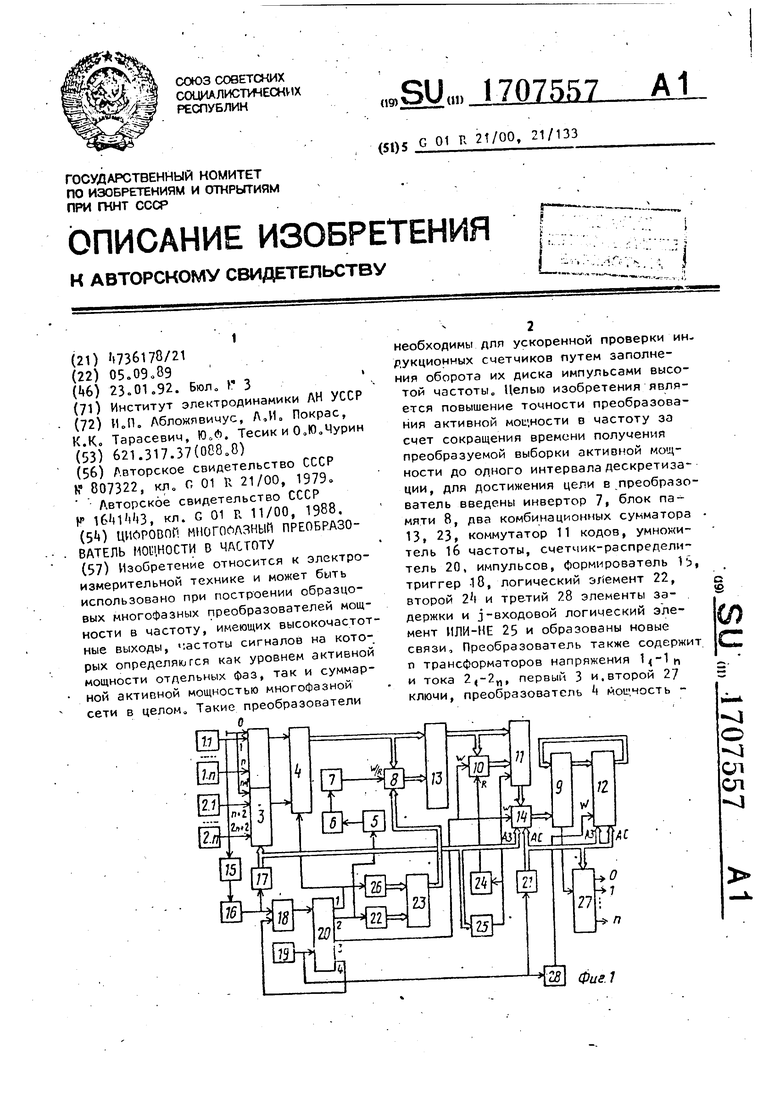

Изобретение относится к электроизмерительной технике и может быть использовано при построении образцовых многофазных преобразователей мощности в частоту, имеющих высокочастотные выходы, частоты сигналов на которых определяются как уровнем активной мощности отдельных фаз, так и суммарной активной мощностью многофазной сети в целом. Такие преобразователи О необходимы для ускоренной проверки индукционных счетчиков путем заполнения оборота их диска импульсами высотой частоты. Целью изобретения является повышение точности преобразования активной мощности в частоту за счет сокращения времени получения преобразуемой выборки активной мощности до одного интерваладескретиза- ции, для достижения цели в .преобразователь введены инвертор 7, блок памяти 8, два комбинационных сумматора 13, 23, коммутатор 11 кодов, умножитель 16 частоты, счетчик-распределитель 20, импульсов, формирователь V3, триггер -18, логический элемент 22, второй 2 t и третий 28 элементы задержки и j-входовой логический элемент ИЛИ-НЕ 25 и образованы новые связи, Преобразователь также содержит п трансформаторов напряжения и тока , первый 3 и.второй 27 ключи, преобразователь k мощность с S -J О СЛ ел ФигЛ

код, дифференцирующую цепь 5, элемент задержки 6, комбинационный сумматор Ь, накапливающий сумматор 10, многоЯ

-. 15

20

1

I

Изобретение относится- к электроизмерительной технике и может быть использовано при построении образце- . вых многофазных преобразователей мощности в частоту, имеющих высокочастотные выходы, частоты сигналов на которых определяются как уровнем ак тивной мощности отдельных фаз, так и суммарной активности мощностью многофазной сети в целому и для ускорения поверки индукционных счетчиков путем

заполнения оборота их диска импульсами высокой частоты.

Целью изобретения является повышение точности преобразования активной мощности в частоту, 25

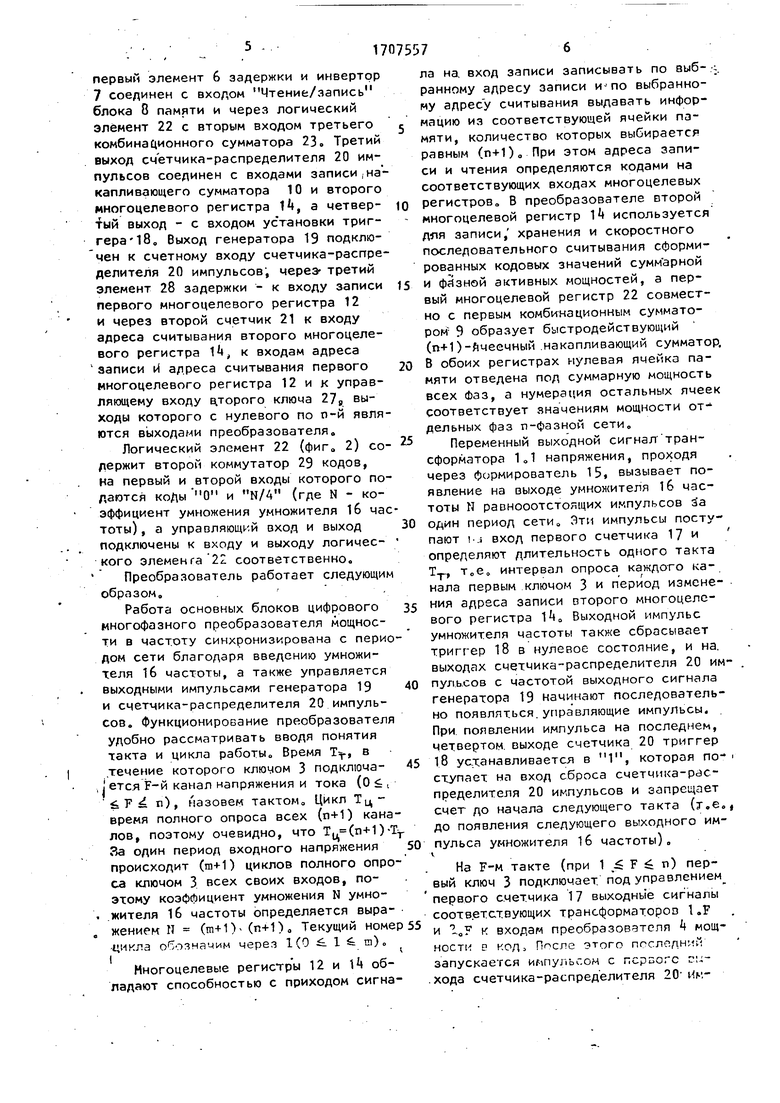

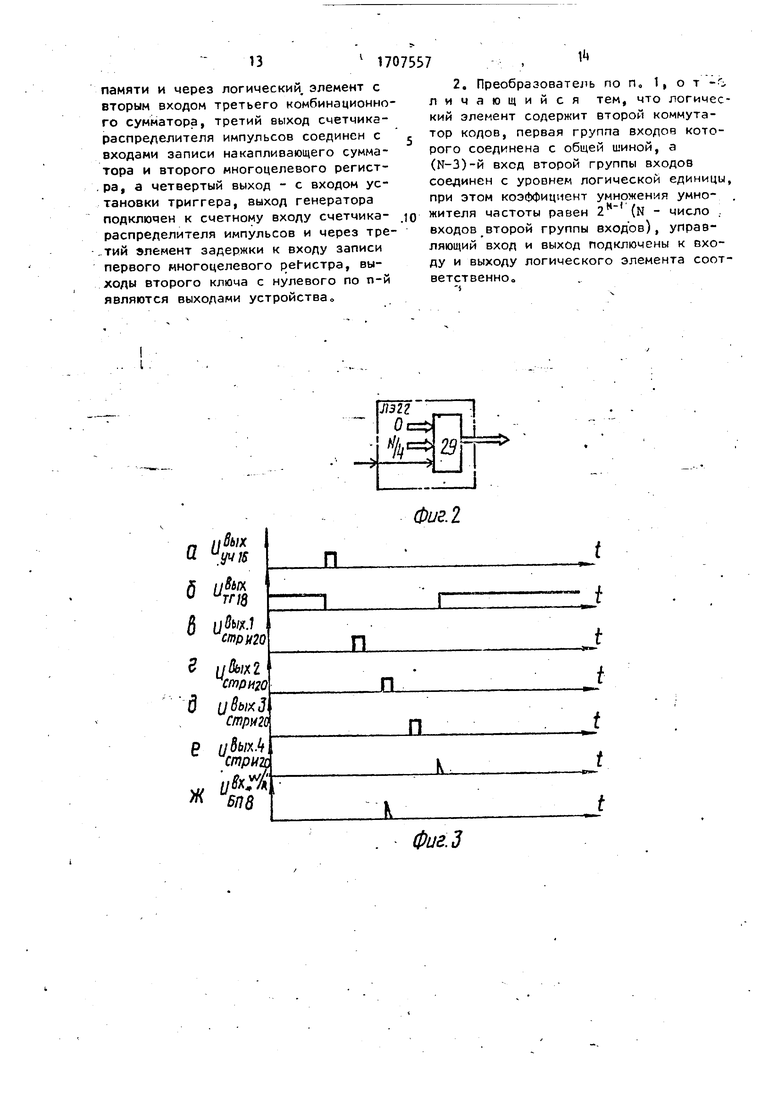

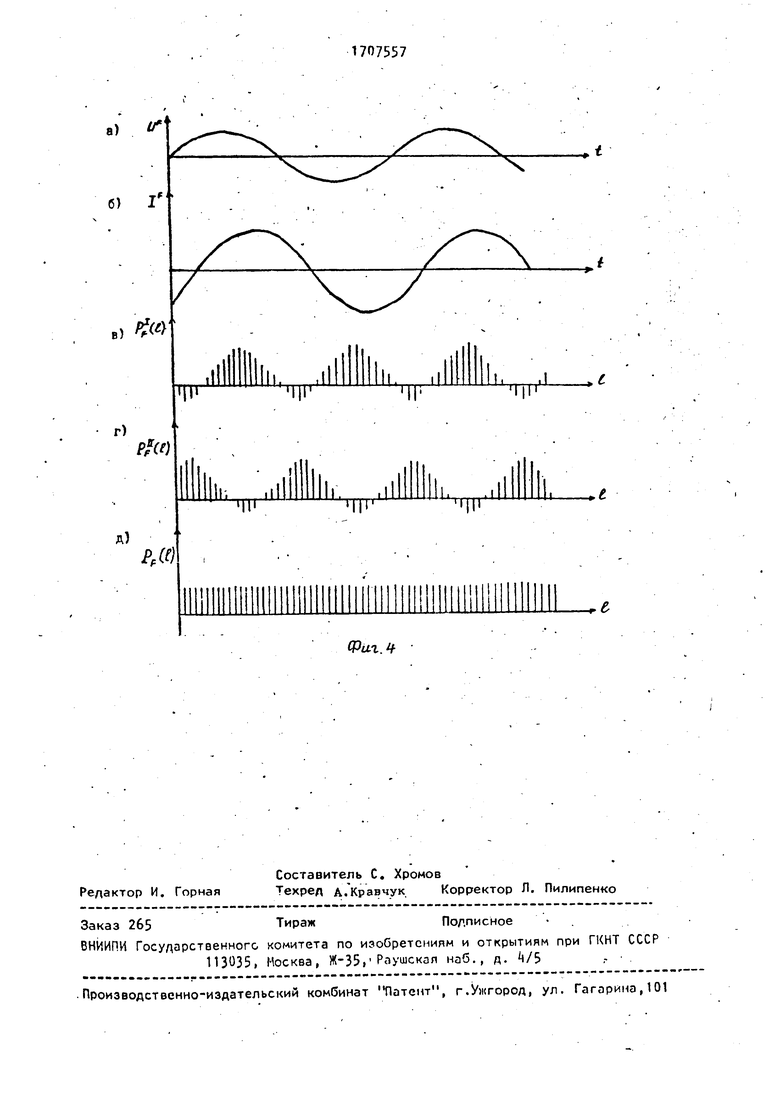

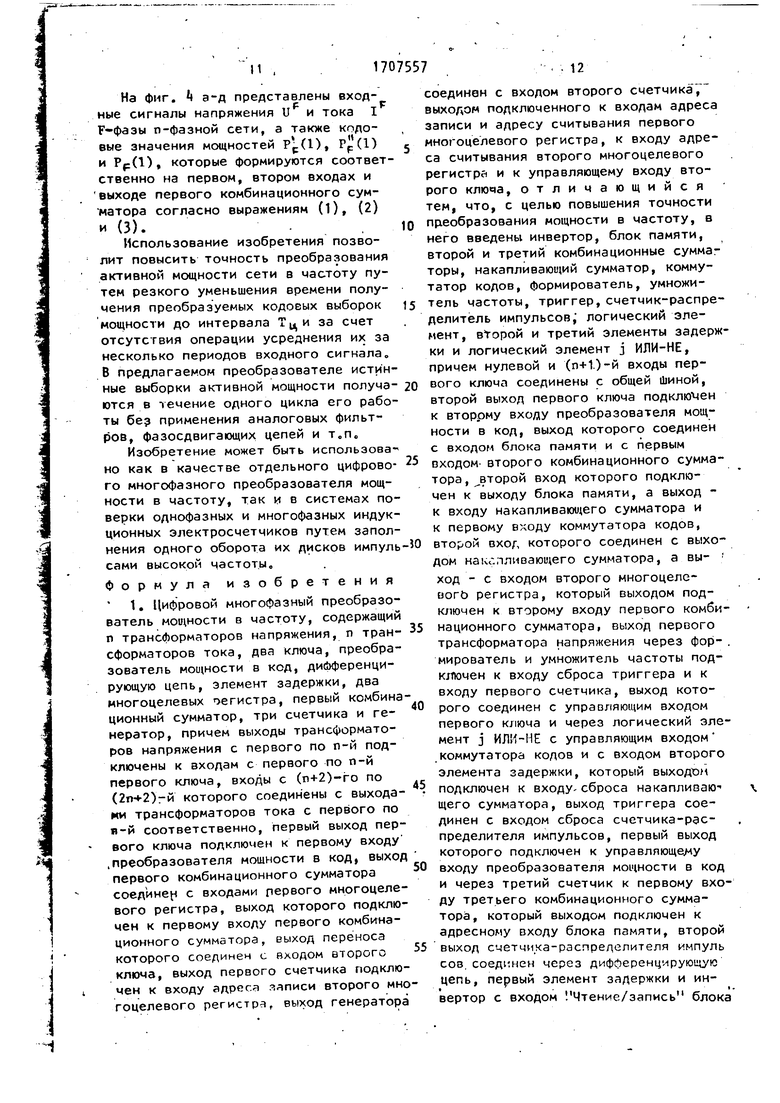

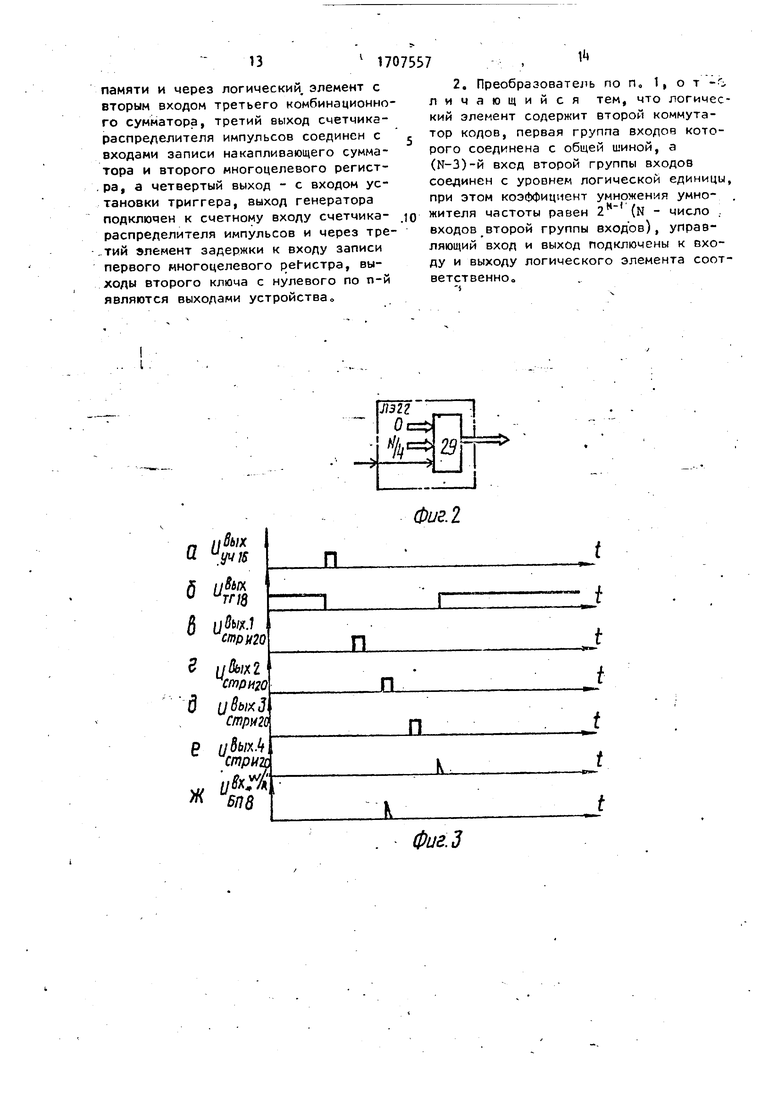

На фиг. 1 представлена блок-схема цифрового многофазного преобразователя мощности в частоту; на фиг0 2 - блок-схема логического элемента; на фиг. 3 временные диаграммы работы ,Q преобразователя; на фиг„ 4 - времен- кые диаграммы входных сигналов и формирующиеся кодовые значения мощности для n-й фазы многофазной сети Цифровой многофазный преобразователь мощности в частоту (фиг. 1) содержит трансфооматоры 1,1-1.п напряжения,трансформаторы 201-2сп тока, первый ключ 3, преобразователь 4 мощности в код, дифференцирующую цепь 5, .„ первый элемент 6 задержки, инвертор 7, блок 8 памяти, первый комбинационный сумматор 9, накапливающий сумматор 10, коммутатор 11 кодов, первый многоцелевой регистр 12, второй ком- , бинацмонный сумматор 13, второй многоцелевой регистр 14, формирователь 15, умножитель 16 частоты, первый счетчик 17, триггер 18, генератор 19; счетчик-распределитель 20 импульсов, второй счетчик 21, логический элемент 22, третий комбинационный сумматор 23, второй элемент 2k задержки, логический элемент i ИЛИ-НЕ 25, третий счетчик 26, второй ключ 27 и трет,Л элемент 28 задержки„

Нулевой и (л-И)-и входы ключа 3 соединены с общей шиной„ Выходы трансформаторов 1.1-1„п напряжения под-

35

50

55

целевые регистры 12, 1Ц, счетчики 17, 21, 26, генератор 19. 1 . ф-лы,

ил.

15

20

25

,Q .„ , ,

35

50

55

ключены к входам с первого по п-й ключа 3, входы с (п+2)-гр по (2п+2)-й которого соединены с выходами трансформаторов Z.1-20n тока соответственно о Первый и второй выходы ключа 3 подключены к первому и второму входам преобразователя 4 мощности в код соответственно, выход которого соединен с входом блока 0 памяти и с первым входом второго комбинационного сумматора 13, второй вход последнего подключен к выходу блока 8 памяти, а выхдд - к входу накапливающего сумматора 10 и к первому входу коммутатора 11 кодов о Второй вход последнего соединен с выходом накапливающего сумматора 10, а выход - с входом второгоо многоцелевого регистра 14, который выходом, подключен к второму входу первого комбинационного сумматора 9, выход которого соединен с входом первого многоцелевого регистра 12, первый вход первого комбинационного сумматора 9 - с выходом многоцелевого регистра 12, а выход, переноса - с входом второго ключа 27. Выход первого трансформатора 1.1 напряжения через формирователь 1 и умножитель 16 частоты подключен к входу сброса триггера 18 и входу первого счетчика 17„ Выход последнего соединен с управляющим входом первого ключа 3, входом адреса записи второго многоцелевого регистра 14 и через логический элемент j ИЛИ-НЕ 25 с управляющим входом коммутатора 11 кодов и входом второго элемента 24 задержки, который выходом подключен к входу сброса накапливающего сумматора 1-00 Выход триггера 18 соединен с входом сброса счетчика-распределителя 20 импульсов, первый выход которого подключен к управляющему входу преобразователя 4 мощности в код и через третий счетчик 26 к первому вхол.У третьего комбинационного сумматора 23, который выходом подключен к адресному входу блока 8 памяти. Второй выход счетчика-распределителя 20 импульсов через дифференцирующую цепь 5,

25

первый элемент 6 задержки и инвертор 7 соединен с входом Чтение/запись блока 8 памяти и через логический элемент 22 с вторым входом третьего с комбинационного сумматора 23. Третий выход счетчика-распределителя 20 импульсов соединен с входами записи/накапливающего сумматора 10 и второго многоцелевого регистра 1, а четвер- ю тый выход - с входом установки триггера 18,, Выход генератора 19 подключен к счетному входу счетчика-распределителя 20 импульсов; через- третий элемент 28 задержки - к входу записи 15 первого многоцелевого регистра 12 и через второй счетчик 21 к входу адреса считывания второго многоцелевого регистра 14, к входам адреса записи и адреса считывания первого 20 многоцелевого регистра 12 и к управляющему входу вдорого ключа 27 „ выходы которого с нулевого по n-й являются выходами преобразователя

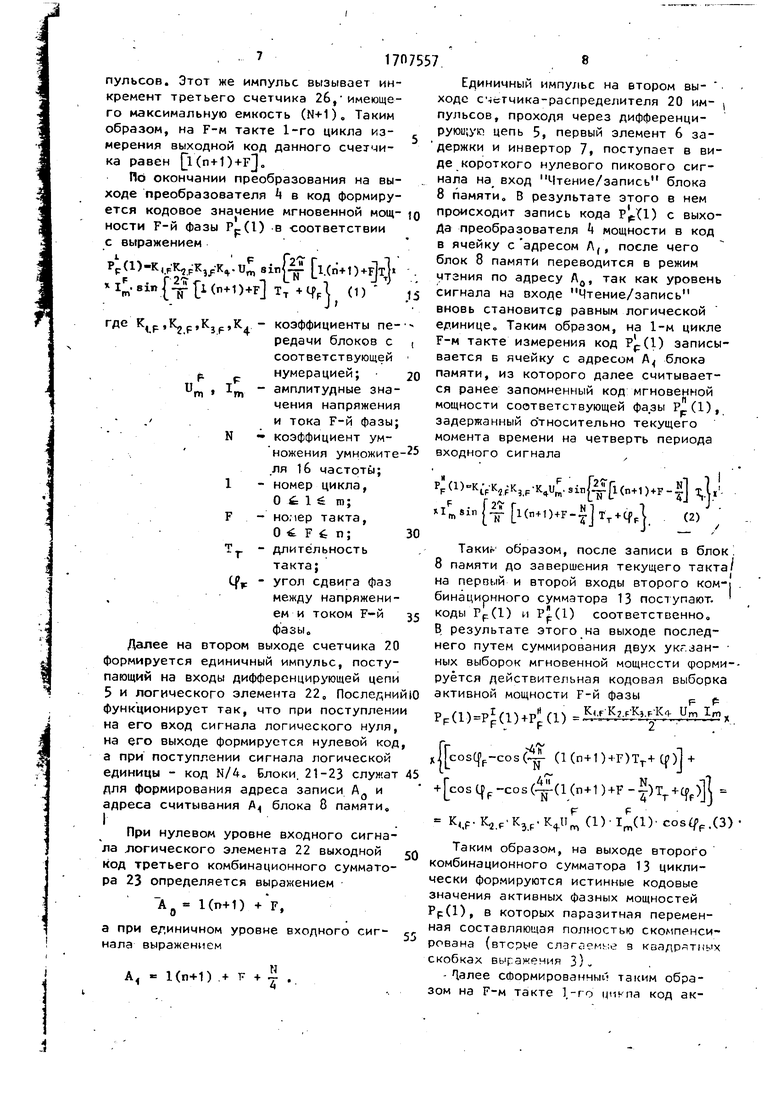

Логический элемент 22 (фиг0 2) содержит второй коммутатор 29 кодов, на первый и второй входы которого подаются коДы О и N/A (где N - коэффициент умножения умножителя 16 частоты) , а управляющий вход и выход 30 подключены к входу и выходу логичес- кого элемента 22 соответственно.

Преобразователь работает следующим образом. . ,

Работа основных блоков цифрового 35 многофазного преобразователя мощности в частоту синхронизирована с периодом сети благодаря введению умножителя 16 частоты, а также управляется выходными импульсами генератора 19 40 и счетчика-распределителя 20 импульсов. Функционирование преобразователя удобно рассматривать вводя понятия такта и цикла работы. Время Т, в .течение которого ключом 3 подключа- 45 j ется F-й канал напряжения и тока (0 Ј , п) , назовем тактом0 Цикл Тц- время полного опроса всех (п+1) каналов, поэтому очевидно, что Тц(п+1)-Ту За один период входного напряжения 50 происходит (т+1) циклов полного опроса ключом 3 всех своих входов, поэтому коэффициент умножения N умно- жителя 16 частоты определяется выра- жением II (га+1) (п+1)„ Текущий номер 55

цикла обозначим через 1(0 1 га) „ I(

Многоцелевые регистр ы 12 и И обладают способностью с приходом сигна5

5 0

0

5 0 5 0 5

ла на, вход записи записывать по выб- . ранному адресу записи и-по выбранному адресу считывания выдавать информацию из соответствующей ячейки памяти, количество которых выбирается равным (п+1)„При этом адреса записи и чтения определяются кодами на соответствующих входах многоцелевых регистров. В преобразователе второй многоцелевой регистр 1 используется для записи, хранения и скоростного последовательного считывания сформированных кодовых значений сумм арной и фазной активных мощностей, а первый многоцелевой регистр 22 совместно с первым комбинационным сумматором 9 образует быстродействующий (п+1)-ячеечный .накапливающий сумматор. В обоих регистрах нулевая ячейка памяти отведена под суммарную мощность всех Фаз, а нумерация остальных ячеек соответствует значениям мощности отдельных фаз п-фазной сети.

Переменный выходной сигнал трансформатора 1„1 напряжения, проходя через формирователь 15, вызывает появление на выходе умножителя 16 частоты N равнооотстолщих импульсов з а один период сети. Эти импульсы поступают -j вход первого счетчика 17 и определяют длительность одного такта Тт, т„е, интервал опроса каждого канала первым ключом 3 и период изменения адреса записи второго многоцелевого регистра 1. Выходной импульс умножителя частоты также сбрасывает триггер 18 в нулевое состояние, и на. выходах счетчика-распределителя 20 импульсов с частотой выходного сигнала генератора 19 начинают последовательно появляться, управляющие импульсы. При. появлении импульса на последнем, четвертом, выходе счетчика 20 триггер 18 устанавливается в 1, которая по- ступает на вход сброса счетчика-распределителя 20 импульсов и запрещает счет до начала следующего такта (т.е., до появления следующего выходного импульса умножителя 16 частоты).

v

На F-м такте (при 1 F п) первый ключ 3 подключает, под управлением первого счетчика 17 выходные сигналы соответствующих трансформатороп 1.F и 10F к входам преобразователя k мощности в KOA3 После этого последний запускается импульсом с псрпогс г:д- хода счетчика-распределителя 20 Импульсов. Этот же импульс вызывает инкремент третьего счетчика 26, имеющего максимальную емкость (N+1). Таким образом, на F-м такте 1-го цикла измерения выходной код данного счетчика равен j(n + 1)+F.

По окончании преобразования на выходе преобразователя k в код формируЕдиничный импульс на втором вы- ходе счетчика-распределителя 20 им- ( пульсов, проходя через дифференцирующую цепь 5, первый элемент 6 задержки и инвертор 7, поступает в виде короткого нулевого пикового сигнала на вход Чтение/запись блока 8 памяти, В результате этого в нем

ется кодовое значение мгновенной мощ- JQ происходит запись кода РД1) с выхоности F-й фазы Рр(1) с выражением

в соответствии

РрСП-К.. 8in l.(n+1)+FJTJ«

Св1.{тгГ1(п+1)+р тт (1)

.15

Да преобразователя k мощности в код в ячейку с адресом Л( после чего блок 8 памяти переводится в режим чтзния по адресу Л0, так как уровень сигнала на входе Чтение/запись вновь становится равным логической единице. Таким образом, на 1-м цикле F-м такте измерения код Рр(1) записы вается Б ячейку с адресом А блока памяти, из которого далее считывается ранее запомненный код мгновенной мощности соответствующей фа.эы Рр(1), задержанный относительно текущего момента времени на четверть периода входного сигнала

I

где .Kjp.KjpjK U

m

Jm N t

20

,-25

коэффициенты передачи блоков с соответствующей нумерацией; амплитудные значения напряжения и тока F-й фазы; коэффициент умножения умножителя 16 частоты; номер цикла, О Ј 1 Ј т; номер такта, О F t n; длительность такта;

угол сдвига фаз между напряжением и током F-й фазы

Далее на втором выходе счетчика 20 формируется единичный импульс, поступающий на входы дифференцирующей цепи 5 и логического элемента 22, ПоследнийЮ

Да преобразователя k мощности в код в ячейку с адресом Л( после чего блок 8 памяти переводится в режим чтзния по адресу Л0, так как уровень сигнала на входе Чтение/запись вновь становится равным логической единице. Таким образом, на 1-м цикле F-м такте измерения код Рр(1) записывается Б ячейку с адресом А блока памяти, из которого далее считывается ранее запомненный код мгновенной мощности соответствующей фа.эы Рр(1),. задержанный относительно текущего момента времени на четверть периода входного сигнала

F

Ч

30

а)-к1ук к31Р-к4и -«{ Ґ: 1(п+1)у- J.«

1mein{ 1 n+1 +F- J rT+Cp,y - (2)

Такиь образом, после записи в блок 8 памяти до завершения текущего такта/ на первый и второй входы второго KOM-I . бинацирнного сумматора 13 поступают, коды Гр(1) и PJL(l) соответственно. В результате этого на выходе последнего путем суммирования двух укгзан- ных выборок мгновенной мощности срорми-- руётся действительная кодовая выборка активной мощности F-й фазы Р. функционирует так, что при поступлении р (;м-р1(П ir CD -fe f -Ч

на РГ-П ovnn гчгндпд пг гииг гкпго HVnn . . i

35

на его вход сигнала логического нуля, на его выходе формируется нулевой код, а при поступлении сигнала логической единицы - код N/4. Блоки. 21-23 служат 45

IjcosCfp-cosC J- (l(n+1)+F)Tr+q) +

единицы - код N/4. блоки. 21-Z3 служат 45 N -,т для формирования адреса записи А0 и p-cos((l (n+1 )+F -j)TT+Јff)J

адреса считывания A блока 8 памяти.

I

При нулевом уровне входного сигнала логического элемента 22 выходной 50 код третьего комбинационного сумматора 23 определяется выражением

чг

К

vCa)-i(n-cos fF.(3

Таким образом, на выходе второго комбинационного сумматора 13 циклически формируются истинные кодовые значения активных фазных мощностей Рр(1), в которых паразитная переменная составляющая полностью скомпенсирована (вторые слагаемые з квадратных скобках выражения ЗК

1(п+1) + F,

а при единичном уровне входного сигнала выражением

А, - 1(п+1) .+ F + ..

Единичный импульс на втором вы- ходе счетчика-распределителя 20 им- ( пульсов, проходя через дифференцирующую цепь 5, первый элемент 6 задержки и инвертор 7, поступает в виде короткого нулевого пикового сигнала на вход Чтение/запись блока 8 памяти, В результате этого в нем

JQ происходит запись кода РД1) с выхо.15

t

20

25

Да преобразователя k мощности в код в ячейку с адресом Л( после чего блок 8 памяти переводится в режим чтзния по адресу Л0, так как уровень сигнала на входе Чтение/запись вновь становится равным логической единице. Таким образом, на 1-м цикле F-м такте измерения код Рр(1) записывается Б ячейку с адресом А блока памяти, из которого далее считывается ранее запомненный код мгновенной мощности соответствующей фа.эы Рр(1),. задержанный относительно текущего момента времени на четверть периода входного сигнала

30

35

чг

К

vCa)-i(n-cos fF.(3

Таким образом, на выходе второго комбинационного сумматора 13 циклически формируются истинные кодовые значения активных фазных мощностей Рр(1), в которых паразитная переменная составляющая полностью скомпенсирована (вторые слагаемые з квадратных скобках выражения ЗК

- 1алее сформированный таким образом на F-м такте 1,-го цикла код активной мощности Рс(1) поступает на входы накапливающего сумматора 10 и на первый вход коммутатора 11 кодов. При 1 Ј F п на выходе логического с элемента j ИЛИ-НЕ 25 присутствует сигнал логического нуля, поэтому на вход второго многоцелевого регистра 1 по- ступает код РР(1У с первого входа

коммутатора 11 кодов. Последующее ю появление управляющего импульса на третьем выходе счетчика-распределителя 20 импульсов вызывает прибавление кода Рр(1) к накопленной ранее сумме в накапливающем сумматоре 10; 15 а также запись данного в F-ю ячейку , второго многоцелевого регистра 1. При этом адрес записи определяется номером такта F, т0е„ выходным кодом счетчика 17.20

Если F 0, т.е. опрашивается нулевой канал первого ключа 3, то на выходах преобразователя А и второго комбинационного сумматора 13 Формируются коды нуля. К этому моменту 5 в накапливающем сумматоре 10 просуммированы все истинные коды фазных активных мощностей предыдущего цикла, т.е.

. г np 30 . . - ff-

Код Р(1) представляет собой кодовую выборку суммарной активной мощности п-фазной сети. При нулевом коде 35 на входе логического элемента j ИЛИ-НЕ 25 появляется единичный сигнал, поэтому выходной код (l) накапливающего сумматора 10 через коммутатор 11 кодов поступает на вход второго многоцеле- 40 вого регистра и с появлением записывающего импульса с третьего выхода счетчика-распределителя 20 импульсов запоминается в нулевой ячейке данного регистра. После этого выходной еди-45 ничный сигнал логического элемента 25i проходя через второй элемент 2 задержки на вход сброса накапливающего сумматора 10, вызывает обнуление

последнего.

Таким образом, в нулевой ячейке второго многоцелевого регистра 1 хранится текущий код суммарной активной мощности зсех п фаз, а в ячейках с первой по n-ю соответствующие текущие коды активных Фазных мощностей. При этом вся хранимая в данном регистре информация полностью обновляетс

ю 15 20

5

30

35 0 5

0

ся потактово на каждом следующем цик ле. - ,

Высокочастотные импульсы с выхода генератора 9, период которых существенно меньше времени одного такта Ту, поступает на вход первого счетчика 21 и через третий элемент 28 задержки на вход записи первого многоцелевого регистра 12. Последний совместно с первым комбинационным сумматором 9 образует скоростной многофазный накапливающий сумматор. Выходные коды второго счетчика 21, изменяющиеся с высокой частотой fr выходных импульсов генератора 19, поступают на вход адреса записи второго многоцелевого регистра I , на входы адреса записи и адреса считывания первого многоцелевого регистра 12 и на управляющий вход второго ключа 27. В результате этого с высокой частотой fr на выход второго многоцелевого регистра Т) последовательно подаются коды из ячеек с адресами с нулевого по п-й, которые далее суммируются в ячейках с соответствующими адресами с нулевого по п-и первого многоцелевого регистра 120 Коды на управляющем входе второго ключа 27 также изменяются. с частотой fr, поэтому импу.ььсы переноса, поступающие на его вход,распре-t деляются по выходам в соответствии с адресацией первого многоцелевого регистра 12. Таким образом, на выходах второго ключа 27 с первого по п-й формируются равномерные высокочастотные импульсные последовательности с частотами, пропорциональными действительным значениям активных мощностей. отдельных фаз с первой по n-ю, а на нулевом выходе - значению активной

суммарной мощности всех п фаз„ i

Логический элемент 22 (фиг. 2), построенный на втором коммутаторе 29, кодов,- выдает на выход код О или N/4 при нулевом или единичном входном управляющем сигналесоответственно.

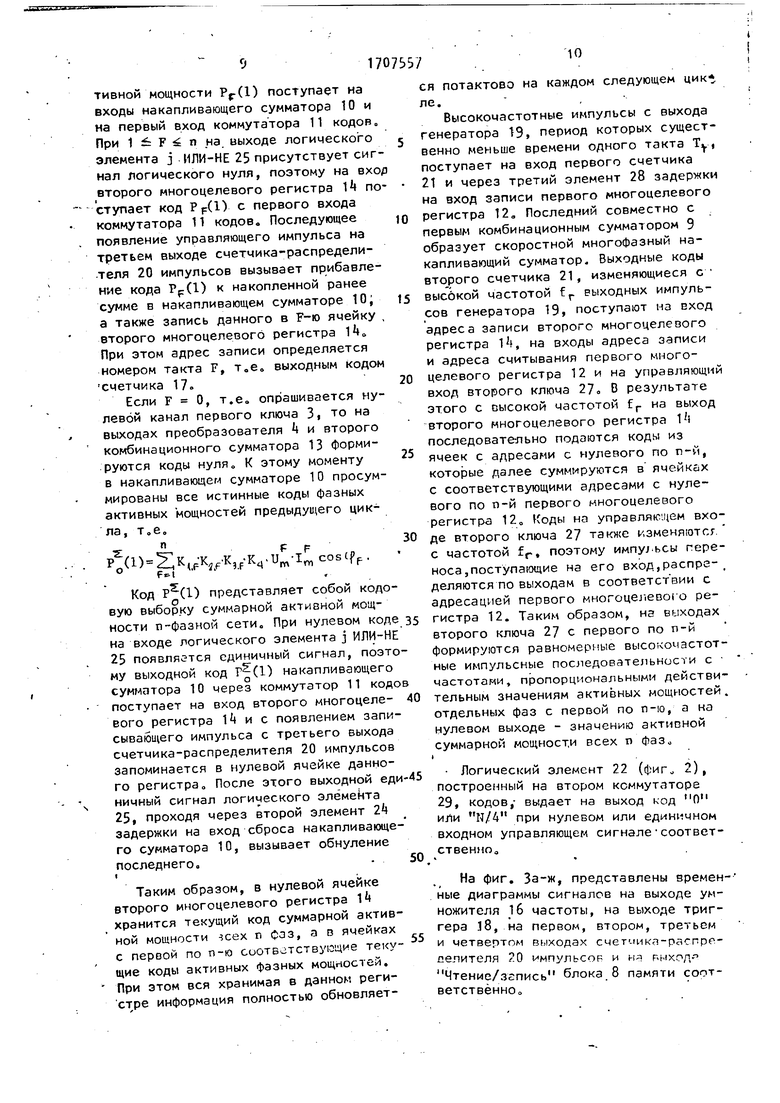

. На фиг. За-ж, представлены времен-1 ные диаграммы сигналов на выходе умножителя 16 частоты, на выходе триггера 8, на первом, втором, третьем и четвертом выходах счетчика-распределителя 20 импульсов и нд выхода

Чтение/запись блока 8 памяти соответственно.

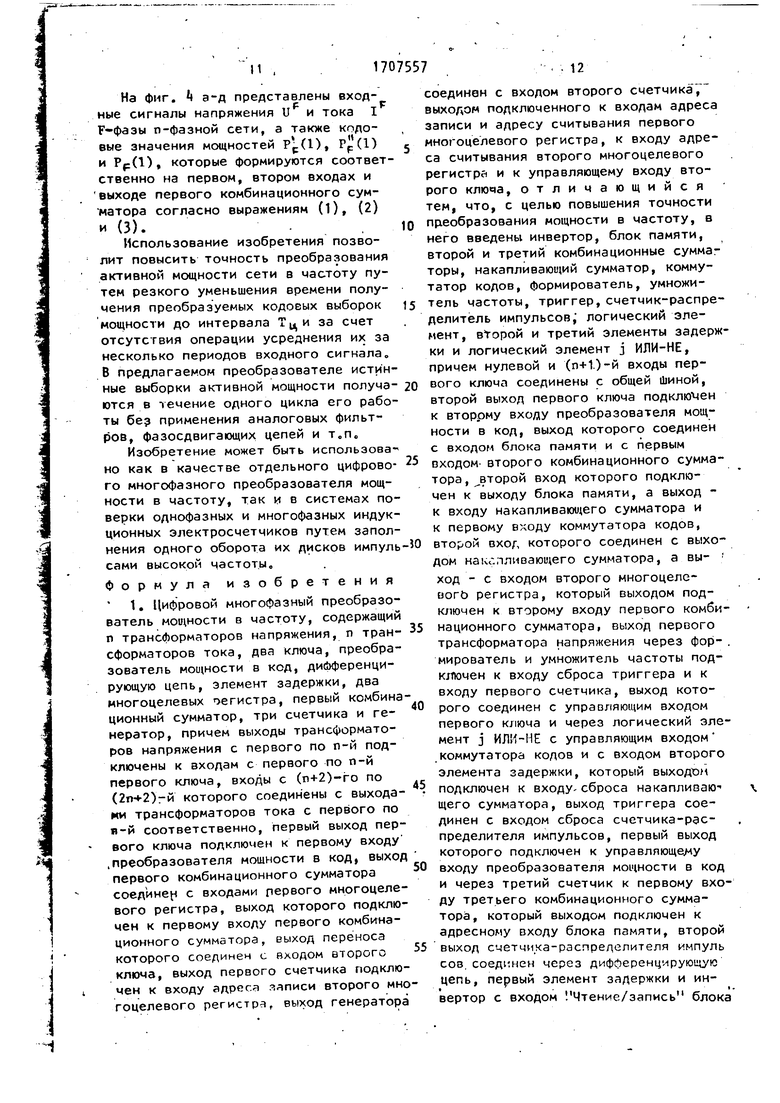

На фиг. Ь э-д представлены входные сигналы напряжения U и тока I F-фаэы п-фазной сети, а также кодовые значения мощностей р р(1), Рр(1) и Рр(1), которые формируются соответственно на первом, втором входах и выходе первого комбинационного сум- матора согласно выражениям (1), (2)

и (3).

Использование изобретения позволит повысить точность преобразования активной мощности сети в частоту путем резкого уменьшения времени получения преобразуемых кодовых выборок мощности до интервала ТцИ за счет отсутствия операции усреднения их за несколько периодов входного сигнала. В предлагаемом преобразователе истинные выборки активной мощности получа- ются в течение одного цикла его работы без применения аналоговых фильтров, фазосдвигающих цепей и т.п.

Изобретение может быть использовано как в качестве отдельного цифрово- го многофазного преобразователя мощности в частоту, так и в системах поверки однофазных и многофазных индукционных электросчетчиков путем заполнения одного оборота их дисков импуль сами высокой частоты.

Формула изобретения 1. Цифровой многофазный преобразователь мощности в частоту, содержащий п трансформаторов напряжения, п тран- сформаторов тока, два ключа, преобразователь мощности в код, дифференцирующую цепь, элемент задержки, два многоцелевых оегистра, первый комбинационный сумматор, три счетчика и генератор, причем выходы трансформаторов напряжения с первого по n-й подключены к входам с первого по п-й первого ключа, входы с (п+2)-го по (2п+2)гй которого соединены с выходами трансформаторов тока с первого по я-й соответственно, первый выход первого ключа подключен к первому входу .преобразователя мощности в код, выход первого комбинационного сумматора соединен с входами первого многоцелевого регистра, выход которого подключен к первому входу первого комбинационного сумматора, выход переноса которого соединен с входом второго ключа, выход первого счетчика подключен к входу адрес) записи второго многоцелевого регистра, выход генератора

5

0

5

0

5

соединен с входом второго счетчика, выходом подключенного к входам адреса записи и адресу считывания первого многоцелевого регистра, к входу адреса считывания второго многоцелевого регистра и к управляющему входу второго ключа, отличающийся тем, что, с целью повышения точности преобразования мощности в частоту, в него введены инвертор, блок памяти, второй и третий комбинационные суммаг торы, накапливающий сумматор, коммутатор кодов, формирователь, умножитель частоты, триггер, счетчик-распределитель импульсов; логический элемент, второй и третий элементы задержки и логический элемент j ИЛИ-НЕ, причем нулевой и (п+1.)-й входы первого ключа соединены с общей Шиной, второй выход первого ключа подключен к второму входу преобразователя мощности в код, выход которого соединен с входом блока памяти и с первым входом- второго комбинационного сумматора, второй вход которого подключен к выходу блока памяти, а выход - к входу накапливающего сумматора и к первому входу коммутатора кодов, второй вход которого соединен с выходом накапливающего сумматора, а вы-

ход - с входом второго многоцелевого регистра, который выходом подключен к второму входу первого комбинационного сумматора, выход первого трансформатора напряжения через фор- . мирователь и умножитель частоты подключен к входу сброса триггера и к входу первого счетчика, выход которого соединен с управляющим входом первого ключа и через логический элемент j ИЛИ-НЕ с управляющим входом коммутатора кодов и с входом второго элемента задержки, который выходам подключен к входу-сброса накапливающего сумматора, выход триггера соединен с входом сброса счетчика-распределителя импульсов, первый выход которого подключен к управляющему входу преобразователя мощности в код и через третий счетчик к первому входу третьего комбинационного сумматора, который выходом подключен к адресному входу блока памяти, второй выход счетчика-распределителя импуль сов. соединен через дифференцирующую цепь, первый элемент задержки и инвертор с входом . Чтение/запись блока

памяти и через логический, элемент с вторым входом третьего комбинационного сумматора, третий выход счетчика- распределителя импульсов соединен с входами записи накапливающего сумматора и второго многоцелевого регист. ра, а четвертый выход - с входом установки триггера, выход генератора подключен к счетному входу счетчика- распределителя импульсов и через тре,тий элемент задержки к входу записи первого многоцелевого регистра, выходы второго ключа с нулевого по п-й являются выходами устройства.

Фиг. 2

фиг.З

б) I

в)

#4

.mllllllii,. ..i1

я)

Р,Ю

1

Фаг. Ц41

Ч|1

-гЈ

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для электрической сигнализации | 1918 |

|

SU16A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1992-01-23—Публикация

1989-09-05—Подача