татора, выходы которого соединены с выходами первого входного коммутатора --и управляющими входами блока памяTti, демодулятор, подключенный входом к входу аналого-цифрового преобразователя и через последовательно включенные селектор строчных синхроимпульсов, генератор синхронизации записи и второй счетчик импульсов - к первому входу блока управления, певый, второй и третий выходы которого соединены соответственно с первыми, вторыми и третьими входами первого и второго выходных коммутаторов, четвертый, пятый и шестой выходы блока . управления соединены соответственно с первыми/ вторыми и третьими входами первого и второго входных коммутаторов, выход генератора синхронизации записи соединен с управляющим входом первого входного коммутатора и с управляющим входом АЦП, N выходов которого через сигнальные входы второго входного коммутатора соединены .с входами блока памяти, выход селектора строчных синхроимпульсов соединен- с вторым входом второго счетчика импульсов, выход первого счетчика импульсов соединен с вторым входом блока управления, введены Детектор- выпадений видеосигналов и блок повторения цикла, причем вход и выход детектора выпадений видеосигналов соединены соответственна с входом демодулятора и с третьим входом блока управления, входы блока Пс1мяти соединены с выходами блока повторения цикла, входы которого соединены с входами ЦАП, а управляющие входы блока повторения цикла соединены соответственно с первым, вторым и третьим выходами блока управления; кроме того блок управления состоит из первого счетчика импульсов, первый, второй и третий выходы которого являются выходами блока управления, и соответственно подключены к первым входам первого и второго элементов, И,, к первым входам третьего и четвертого элементов И, к первым входам пятого и шестото элементов И, а вторые входы -Гретьего и шестого элементов И, второго и пятого элементов И, первого и четвертого элементов И подключены сосггветственно к первому, BTOpo.iy и третьему выходам второго счетчика иглпульсов, выходы которого являются выходами блока управления, выходы второго, четвертого и шестого элементов И через первый элемент ИЛИ подключены, к входу первого инвертора, выход которого через первый вход седьмого элемента И, на второй вход которого, являющийся первым входом блока управления, поданы импульсы считывания, соединен с входом первого счетчика импульсов, а выходы Первого, третьего и пятого элементов И через второй элемент ИЛИ

подключены к входу второго инвертора, выход которого через первыР вход восьмого элемента И, подключен к входу второго счетчика импульсов, на второй вход восьмого элемента И, являющийся вторым входом блока управления, поданы импульсы записи, третий вход блока управления соединен

1

с входом, установки

триггера.

первый выход которого соединен с вторым входом блока управления, второй выход триггера через третий инвертор соединен с третьим входом восьмого элемента И.

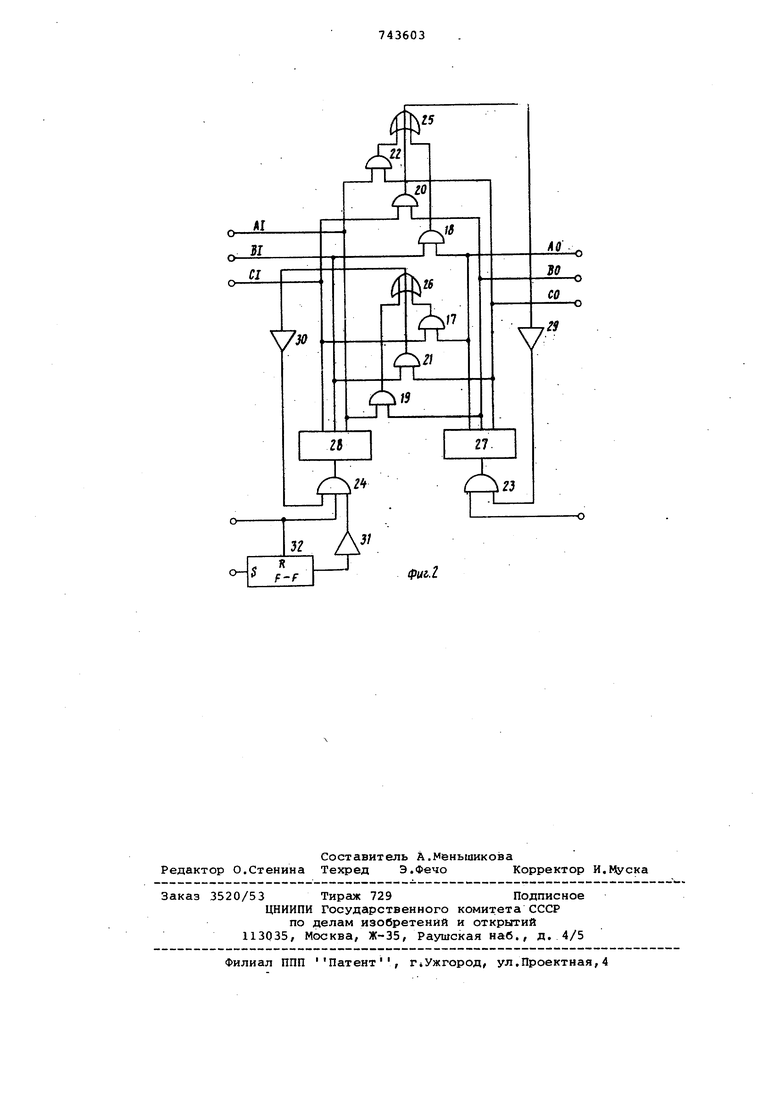

На фиг, 1 приведена структурная электрическая схема предложенного устройства; на фиг, 2 - структурная электрическая схема блока управления

Устройство для коррекции ошибок синхронизации содержит блок памяти 1 первый выходной коммутатор 2, цифроаналоговый преобразователь 3, первый счетчик 4 импульсов, генератор 5 синхронизации считывания, второй выходной коммутатор 6, первый входной коммутатор 7, демодулятор 8, селекто 9- строчных синхроимпульсов, генератор 10 синхронизации записи, второй счетчик 11 импульсов, блок управления 12, аналого-цифровой преобразователь 13, второй входнойкоммутатор 14, детектор 15 выпадений видеосигналов, блок 16 повторения цикла, кроме того, блок .управления 12 состоит из первого, второго, третьего, четвертого, пятого, щестого, седьмого и восьмого элементов И 17-24, первого и второго элементов ИЛИ 25 и 26, первого и второго счетчиков 27 и 28 импульсов, первого, второго и третьего инверторов 29, 30, 31 и триггера 32.

Устройство работает следующим образом.

На вход демодулятора 8 поступают периодические информационные сигналы -такие как воспроизведенные видеосигналы f имеющие ошибки развертки, которые после детектирования или демодуляции пост-упают на аналого-цифровой преобразов-атель 13, Затем демодулированные видеосигналы поступают на селекгор 9, отделяющий от них сигналы горизонтальной.синхронизации для подачи их на генератор 10 синхронизации записи. Генератор Ю синхронизации записи вырабатывает импульсы синхронизации записи сравнительно высокой частоты следования, например около 10,7 МГц„

Импульсы синхронизации записи, имеющие частоту примерно 10,7 МГц, поступают на АЦП 13 для управления частотой, с которой АЦП 13 производит выборку мгновенного значения демодулированных или детектированных видеосигналов и преобразует последние из их первоначальной аналоговой формы в цифровую форму. Конкретно, в ответ на каждый синхроимпульс записи с генератора 10 АЦП 13 производит выборку демодулированного видеосигн ла и преобразует последний во множество параллельных цифровых сигналов, например в цифровую восьмибито вую информацию. Параллельные двоичные сигналы подаются с АЦП 13 на множество входных ключевых схем вхо ного коммутатора 14, каждая из кото рых состоит из множества элементов И, число которых равно числу битов, составляющих преобразованные в цифр вой вид видеосигналы. Выходы входно го коммутатора 14 соединены соответ ственно с блоком памяти 1, Блок памяти 1 содержит множество регистров сдвига, число которых равно числу битов, составляющих преобразованные в цифровой вид видеосигналы. Емкост памяти блока памяти 1 должна быть т кой, чтобы при рассмотрении частоты следования импульсов синхронизации записи, она была достаточна для запомилания одного горизонтального или строчного интервала приходящих видеосигналов или любому целомучис лу таких горизонтальных или строчных интервалов. Затем синхроимпульсы записи подаются с генерат-ора 10 на счетчик 11, вырабатывающий импульс записи интервала, например, в конце каждого горизонтального или строчного интервала приходящих видеосигналов, и сбрасывающийся горизонтсшьными синхровизирующими сигналами с селектора 9 Импульсы записи интервала со счетчик 11 подаются на блок управления 12, который вырабатывает сигналы управления записью А1, В1 и С1 в повторяю щемся циклическом порядке, которые .соответственно подаются на входной коммутатор 14 для. определения последовательностей, в которых выбираются необходимые регистры сдвига блока памяти 1 для записи в них последовательных строчных интервалов, преобразованных в цифровой вид видеосигналов. Затем синхроимпульсы записи с ген ратора 10 подаются на входной коммутатор 7, на другие входы которого поступают сигналы управления записью А1, В1 и С1, и его выходы соединены соответственно с блоком памяти 1. Таким образом, в течение периода или интервала, определяемого сигналом управления записью А1, В1 или С1, преобразованные в цифровой вид видео сигналы проходят через входной коммутатор 14 на блок памяти 1, в то же время блок памяти 1 одновременно получает импульсы синхронизации записи через соответствующий вход вход ного коммутатора 7 для записи преобразованных в цифровой вид видеосигналов в регистрах сдвига блока памяти 1 , После кратковременного хранения в блоке памяти 1 преобразованные в цифровой вид видеосигналы считываются из него последовательно и проходят через выходной коммутатор 2, который, как и входной коммутатор 14, состоит из ключевых схем, соответствующих регистрам сдвига блока памяти 1. Для управления считыванием хранящихся в регистрах сдвига блока памяти 1 видеосигналов устройство имеет генератор 5 синхронизации считывания эталонной частоты, например, 10,70 МГц, по крайней мере, в начале и конце каждого эталонного горизонтального или строчного интервала. Такие синхроимпульсы считывания подаются на счетчик 4, который вырабатывает импульс интервала считывания в начале кгикдого эталонного строчного интервала, и интервальные импульсч считывания подаются на блок 12 управления сигнала, который вырабатывает импульсы управления считыванием АО, ВО и СО в повторяющемся циклическом порядке. Такие сигналы управления считывани-ем АО, ВО и СО подаются на выходной коммутатор 2 для определения последовательности, в которой считываются запомненные видеосигналы из регистров сдвига блока памяти 1. Затем импульсы синхронизации считывания с генератора 5 подаются на выходной коммутатор 6 параллельно и стробируются сигналами управления считыванием АО, ВО и СО. При появлении сигнала управления считыванием АО, ВО или СО соответствующие ключевые схемы выходных коммутаторов 2 и 6 открываются, вызывая считывание запомненных видеосигналов из регистров сдвига блока памяти 1 с частотой синхронизации, определяемой импульсами синхронизации считывания с генератора ,5. Импульсы синхронизации считывания с генератора 5 затем поступают на цифроаналоговый преобразователь 3, который также получает сигнал с выхода выходного коммутатора 2 и который преобразует видеосигналы, последовательно считанные из блока памяти 1, из цифрового вида обратно в первоначальный аналоговый вид, причем видеосигналы в анашоговом виде подаются на выход. Последовательные строчные интервалы приходящих видеосигналов записываются в блок памяти 1 с частотой синхронизации, изменяющейся в целом в соответствии с ошибками развертки приходящих сигналов, и видеосигналы считываются из блока памяти 1 с эталонной частотой синхронизации таким образом, что видеосигналы, получаемые на выходе, полностью освобождены от ошибок развертки.

Ключевые схемы блока 16 повторения цикла принимают также сигналы управления считыванием АО, ВО и СО, При появлении сигнала управления считыйанием АО, ВО или СО для обеспечения считывания сигналов, хран)1шихся в блоке памяти 1, сигналы, считываеivwe из него, одновременно подгштся через блок 16 повторения цикла, с тем чтобы повторно записаться в блок памяти 1. Детектор 15 выпадений, соединенный со входом, необходимым для детектирования любого выпадения в приходящих или воспроизводимых видеосигналах и для выдачи сигнала указания на выпадение на блок управления 12 в ответ на детектирование выпадения-. На входы блока управления 12 поступают интервальные импульсы записи из счетчика 11 и интервальные импульсы считывания из счетчика 4, а также сигнал указания выпадения из детектора 15 выпадений, который соединен с выводом установки триггера 32 в состояние , Выходной сигнал триггера 32 поступает через инвестор 31 на элемент И 24, на который также поступают импульсы записи интервала с выхода счетчика 11. Импульсы считывания интерваша поступают с выхода счетчика 4 на элемент И 23. В нормальных условиях, .т.е. когда приходящие видеосигналы имеют сравнительно малые ошибки развертки, импульсы записи интервала и импульсы считывания интервала, поступающие на входы блока управления 12 соответственно, проходят через элементы И 24 и 23 на соответствующие счетчики 27 и 28 деления на три. Три каскада счетчика 28 деления на три имеют промежуточные выводы для выработки трех сигналов управления записью А1, В1 и С1, которые снимаются с соответствующих выходов блока управления 12. Аналогично три каскада счетчика 27 деления на три имеют промежуточные выводы для йыработки трех сигналов управления считыванием АО, ВО и СО на соответствующих выходах блока управления 12. Сигналы управления записью А1, В1 и С1 в нормальНых условиях вырабатываются последовательно в повторяющемся циклическом порядке счетчиком 28 в ответ на выходные импульсы элемента И 24, соответствующие импульсам записи интервала, поступающим на вход блока управления 12, в результате чего-, к.аждый из сигналов управления записью А1, В1 и С1 будет иметь положит.ельную полярность или иметь сравнительно высокий уровень в течение времени, соответствующего строчному интервалу приходящих видеосиг- налов. Аналогично в нормальных условиях сигналы управления считыванием АО,. ВО И СО вырабатываются последовательно в повторяющемся циклическом порядке счетчиком 27 в ответ на выходные импульсы элемента И 23, которые соответствуют импульсам считывания интервала, поступающим на вход блока управления 12, причем каждый из импульсов управления считыванием АО, ВО и СО имеет положительную полярность или сравнительно высокий уровень в течение времени, равного соответствующему эталонному строчному интервалу. Далее счетчики 28 и 27 предварительно устанавливаются таким образом, что при нормальных условиях сигналы управления считыванием для каждого из регистровых блоков блока памяти 1 оказываются приблизительно посередине между последовательными сигналами управления записи для того же регистрового блока.

Однако в условиях, отличных от нормальных, например, когда приходящие видеосигналы имеют сравнительно большие ошибки развертки, запуск счечиков 27 и 28 импульсами записи интервала и импульсами считывания интервала через элементы И 24 и 23 соответственно может привести к ситуации, когда предпринимается неудачная попытка осуществить одновременные операции записи и считывания в одном из регистровых блоков памяти 1.

Чтобы избежать таких одновременны операций записи и считывания в любом из регистровых блоков блока памяти 1 блок управления 12 включает в себя также три элемента И 19, 21 и 17, которые принимают соответственно управляющие сигналы А1 и ВО, управлящие сигналы В1 и СО и управляющие сигналы С1 и АО, и элемент ИЛИ 26, соединяющий выходы элементов И 19, 21, 17 с инвертором 30. Кроме того, три элемента И18, 20 и 22, выходы которых соединены через элемент ИЛИ 25 с инвертором 29, принимают соответственно управляющие сигналы В1 и АО, управляющие сигналы С1 и ВО и управляющие сигналы А1 и СО,

Когда На вход блока управления 12 не поступает сигнал указания выпадения, триггер 32 выдает сигнал низкого/уровня или отрицательной полярности на инвертор 31, в результате чего последний подает сигнал положительно полярности или высокого уровня на элемент И 24. Когда управляющие сигналы, поступающие на элементы И 19, 21, 17 соответственно, возникают не одновременно, на выходах ни одного из элементов И 19, 21, 17 нет. сигнала, следовательно, элемент ИЛИ 26 не выдает сигнал запрета сравнительно высокого уровня или положительной полярности на инвертер30, в результате чего последний вырабатывает сигнал высокого уровня или положительной полярности на элемент И 24. Таким образом когда ни инвертор 31 ни инвертер 30 не получают сигнала запрета от триггера 32 или от элемента ИЛИ 26 соответственно, элемен И 24 выдает на соответствуквдий счет чик 28 каждый из импульсов записи интервала, поступающий на блок управления 12. Аналогично, коль скоро управляющие сигналы, поступающие на каждый из элементов И 18, 20, 22 соответственно, возникают не одновременно, с элемента ИЛИ 25 не выходит сигнал запрета сравнительно высокого уровня или положительной полярности и, сле довательно, инверт 29 подает сигнал сргшнительно высок го уровня или положительной полярности на элемент И 23, в результате чего последовательные импульсы считывания интервала, поступающие на вход блока управления 12, пропускаю ся через элемент И 23 для запуска со ответствующего счетчика 27. Однако, если на входе блока управ ления 12, соединенного с входом установки появляется сигнал указания выпадения, триггер 32 устанавливается им таким образом, что бы выработать сигнал запрета, который заставляет инвертор 31 подать сигналсравнительно низкого уровня или отрицательной полярности на элемент И 24, в результате чего последний блокирует прохождение импульсов записи интервала со входа блока управления 12 на счетчик 28, приостанавливая задание последовательности последнего до тех пор, пока не исчез нет сигнал указания выпадения на входе блока управления 12 и триггер 32 может быть сброшен следующим импульсом записи интервала, приходящим на вход импульсов записи блока управ ления 12. Аналогично в случае, когда управляющие сигналы, поступающие на элементы И 19, 21, 17, возникнут одновременно, появляющийся в результат этого выходной сигнал, проходящий через элемент ИЛИ 26 на инвертор 30 заставляет последний подать сигнал сравнительно низкого уровня или отри цательной полярности на элемент И 24, в результате чего последний снова блокирует згщание последовательности счетчика 28 импульсом запи си интервала, поступающим в этсм случае на вход блока управления 12. Таким образом, последовательность счетчика 28 продолжает задаваться последовательными импульсами записи интервала, поступающими на вход, лиш до тех пор, пока ни триггер 32, ни элемент ИЛИ 26 не вырабатывают сигнал или импульс запрета задания последовательности. Аналогично задание последовательности счетчика 27 осуществляется последовательными импуль сами считывания интервала, поступающими на вход блока управления 12 только до тех пор, пока элемент ИЛИ 25 не выработает импульс или сигнал запрета задания последовательности, заставляя инвертор 29 подавать сигнал низкогоуровня или отрицательной полярности на элемент И 23, т.е., лишь до тех пэр, пока сигналы управления, поступающие на элементы И 18, 20, 22, не появятся одновременно. Формула изобретения 1, Устройство для коррекции ошибок синхронизации в телевизионных сигналах, содержащее блок памяти, N выходов которого через первый выходной коммутатор соединены с входами цифроаналогового преобразователя (ЦАП), управляющий вход которого соединен с входом первого счетчика импульсов, с выходом генератора синхронизации считывания и с управляющим входом второго выходного коммутатора, выходы которого соединены с выходами первого входного коммутатора и управляющими входами блока памяти, демодулятор, подключенный входом к входу аналого-цифрового преобразователя (АЦП) и через последовательно включенные селектор строчных синхроимпульсов, генератор синхронизации записи и второй счетчик импульсов - к первому входу блока управления, первый, второй и третий выходы которого соединены соответственно с первЕлми, вторыми и третьими входами первого и второго выходных коммутаторов, четвертый, пятый и шестой выходы блока управления соединены соответственно с первыми,.вторыми и третьими входами Первого и второго входных коммутаторов, выход генератора синхрониз.ации записи .соединен с управляющим входом первого входного коммутатора и с управляющим входом АЦП, N выходов которого через сигнальные входы второго входного коммутатора соединены с входами блока памяти, выход селектора строчных синхроимпульсов соединен с вторым входом второго счетчика импульсов, выход первого счетчика импульсов соединен с вторым входом блока управления, о т л и чающее с я тем, что, с целью повышения точности синхронизации, введены детектор выпадений видеосигналов и блок повторения цикла, причем -вход и выход детектора выпадений видеосигналов соединены соответственно с входом демодулятора и с третьим входом блока управления, входы блока памяти соединены с выходами блока повторения цикла, вхо.зы которого соединены с входами ЦАП, а управляющие входы блока повторения цикла соединены соответственно с первым, вторым и третьим выхода дами блока управления.

2. Устройство по п.1, отличающееся тем, что блок управления .состоит из первого счетчика импульсов, первый, второй и третий выходы которого являются выходами блока управления, и соответственно подключены к первым входам первого и второго элементов И, к первым входам третьего и четвертого элементов И, к первым входам пятого и шестого эле.1а, И-, а вторые входы третьего и шйстого элементов И, второго и пятого элементов И, первого и чет-вертого элементов И подключены соответственно к первому, второму и третьему Ьыходам второго счетчика импульсов, выходы которого являются выходами блока управления, выходы второго, четвертого и шестого элементов И через первый элемент ИЛИ подключены к входу первого инвертора выход которого через первый вход седьмого элемента И,на второй вход

которого,, являющийся первым входом блока управления, поданы импульсы считывания, соединен с входом первого счетчика импульсов, а выходы первого, третьего и пятого элементо И через второй элемент ИЛИ подключены к входу второго инвертора, выход которого через первый вход всх;ьмого элемента И, подключен к входу второго счетчика импульсов, на-второй вход восьмого элемента И, являюшийся вторым входом блока управления, поданы импульсы записи, третий вход блока управления соединен с входом установки триггера, певый выход которого соединен с вто-. рым. входом блока управления, второй выход триггера через третий инвертор соединен с третьим входом восьмого элемента И

Источники информации, принятые во внимание при экспертизе

1,. Патент США № 3860952, кл„ 178-5.1, 1974 (прототип)„

O

Авторы

Даты

1980-06-25—Публикация

1975-12-25—Подача