(54) иИФРОВОЙ ИЗМЕРИТЕЛЬ НЕСИММЕТРИИ ТРЕХФАЗНОЙ СЕТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой измеритель несимметрии трехфазной сети | 1980 |

|

SU875311A1 |

| Измеритель симметричных составляющих трехфазной сети | 1977 |

|

SU737882A1 |

| Цифровой измеритель показателей качества электрической энергии трехфазной сети | 1988 |

|

SU1633368A1 |

| Автоматический цифровой измеритель коэффициента гармоник | 1980 |

|

SU911363A1 |

| Цифровой измеритель симметричных составляющих трехфазной сети | 1982 |

|

SU1056081A1 |

| Цифровое устройство для измерения несимметрии напряжений | 1980 |

|

SU993162A1 |

| Цифровой измеритель симметричных составляющих трехфазной сети | 1980 |

|

SU868640A1 |

| Цифровой измеритель симметричных составляющих трехфазной сети | 1981 |

|

SU1012158A1 |

| Цифровой измеритель коэффициента нелинейных искажений | 1976 |

|

SU618695A1 |

| Измеритель коэффициента гар-МОНиК | 1979 |

|

SU819737A1 |

1

Изобретение относится к устройствам дпя контроля качества электроэнергии трехфазных систем переменного тока.

Известно устройство для иэкерення несимметрии режима многофазной сета, содержащее трансформатор, многофазный выпрямитель, частотно-избирательный фильтр, и индикатор составляющей напряжения прямой последовательности l.

При несинусоицальном входном сигнале в вьтрямленном Ьигнале будут присутствовать высшие гармоники, которые приводят к возрастанию погрешности измерения. Кроме того, указанное устройство непригодно для измерения мальве несимметрий, его применение ог эаничено лишь одной частотой сети иэ-за наличия фильтров и имеет дополнительные погрешности, вносимые фильтрами.

Это и другие подобные устройства, основанные на выпрямлении напряжений, не дают возможности и эмерять амплитуды и особенно фазы всех симметричн ных составляющих.

Расширить функциональные возможности измерителей за счет измерения амплитуд и фаз всех симметричных составляющих, а также коэффициента несимметрии позволяет устройство, реализующее корреляционный способ обработки сигналов 2.

Однако поскольку в качестве базисной функции HJH этом используется сигнал прямоугольной формы, то в таких устрой10ствах не устраняется методическая погpeшнocтei вносимая высшими гармониками в нсспедуемой трехфазной системе напряжений.

Известно также устройство для измеtsрения симметричных составляющих трехфазной системы напряжений. В этом устройстве также рализуется коррелятхионный способ обработки, но в качестве базисной функции взят синусоидальный сигнал, что

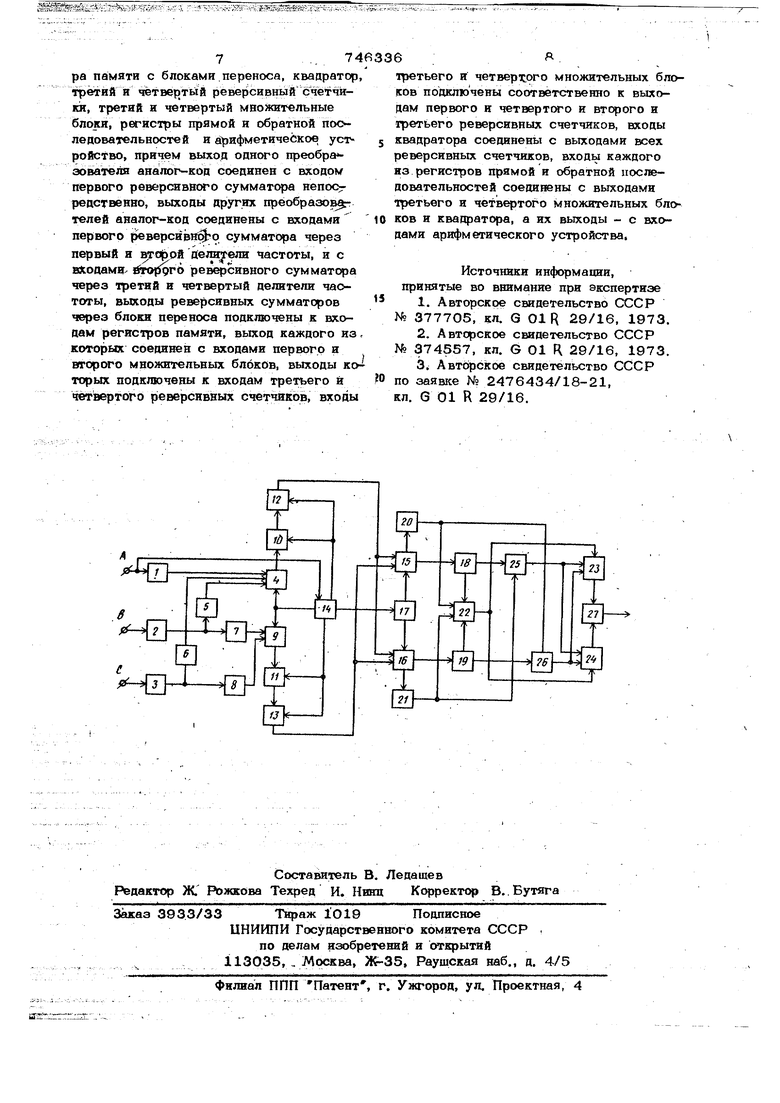

20 позволяет исключить погрешность за счет несинусоидальности трехфазной системы натфяжений. Это устройство является наиболее близким к изобретению по технвг37чесжой сущности (по состйву блоков и функциональным связям между ними) и по достигаемому результату (измерение основных гармоник симме-гричных состав ляющих). Оно содержит преобразователь аналог код, переключатель фаз, фазосдвигающее устройство, пересчетный блок, регистрирующее устройство, реверсивный счетчик, пррогоч ое устройство к задатчик кодов, а также различитепь полярности З Недостатками этого усчройства явпяются низкое быстродействие, так как оно представляет поисковую систему и для определения начальной фазы и амплитуды всех симметричных составляю щих может потребоваться значительное время, и погрешность, обусловленная тем что измерения производятся не одновременно во всех фазах, а разнесены во вре мени., Целью изобретения является повышение точности измерений и быстродействия Поставленная дедь достигается тем, что в цифровой измеритель несимметрии трехфазной сети, содержащий три преобразователя аналог-код, входы которых являются входами устройства, делители частоты, задатчик кодов, первое и второ множительные устройства, входы которых соединены с выходами задатчика ко дов, первый и реверсивные счетчики, подключённые соответственно к выходам множительных блоков, а также блок управления, введены два реверсивных сумматора, два регистра памяти с Олоками переноса, кварратор, третий и четвер ый реверсивный счетчики, третий и четвертый множительны.е блоки, регистры прямой и обратной ПбЙШдбватёль ностей я арифметическое устройство, причем вькод одного преобразователя аналог-код соединен с входом первого реверсивного сумматора непосредственно выходы других преобразователей аналогкод соединены с входами первого реверсивного сумматора через первый и второй делители частоты, а с входами второго реверсивного сумматора - через третий н четвертый делители частоты, вьтходы реверсивных сумматброб через блоки пфеноеа подключены к входам регистров памяти, выход каждого из который соедидан с входами первого и вто роге множительных блоков, выходы которых подключены к входам третьего и 4eTBiBf forb реверсивных счётчик:6в, входы 6 третьего и четвертого множительных блоков подключены соответственно к выходам первого и четвертого и второго и третьего реверсивных счетчиков, входы квадратора соединены с выходами всех реверсивных счетчиков, входы каждого из регистров прямой и обратной последовательностей соединены с выходами третьего и четвертого множительных,блоков и квадратора, а их выходы - с входами арифметического устройства. На чертеже представлена структурная схема цифрового измерителя несимметрии трехфазной сети. Измеритель состоит из -грех преобразователей 1-3 аналог-код (ПАК),ревер;йивнаго сумматора 4, делителей 5-8 час Тоты, реверсивного суммато|за 9, блоков 10 и 11 переноса; perncipOB 12 и 13 памяти, блока 14 управления, первого и второго множительных блоков 15 н 16, задатчика 17 кодов, реаерсивных счетчиков 18-21, квадратора 22, регистра 23 прямой последовательности, регистра 24 обратной последовательности, третьего и четвертого множительных блоков 25 и 26, арифметического устройства 27. Трехфазное напряжение поступает на вход преобразователей 1-3 аналог-код, которые преобразуют мгновенные значения соответствующих фазных напряжений в точках t - в пропорциональный цифровой код. Выход преобразователя 1 подключен к одному входу реверсивного сумматора 4 непосредственно, а вькоды преобразователей 2 и 3 через делители 5 . и 6 - к двум другим входам того же суммутора. Кроме того, выходы феобразрвателей 2 и 3 через делители 7 и 8 подключены к входам реверсивного сумматора 9. Реверсивные сумматоры 9 и 4 связаны поразрядно с блоками переноса 11 и 10 и с регистрами памяти 12 и 13. Блок управления 14 служит для синхронизации работы устройства. Выходы регистров 12 и 13 памяти подключены к первьхм входам множительных блоков 15 и 16, вторые входы которых соединены с вх01;ами задатчика 17 кодов. Выходы множительных блоков 15 и 16 соединены через реверсивные счетчики 18 и 20 и 19 и 21 соответственно с входом квадратора 22 и входами множительных блоков 25 и 26. Входы регистров 23 и 24 прямой и обратной последовательности подключены к входам квадратора 22 и множительных блпков 25 и 26, а вькоды регистров соединены с арифметическим устройством 27. .

Рассмотрим принцип действия уст ройства.

Фазные напряжения U((t),Ug{l)jUc(0 поступают соответственно на преобразователи 1-3 аналог-код.

С выходов преобразователей числовые коды, пропорциональные мгновенным значениям напряжений U(ii ), ), l/cHi) поступают на вход реверсивного сумматора 4, причем с преобразователя 1 на суммирование, а с преобразователей 2 и 3 через делители частоты 5, 6 с коэффициентом деления 0,87 - на . вычитание. В результате в реверсивном сумматоре 4 записывается кодУГ-Ьс)напряжения.

С выходов преобразователей 2 и 3 через делители частоты 7 и 8 с коэффициентом деления 0,5 коды, пропорциональные Ug (tJ к Uc (t L)/ поступают на вход реверсивного сумматора 9. В результате этого в сумматоре 9 записывается код напряжения W(t;).

Коды Vftl) и VVftt) напряжений из реверсивных сумматоров 4 и 9 по команде с блока 14 управления через блоки переноса 10 и 11 вводятся в регистры 12 и 13 памяти..

Посйе переноса кодовУ(1.)и W(t{)Haпряжений в регистры памяти 12 и 13 реверсивные сумматоры 4 и 9 устанавливаются в нулевое состояние и тем самым подготавливаются для записи следующих мгновенных значений V(i).,)H

W(t,,,).

По команде с блока 14 управления код V(t) напряжения поступает на первый и второй множительные блоки 15 и 16, гае перемножается с кодами tosWt и eutWit,задаваемыми задатчиком 17 кодов.

Произведение V(ii.) с выхода .множительного блока 15 поступает на реверсивный счетчик 18, а произведение y(tc)cp6wtu с выхода множительного блока 16 - на реверсивный счетчик 19.

В следующий момент времени код ()напряжения перемножается множительными блоками 15 и 16 с кодами тех же значений ортогональных фyнкцийCosй t

Пpoизвeдёш eW(i)sitla tic выхода множительного блока 15 поступает на реверснвный счетчик 20, а произведение W(ti)

iiiltioutj, с выхода множительного блоа 16 - на реверсивный счетчик 21.

За период исследуемого сигнала (посе обработки кодов мгновенных значений) в реверсивных счетчиках 18-21 будут олучены коды V и W квадратурных составляю ишх основной гармоники напряжений..

Из реверсивных счетчиков 18-21 коды квадратурных составляющих поступают на квадратор 22, а с выхода последнего квадраты этих кодов вводятся в регистры 23 и 24 прямой и обратной последовательнострй. Коды квадратурных составляющих с выходов реверсивных счетчиков 18, 21 и 19, 20 поступают также на входы третьего и четвертого множительных блоков 25 и 26. Ввод кодов в множительные блоки 25 и 26 производится

так, чтобы на их выходе получить коды удвоенных произведений квадратурных ,,В./ и2. Эти коды

Тавляющих

с выходов множительных блоков 25 и 26 поступают на входы регистров 23 и 24 прямой и обратной последовательностей с соответствующим знаком.

В результате в регистре 23 прямой последовательности запишется код V. квадрата прямой последовательности, а в регистре 24 обратной последовательности - код у} квадрата обратной последовательности. Коды V, и У поступают на арифметическое устройство 27, которое опред еляет коэффициент несимметрии.

Таким образом, предлагаемый измеритель позволяет существенно сократить

время измерений и исключить погрещность обусловленную измерением симметричных составляющих по различным реатшзациям исследуемого напряжения.

Формула изобретения

Цифровой измеритель несямметргш „ трехфазной сети, содержащий три преобразователя аналог-код, входы которьк являются входами устройства, делители частоты, задатчик кодов, первый и второй множительные блоки, входы которых соединены с выходами задатчика кодов, первый и второй реверсивный счетчики, подключенные соответственно к выходам множительных блоков, а также блок управления, отличающийся тем, что, с целью повышения точности и быстродействия измерителя, в него введены два реверсивных сумматора, два регийт

pa памяти с блоками переноса, квадратор третий и четвертый реверсивный счётчйкя, третий и четвертый множительные блоки, регистры прямой и обратной последовательностей и йрифметическое устройство, причем выход одного преобра зователя ана лог-код соединен с входом первого реверсивного сумматора непос редственно, выходы других прёобразов телей аналог-код соединены с входами первого реверснвкй о сумматора через первый и второй делители частоты, и с в)1ОдамИ реверсивного сумматора через третий и четвертый делители частоты, выходы реверсивных сумматоров через блоки переноса подключены к входам регистров памяти, выход каждого из которых соединен с входами первого и вяророго множительных блоков, выходы ко торых подключены к юсодам третьего и четвертого реверсивных счетчиков, входы

оретьего и четвертого множительных блоков подключены соответхл-веяно к выходам первого и четвертого и второго и третьего реверсивных счетчиков, входы

квадратора соединены с выходами всех реверсивньпс счетчиков, входы каждого из регистров прямой и обратной последовательностей соединены с выходами третьего и четвертого множительных бло

ков и квадратора, а их выходы - с входами арифметического устройства.

Источники информации, принятые во внимание при экспертизе

3i Авторское свидетельство СССР по заявке № 2476434/18-21, кл. G 01 R 29/16.

Авторы

Даты

1980-07-05—Публикация

1978-03-17—Подача