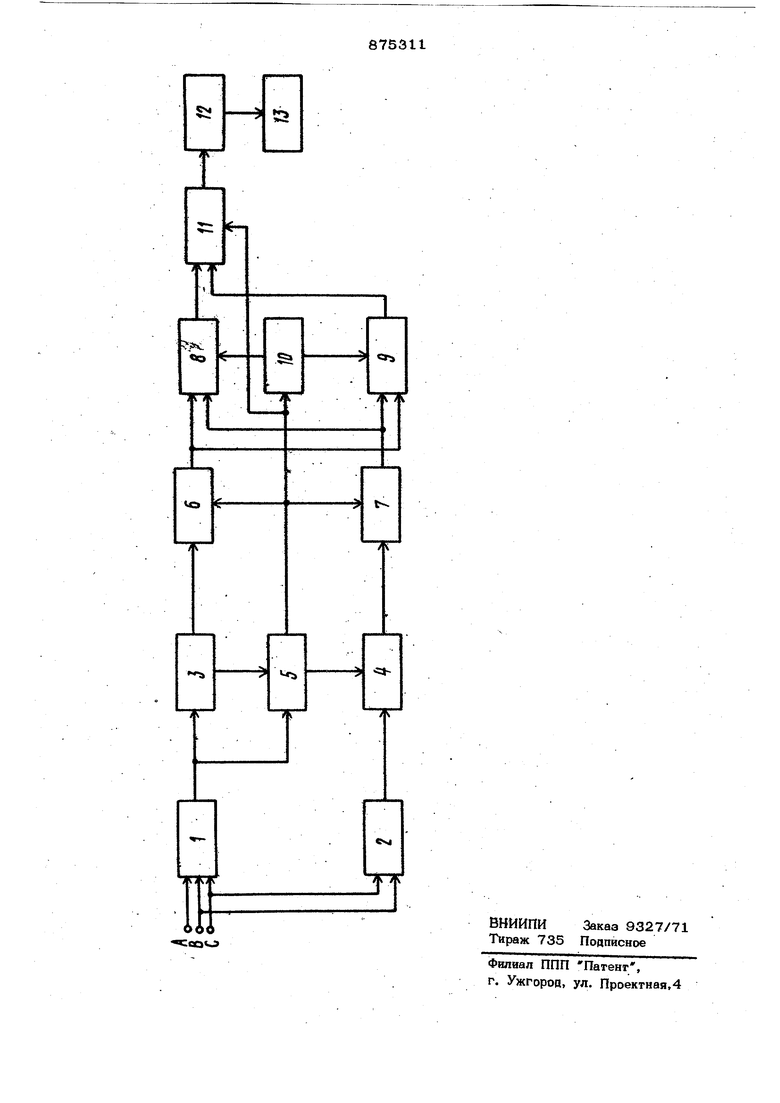

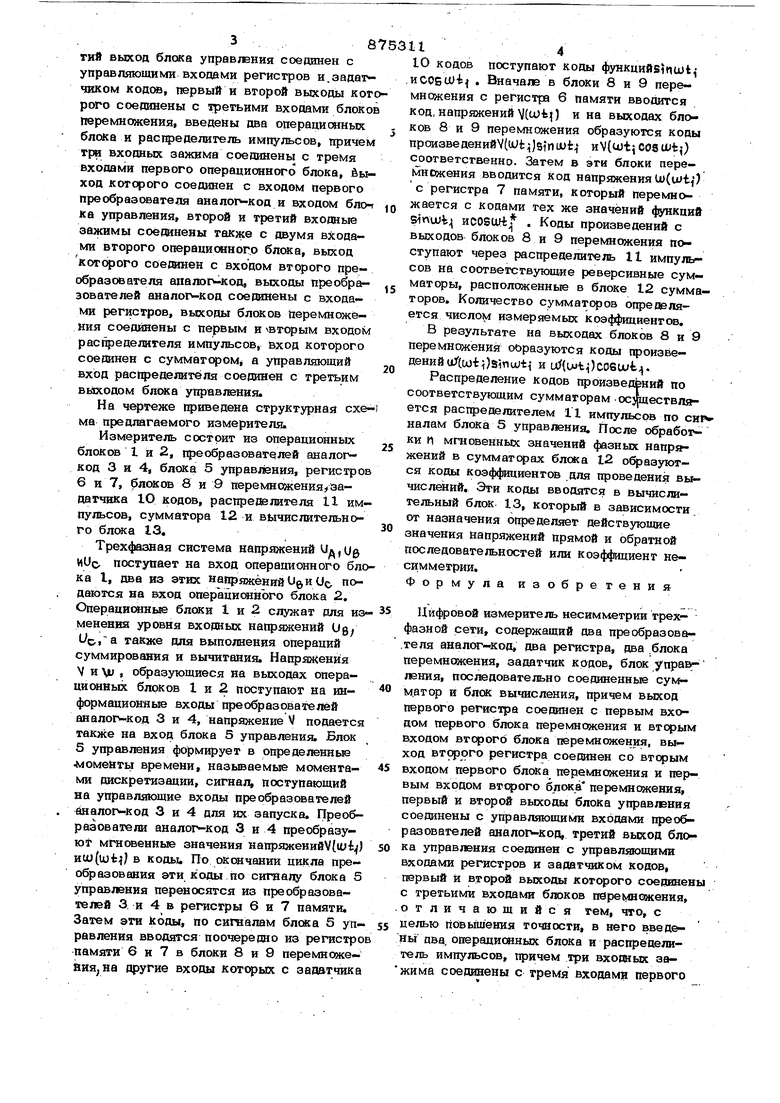

Изобретение относится к области контроля качества электроэнергии трехфазных сетей переменного тока. Известно цифровое устройство дяя измерения симметричных составляющих трех фазной системы переменных напряжений, Содержащее пересчетный блок, преобразователь аналог-коц, множительное устройство, реверсивный счетчик, пороговое уст ройство, фазос игающее устройство, разлячятет полярности, переключатель фаз, регистрирующее устройство. Недостатком этого устройства являемся низкое быстродействие, так как в нем используется поисксжый метод измерения амплитуд симметричных составляющих. Наиболее близким по технической сущности к предлагаемому является измеритель несимметрии трехфазной сети, содеркащий преобразовагелш анало1 -коа, реверсивные сумматсфы, делитеш частоты регистры памяти, множительные устройства, задатчкк кодов, реверсивные счет- чики квадратор, арифметическое устройство, регистры прямой и обратной последовательНостей, блок управ;ения и задач чик кодов. Недостатками известного измерителя являются слоншая аппаратурная реализация и недостаточная точность измерения. Цель изобретения - повышение точности измерения. Поставленная цель достигается тем, что в измеритель несимметрии трехфазной сети, содержащий дэа преобразователя аналор-коо, дза регистра, два блока перекшожения, задатчик кодов, блок управления, последовательно соединенные сумматор и блок вычисления, причем выход первого регистра соединен с :;ервым входом первого блока перемножения и вторым входом второго блока перемножения, выход второго регистра соединен со вторым входом первого блока перемножения и первым входом втсрого блока перемножения, первый и второй выходы блока управления соединены с управляющими входами преобразователей аналог-код, третий выхоа блока управ/ения соединен с управляющими входами регисгров и.задатчиком кодов, первый и вгорой выходы ког рого соединены с третьими входами блоко даремножения, введены два one ради шных блока и распределитель импульсов, причем три входных зажима соединены с тремя входа1 И первого операционного блока, быход которого соединен с входом первого преобразователя аналог код и входом блока управления, второй и третий входные зажимы соединены также с двумя входами второго операционного блока, выход которого соединен с входом второго преобразователя аналог-код, выходы преобраэователей аналог код соединены с входами регистров, выходы блоков перемножения соешйены с первым и вторым входом распределителя импульсов, вход которого соединен с сумматором а управляющий вход распределителя соединен с третьим выходом блока управления. На гфиведена структурная схема предлагаемого измерителя. Измеритель сострит из операционных блоков 1 и 2, преобразователей аналоркод 3 и 4, блока 5 управления, регистров 6 и 7, 0ЛОКОВ 8 и 9 перемножения#эадатчдаа Ю кодов, распределителя 11 импульсов, сумматора 12 и вычислительного блсжа 13, Трехфазная система напряжений |U0 иУс- поступает на вход операционного бло ка I, два на этих напряжений Je и (J подаются на вход операцисиного блока 2. Операционные блоки 1 и 2 служат для из менення уровня входных напряжений U0/ Uc,,a также для выполнения операций суммирования и вычитани$1. Насфяжения V и и , образующиеся на выходах опера- цисжных блоков I и 2 поступают на информационные входы преобразователей аналор-код 3 и 4, напряжение V подается также на вход блока 5 управлениа Блок 5 управ тания формирует в определенные иомейты времени, называемые моментами дискретизации, сигна поступающий на управляющие входы преобразователей алор-код 3 и 4 для их запуска. Преобразователи аналог-код 3 и 4 преобразуют мгновенные значения нaпpяжeиийV() Hiu( в коды. По окончании цикла преобразования эти коды по сигнаду блока 5 управления переносятся из преобразователей 3. и 4 в регистры 6 и 7 памяти. Затем эти Коды, по сигналам блока 5 управления вводятся поочередно из регистро памяти 6 и 7 в блоки 8 и 9 перемножейия,на другие входы котфых с задвгчика 10 кодов поступают коды фyнкцийS1 1Шt HCOStWti . Вначале в блоки 8 и 9 перемножения с регистра б памяти вводится код, напряжений V(u)t) и на выходах блоков 8 и 9 перемножения образуются коды произведенийУ(()д1Пии 1 HV(UJtj ,-) соогвегсгвенно. Затем в эти блоки перемножения вводится код напряжения U)(uit) с регистра 7 пам5ПИ, который перемножается с кодами тех же значений функций Sinuut HCOSUrt . Коды произведений с выходов блоков 8 и 9 перемножения поступают через распределитель It импульсов на соответствуюш1ие реверсивные сумматоры, расположенные в блоке 12 сумматоров. Количество сумматоров опредаляется числом измеряемых коэффициентов. В рааульгате на выходах блоков 8 и 9 перемножения образуются коды произведений u:f(co-ti) sin u;t{ и LXf()COeiut. Распределение кодов гфоизведЬний по соответствующим сумматорам -осшцествляется расгфедалителем 11 импульсов по си1 налам блока 5 управления. После обработки п мгновенных значений фазных напряжений в сумматфах блока 12 образуются коды коэффициентов для проведения вычислший. Эти коды вводятся в вычислительный блок 13, который в зависимости, от назначения определяет действующие значения напряжений прямой и обратной последовательностей или коэффициент несимметрии. Формула изобретения Цифровой измеритель несимметрии трехфазной сети, содержащий два преобразователя аналог-код, два регистра, два блока перемножения, за датчик кодов, блок управления, последовательно соединенные сумматор и блок вычисления, причем выход первого регистра соединен с первым входом первого блока перемножения и вторым входом второго блока перемножения, выход втс|эрго регистра соединен со вторым входом первого блока перемножения и первым входом втфого блока перемножения, первый и второй выходы блока управдания соединены с управляющими входами преобразователей аналор-код, третий выход блока управления соединен с управл 1ющими входами регистров и задатчиком кодов, ПЕЭрвый и второй выходы которого соединены с третьими входами блоков перемножения, .отличающийся тем, что, с целью повышения точности, в него введены два, операционных блока и распределитель импульсов, тфичем три входных соединены с тремя входами первого

операционного блока, выхоа которого динен с вхооом первого преобразователя, аналог-код и входом блока управления, второй и третий входные зажимы coenrae ны также с двумя входами второго оперда онного блока, выход котррого соединен с входом второго преобразователя аналог

код, выходы преобразователей аналогмсод соединены с входамн регистров, выходы блоков перемножения соединены с первым 11 вторым входом распределителя импульсов, вход которого соединен с сумматором, а управляющий вход распределителя соедвнён с третьим выходом блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой измеритель несимметрии трехфазной сети | 1978 |

|

SU746336A1 |

| Устройство для управления @ -пульсным выпрямителем | 1986 |

|

SU1363405A1 |

| Одноканальное устройство для управления @ -пульсным выпрямителем | 1986 |

|

SU1365299A1 |

| Цифровой измеритель симметричных составляющих трехфазной сети | 1981 |

|

SU976403A1 |

| Устройство для регулирования частоты вращения асинхронного электродвигателя | 1979 |

|

SU1010713A1 |

| Цифровой измеритель симметричных составляющих трехфазной сети | 1981 |

|

SU1012158A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

| Измеритель параметров качества электроэнергии трехфазной сети | 1979 |

|

SU1164616A1 |

| Измеритель параметров электрическойэНЕРгии ТРЕХфАзНОй СЕТи | 1979 |

|

SU813263A1 |

| Устройство для измерения показателей качества электроэнергии трехфазной сети | 1982 |

|

SU1064233A1 |

.

to

i I

J П I

k k

Авторы

Даты

1981-10-23—Публикация

1980-02-18—Подача