1

Изобретение относится к устройствам вычислительной техники и может быть использовано для вычисления статистических характеристик случайных , процессов (корреляционных функций, функций распределения и др.).

Известен цифровой комплекс, предназначенный для статистического анализа, содержащий в качестве основных 10 элементов универсальную цифровую вычислительную машину (процессор), аналого-цифровые преобразователи (АЦП) и совокупность других вспомогательных устройств 1. . 15

Однако для адаптации комплекса к диапазону изменения входных сигналов необходимо определить наибольшие и наименьшие значения этих сигналов. Конечность частоты дискретизации 20 АЦП не позволяет уменьшить время определения наибольших и наименьших значений при анализе высокочастотных сигналов. Это приводит, в конечном счете, к снижению относительного 25 (зависящего от спектра сигнала) быстродействия комплекса.

Наиболее близким к изобретению является адаптивный статистический анализатор, предназначенный для- ЗО

адаптивного вычисления различных статистических характеристик, и содер-. жащий блоки определения и фиксации наибольших и наименьших значений,АЦП, процессор, блоки определения относительной разности диапазонов входных сигналов, устройство коррекции и блок управления 2.

Однако при анализе случайных процессов с несимметричными законами распределения и преобразования (квантовании) процессов относительно их наибольших и наименьших значейий в преобразованном процессе возникает смещение, что, в свою очередь, приводит к появлению дополнительной погрешности смещения в вычисленной характеристике.

Цель изобретения - повышение точности вычислений.

Цель достигается тем, что в адаптивный статистический анализатор, содержащий процессор, устройство коррекции, блок определения относительной разности диапазонов входных сигналов, блок управления и п-каналов, каждый из которых содержит блок определения и фиксации наибольших значений, блок определения и фиксации наименьших

значений и аиалого-цифровой преобразователь, первый информационный вход которого является соответствующим входол; анализатора и подключен к первым эходам блока определения и фиксации наибольших значений, блока определения и фиксации наименьших значений своего канала и к соответствующему входу первой группы входов процессора, причем управляоощие входы блоков определения и фиксации наибольших и наименьших зн 1чений подключены к вхо ду блока управления, к управляющим входам процессора, аналого-цифровых преобразователей, устройства коррекци и блока определения относительной разности диапазонов входных сигналов, второй информационный вход каждого аналого-цифрового преобразователя соединен с соответствующим входом блока определения относительной разности диапазонов входных сигналов, выход - с соответствующим входом второй группы входов процессора, а первый и второй информационные входы устройства коррекции соединены соответственно с выходами процессора и блока определения относительной раз ности диапазонов входных сигналов, дополнительно введены в каждом канале схему сравнения и два ключа, выходы которых объединены и подключены к соответствующему входу блока определения и относительной разность диапазонов входных сигналов, первые входы ключей соединены с выходами блока определения и фиксации наибольших значений и блока определения,и фиксации наименьших значений и соответственно с первым и вторым входами схемы сравнения своего канала, выход схемы сравнения подключены к вторым входам ключей своего канала.

Это дает возможность определить в .Ксокдом канале наибольшее и наименьшее значения входного сигнала, выбрать болыпее из них по модулю и осуществить квантование относительно этой величины. Тем самым осуществляется несмещенное преобразование исходного процесса, и вычисленная статистическая характеристика не содержит пО1Т)ешности смещения,

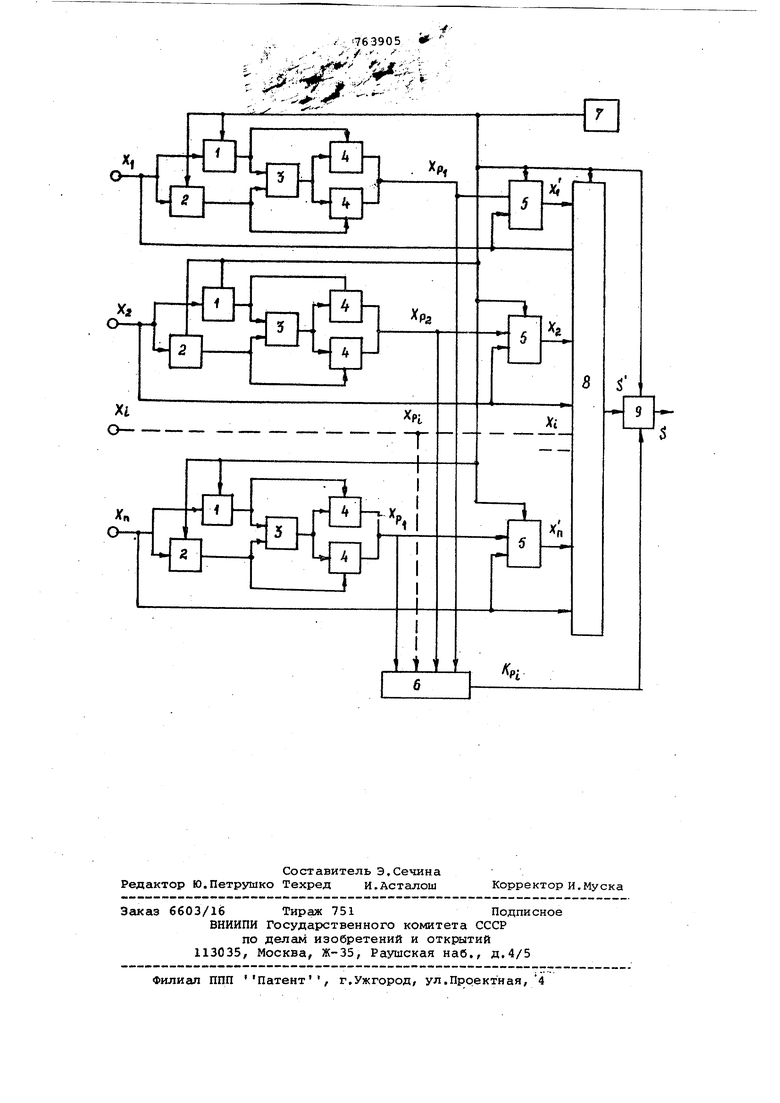

На чертеже приведена блок-схема анализатора. Анализатор содержит блоки 1 определения и фиксации нгшбольших значений, блоки 2 определени и фиксации наименьших значений, п-схем 3 сравнения, п-пар ключей 4, АЦП 5, блок 6 определения относительной разности диапазонов входных сигналов, блок 7 управления, процессор 8, устройство 9 коррекции. Информационный вход АЦП 5 является соответствующим входом анализатора и подключен к первым входам блока Г определения и фиксации Нсшбольших значений, блока 2 определения и фиксации наименьших значений своего канала; и к соответствующему первому входу процессора 8, управляющие входы блоков 1 и 2 определения и фиксации подключены к выходу блока 7 управления, к Управляющим входам процессора 8, АЦП 5, устройства 5 коррекции и блока б определения относительной разности диапазонов входных сигналов, третий вход казкдого АЦП 5 соединен с соответствующим входом блока 6 определения относительной разности диапазонов входных сигналов, а выход - с соответствующим вторым входом процессора 8, первый и второй входы устройства 9 коррекции соединены соответственно с выходами процессора 8 и блока 6 определения относительной разности диапазонов входных сигналов, входы схемы 3 сравнения соединены с выходами устройств 1 и 2 определения и фиксации наибольших значений и определения и фиксации наименьших значений канала соответственно и с первыми входами соответствующей пары ключей 4, вторые входы пары ключей 4 соединены с выходом схемы 3 сравнения, а выходы объединены и подключены к соответствующим входам блока 6 определения относительной разности диапазонов входных сигналов.

Цикл работы анализатора разделяется на два этапа. Первый этап (адаптация) заключается в определении наибольших Х(„д и наименьших Xmip значений случайных процессов Х{.. При этом блок 7 управления включает в работу только блоки 1 и 2 определения и фиксации. После окончания этапа адаптации на их выходах фиксируются величины модулей наибольшего и наименьшего значений сигнала X|Tioix,.l

Эти сигналы поступают на

mini t

входы схемы 3 сравнения. Если

l maxit } mlhil по. управляющему, сигналу схемы 3 сравнения открывается тот ключ 4, на вход которого поступает IXn.-l. . ЕСЛИ .I Viinvl

то открывается другой ключ 4. Таким образом, на выходе пары ключей 4 появляется большее из .| и ГХгп|„ j -Хр . Это сигнал поступает на третий вход АЦП 5, определяя его диапазон преобразования (D{ ) D| -Хр ,

Xp . За счет симметричности границ диапазона преобразования относительно нуля преобразование сигнала Х является несмещенным. На втором этапе осуществляется вычисление совокупности статистических характеристик ,S,...Sv,.-®nY, / например

Блок 1 управления включает преобразователи 5, преобразующие аналоговые 65 сигналы Х{ в цифровые х и задает программу вычисления сбйокупности ха рактеристик s для процессора 8 .5г,.....5й, например , ы т й5Д Величины Хр поступают на соответст вующие входы блока б определения отн сительной разности диапазонов входны сигналов, где определяются коэффициенты отличия Кр диапазонов входных сигналов D от эталонных диапазонов Ол К Хро . где Хрд - эталонное значение Хр, выбранное из условия Pq PiПо управляющим сигналам блока 7 упр ления коэффициенты Кр постудаиот (на пример последовательно во времени) на второй вход устройства 9 коррекции, где определяются коэффициенты коррекции Kg; ,{Кр ), связывающие S .)&-. например ., J. N ч ,,к 4i-VСтатистические характеристики S , п ступающие с выхода процессора 8 на первый вход устройства 9 коррекции, умножаются соответственно на Kgj , и таким образом формируются характе ристики Si . Введение дополнительных элементов: схем сравнения и ключей в изве ную структуру приводит к повышению точности вычислений статистических характеристик исследуек з1х процессов с несимметричными законами распреде ления. Формула изобретения Адаптивный статистический.анализ тор, содержащий процессор, устройст коррекции, блок определения относительной разности диапазонов входных сигналов, блок управления и п-каналов, каждый из которых содержит блок определения и фиксации наибольших значений, блок определения и фиксации наименьших значений и аналого-цифровой преобразователь, первый информационный вход которого является соответствующим входом анализатора и подключен к первым входам блока определения и фиксации наибольших значений, блока определения и фиксации наименьших значений своего канала и к соответст вующему входу первой группы входов процессора, причем управляющие входы блоков определения и фиксации соответственно наибольших и наименьших значений подключены к выходу блока управления, к управляющим входс1М процессора, аналого-цифровых преобразователей, устройства коррекции и блока определения относительной разности диапазонов входных сигналов, второй информационный вход каждогоаналого-цифрового преобразователя соединен с соответствующим входом блока определения относительной разности диапазонов входных сигналов,а выход - с соответствующим входом второй группы входов процессора, первый и второй информационные входы устройства коррекции соединены соответственно с выходами процессора и блока определения относительной разности диапазонов входных сигналов, отличающийся тем, что, с целью повышения точности, он содержит в каждом канале схему сравнения и два ключа, выходы KOTOi«x объединены и подключены к соответствующему входу блока определения относительной разности диапазонов входных сигналов, первые входы соединены с выходами блока определения и фиксации наибольших значений и блока определения и фиксации наименьших значений и соответственно с первым и вторым входами схемы сравнения своего канала, выход cxeNW сравнения подключен к вторым входам ключей своего канала. Источники информации, принятые во внимание при экспертизе 1,Аналоговая и ансшого-цифровая вычислительная техника. М., Машиностроение , 1965, с.87-99, 2,Авторское свидетельство СССР по заявке № 2091264/18-24/, кл. G 06 F 15/36, 1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный статистический анализатор | 1975 |

|

SU736116A1 |

| Анализатор параметров телевизионного передатчика | 1988 |

|

SU1584126A1 |

| Статистический анализатор | 1979 |

|

SU842833A1 |

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2012131C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ И СПОСОБ ЕГО КАЛИБРОВКИ | 2010 |

|

RU2442279C1 |

| УСТРОЙСТВО ДЛЯ РАСПОЗНАВАНИЯ ВИДОВ МАНИПУЛЯЦИИ ЦИФРОВЫХ СИГНАЛОВ | 2002 |

|

RU2235337C2 |

| Адаптивный анализатор плотности распределения амплитуд | 1981 |

|

SU1001110A1 |

| ИЗМЕРИТЕЛЬ ТЕМПЕРАТУРЫ И СПОСОБ ЕЕ ИЗМЕРЕНИЯ | 2017 |

|

RU2677786C1 |

| Статистический анализатор конечной разности фазы | 1987 |

|

SU1422182A1 |

| СПОСОБ И УСТРОЙСТВО КОРРЕКЦИИ ПОГРЕШНОСТЕЙ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 2007 |

|

RU2352060C1 |

Авторы

Даты

1980-09-15—Публикация

1976-04-26—Подача