Изобретение относится к импульсной технике, в частности к преобразователям напряжения в цифровой код с интегрированием входного и опорного напряжений.

Широко известны аналого-цифровые преобразователи (АЦП), которые содержат интегратор, источник опорного напряжения, нуль-орган, два триггера, генератор импульсов и счетчик [1] . В этих АЦП преобразование выполняется в два такта: сначала за To = No/f (f - частота генератора импульсов) интегрируется входной сигнал Uх, а затем полученное напряжение разынтегрируется за Tx = x/f с помощью опорного напряжения Uо, откуда kUxTo = kUoTx, где k - коэффициент интегратора и x=  Nо .

Nо .

Для подавления помех, наложенных на Uх, длительность первого такта должна быть равна (кратна) периоду помехи То = Тп, что недопустимо в этих АЦП, так как это приводит к появлению погрешности в результате преобразования.

Эти погрешности устраняются в другом известном АЦП (авт. св. СССР N 333697, 1972). В нем по сравнению с предыдущим АЦП в первом такте Т1измеряется величина Δ Т, на которую по сравнению с То увеличивает Т1, Δ T = N/f, а во втором такте Т2 разынтегрирование выполняют напряжением Uр= Uо+  ·N , в котором дополнительное к Uо напряжение формируется цифроаналоговым преобразователем (ЦАП). Поэтому уравнение преобразования имеет вид

·N , в котором дополнительное к Uо напряжение формируется цифроаналоговым преобразователем (ЦАП). Поэтому уравнение преобразования имеет вид

k Ux(Tо+ΔT)= k Uо(1+  )Tx

)Tx

или

UxNо(1+  )

) = Uо(1+

= Uо(1+  )

) , x=

, x=  Nо=

Nо=  , где Δ - квант АЦП, равный Uo/No.

, где Δ - квант АЦП, равный Uo/No.

Результат не зависит от Δ Т изменения времени измерения Uх, и ошибки, вызываемые Δ Т, в предыдущем АЦП, устранены.

Для повышения точности АЦП и обеспечения высоких коэффициентов подавления помех необходимо время измерения Ти (интегрирования) входного сигнала изменять в широких пределах, включающих несколько р периодов частоты помехи или ее гармоник.

Выполнение преобразования за Ти = рТо (р = 1 - ро) ведет к неверному результату из-за превышения динамического диапазона интегратора Uо. Поэтому без изменения параметров АЦП увеличение Тинедопустимо. При ро, кратном увеличении Ти, по сравнению с Токоэффициент k интегратора должен быть уменьшен в ро раз; k1 = k/ро. В этом случае при интегрировании Uxm выходное напряжение интегратора не превышает рабочий диапазон Uо.

Необходимо изменить также параметры ЦАП, его диапазон работы, но это связано с большими трудностями при реализации из-за необходимости существенного увеличения точности ЦАП, а при больших значениях ро это вообще нереализуемо.

Изменение k на k1 приводит к потере точности при выполнении преобразования с Ти < роТо, так как относительная погрешность результата преобразования определяется временем измерения Ти.

Рассмотренные недостатки не позволяют использовать АЦП в режиме работы с различными временами измерения входного сигнала, изменяющимся в широких пределах.

Эти недостатки устранены в АЦП [2] , который содержит интегратор, вход которого соединен с выходом аналогового сумматора и с информационным входом первого ключа, а выход - с выходом последнего и с первыми входами нуль-органа и компаратора, второй вход которого через источник опорного напряжения подсоединен к шине нулевого потенциала и к второму входу нуль-органа, выход которого соединен с первым входом блока управления, первый выход которого подсоединен к входу управления второго ключа, выход которого соединен с первым входом аналогового сумматора, второй вход которого подсоединен к выходу третьего ключа, информационный вход которого является входной шиной преобразуемого напряжения, а вход управления соединен с вторым выходом блока управления и с первыми входами первого и второго элементов И, второй вход первого из них соединен с выходом делителя частоты, а выход - со счетным входом первого счетчика, вход установки "0" которого подсоединен к первому входу первого элемента ИЛИ, к выходу переполнения второго счетчика и к счетному входу третьего счетчика, выходы разрядов которого соединены с соответствующими входами делителя частоты, а вход установки "0" объединен с одноименным входом четвертого счетчика и подсоединен к выходу третьего элемента И, первый и второй входы которого соединены соответственно с третьим выходом и вторым входом блока управления, последний из которых является шиной синхронизации и подсоединен к второму входу первого элемента ИЛИ и к входу установки "0" второго счетчика, выходы разрядов которого являются шиной результата преобразования, а счетный вход соединен с выходом второго элемента ИЛИ, первый вход которого подсоединен к выходу второго элемента И, второй вход которого соединен с четвертым выходом блока управления и с входом делителя частоты, вход установки "0" которого подсоединен к выходу первого элемента ИЛИ, при этом пятый выход блока управления соединен с входом управления режимом вычитания четвертого счетчика, выходы разрядов которого подсоединены к входам третьего элемента ИЛИ, и четвертый элемент ИЛИ, выход которого соединен с входом управления первым ключом, первый вход - с выходом компаратора и со счетным входом четвертого счетчика, второй вход - с третьим выходом блока управления, третий вход которого соединен с выходом третьего элемента ИЛИ, последний вход которого соединен с шестым выходом блока управления и с входом управления переключателя, первый вход которого через аналоговый инвертор соединен с вторым входом и с выходом источника опорного напряжения, а выход - с входами четвертого ключа и ЦАП, информационные входы которого соединены с выходами разрядов первого счетчика, а выход - с входом второго ключа, управляющий вход которого объединен с одноименным входом четвертого ключа, выход которого соединен с выходом третьего ключа, вторые входы первого элемента И и второго элемента ИЛИ объединены.

В этом АЦП по сравнению с аналогами время интегрирования задается по внешним синхронизирующим импульсам, интервал времени между которыми выбирается в зависимости от периода частоты помехи Тп или ее гармоник. При этом, если за Ти выходное напряжение интегратора превышает величину его рабочего диапазона, то срабатывает компаратор, выполняется разряд конденсатора интегратора и продолжается дальнейшее интегрирование Uх. За время Ти определяются два кода р и n/р, обеспечивающие соотношение Ти = (pNo + n) t, где t - квант работы АЦП в первом такте; No= To/t и То - наименьшее время интегрирования Uх; q - число срабатываний компаратора.

Во втором такте для выполнения разыинтегрирования и компенсационного интегрирования используется напряжение Uк = Δ (No + n/p), где Δ - квант АЦП, равный Uo/No.

Сначала разыинтегрируется остаточное напряжение Uи1 интегратора за время Тр, а затем q раз выполняется интегрирование Uк до напряжения Uo = kUк Тк, что занимает общее время Т2 = Тр + qТк. Время Т2 преобразуется в код Х результата преобразования с временным квантом:

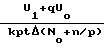

x=  =

=  .

.

Величина (U1 + qUо) равна напряжению, получаемому на выходе интегратора в первом такте, т. е. Uи1 = k Ux Ти = k Uxp(No + n/p)t, поэтому получают X = Ux/Δ , т. е. Х является точным результатом преобразования, который не зависит от величины Ти.

Но данный АЦП имеет недостаток, который состоит в том, что точность получения результата преобразования ограничена в основном из-за наличия составляющих погрешностей, возникающих при получении величины n/p, при преобразовании этой величины в напряжение с помощью ЦАП и при разряде конденсатора интегратора, который приводит к двум видам погрешностей: к остаточному напряжению, уменьшающему величину Uи1, и к исключению интегрирования Uх в течение времени разряда конденсатора интегратора. Наличие этих погрешностей определяет выбор величины Δ кванта АЦП, который нельзя уменьшать с увеличением Ти, и он остается постоянным для всех значений Ти, так как с увеличением Ти увеличиваются составляющие этих погрешностей.

Если исключить эти погрешности, то с увеличением Ти остальные составляющие погрешности от ключей и нуль-органа оказывают все меньшее влияние на относительную погрешность результата преобразования, соответствующего интегралу Uх за время Ти. Поэтому с увеличением Тиможет быть повышена точность АЦП, в котором при этом необходимо обеспечить без изменения рабочий диапазон работы интегратора для всех значений Uх и Ти.

Целью изобретения является повышение точности АЦП.

Цель достигается тем, что в интегрирующий АЦП, содержащий интегратор, вход которого соединен с выходом аналогового сумматора и с информационным входом первого ключа, а выход - с выходом последнего и с первыми входами нуль-органа и компаратора, второй вход которого через источник опорного напряжения подсоединен к шине нулевого потенциала и к второму входу нуль-органа, выход которого соединен с первым входом блока управления, первый выход которого подсоединен к входу управления второго ключа, выход которого соединен с первым входом аналогового сумматора, второй вход которого подсоединен к выходу третьего ключа, информационный вход которого является входной шиной преобразуемого напряжения, а вход управления соединен с вторым выходом блока управления и с первыми входами первого и второго элементов И, второй вход первого из них соединен с выходом делителя частоты, а выход - со счетным входом первого счетчика, вход установки "0" которого подсоединен к первому входу первого элемента ИЛИ, к выходу переполнения второго счетчика и к счетному входу третьего счетчика, выходы разрядов которого соединены с соответствующими входами делителя частоты, а вход установки "0" объединен с одноименным входом четвертого счетчика и подсоединен к выходу третьего элемента И, первый и второй входы которого соединены соответственно с третьим выходом и вторым входом блока управления, последний из которых является шиной синхронизации и подсоединен к второму входу первого элемента ИЛИ и к входу установки "0" второго счетчика, выходы разрядов которого являются шиной результата преобразования, а счетный вход соединен с выходом второго элемента ИЛИ, первый вход которого подсоединен к выходу второго элемента И, второй вход которого соединен с четвертым выходом блока управления и с входом делителя частоты, вход установки "0" которого подсоединен к выходу первого элемента ИЛИ, при этом пятый выход блока управления соединен с выходом управления режимом вычитания четвертого счетчика, выходы разрядов которого подсоединены к входам третьего элемента ИЛИ, и четвертый элемент ИЛИ, выход которого соединен с входом управления первым ключом, введены четвертый и пятый элементы И, группа шестых элементов И, пятый и шестой элементы ИЛИ, формирователь импульсов и многозвенная линия задержки, вход которой соединен с выходом пятого элемента ИЛИ, выход - с первым входом пятого элемента И, а выходы звеньев - с первыми входами соответствующих шестых элементов И, вторые входы которых подсоединены к выходам соответствующих разрядов первого счетчика, а третьи входы объединены и подсоединены к второму входу пятого элемента И и к выходу третьего элемента ИЛИ, который является выходной шиной готовности результата преобразования, при этом выход пятого элемента И соединен с вторым входом второго элемента ИЛИ, с первым входом пятого элемента ИЛИ и со счетным входом первого старшего разряда четвертого счетчика, счетные входы младших и средних разрядов которого, кроме первого среднего разряда, соединены с выходами соответствующих шестых элементов И, счетный вход первого среднего разряда - с выходом шестого элемента ИЛИ, а вход установки "0" - с третьим входом блока управления, четвертый вход которого подсоединен к выходу компаратора, первый выход - к первым входам четвертых элементов И и ИЛИ, второй выход - к второму входу последнего, а четвертый выход - к второму входу четвертого элемента И, выход которого соединен с первым входом шестого элемента ИЛИ, второй вход которого подсоединен к выходу среднего звена линии задержки, последний вход третьего элемента ИЛИ объединен с выходом четвертого элемента ИЛИ и через формирователь импульсов подсоединен к второму входу пятого элемента ИЛИ, информационный вход второго ключа соединен с вторым входом компаратора, а выходы разрядов третьего счетчика являются выходной шиной величины кванта результата преобразования.

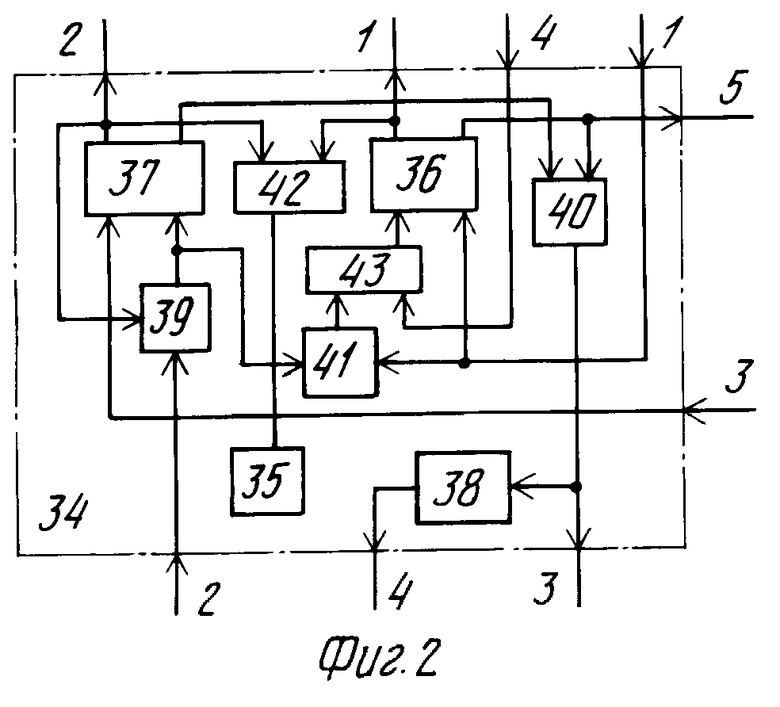

Блок управления выполнен на двух триггерах, управляемом генераторе импульсов, трех элементах И, двух элементах ИЛИ и накопительном элементе, выход которого соединен с выходом первого элемента ИЛИ, входы которого подсоединены к выходам "1" первого и второго триггеров, которые являются соответственно первым и вторым входами блока, последний из которых подсоединен к первому входу первого элемента И, четвертым и третьим выходами блока являются соответственно выход и вход управляемого генератора, который подсоединен к выходу второго элемента И, первый вход которого соединен с выходом "0" первого триггера, который является пятым выходом блока, первый вход которого соединен с первым входом третьего элемента И и с входом "0" первого триггера, вход "1" которого подсоединен к выходу второго элемента ИЛИ, первый вход которого является четвертым входом блока, а второй вход соединен с выходом третьего элемента И, второй вход которого подсоединен к входу "0" второго триггера и к выходу первого элемента И, второй вход которого является вторым входом блока, третьим входом которого является вход "1" второго триггера, выход "0" которого подсоединен к второму входу второго элемента И.

Среди известных технических решений не обнаружены АЦП, в которых имелись признаки, сходные с отличительными признаками заявляемого технического решения.

В предлагаемом АЦП поставленная техническая задача по устранению недостатка прототипа решается следующим образом. Во-первых, обеспечивается работа интегратора в его рабочем диапазоне с помощью включения совместного интегрирования Uх и -Uо, что не позволяет превысить этот диапазон и исключает необходимость разряда конденсатора интегратора. Во-вторых, коррекция результата преобразования в зависимости от величины Ти выполняется цифровым методом без применения аналоговых элементов, что исключает погрешности ЦАП прототипа и по сравнению с ним позволяет использовать меньший по длительности временной квант работы АЦП. При увеличении Ти благодаря применению этих технических решений уменьшается погрешность АЦП и, как показано ниже, существенно увеличивается точность его работы.

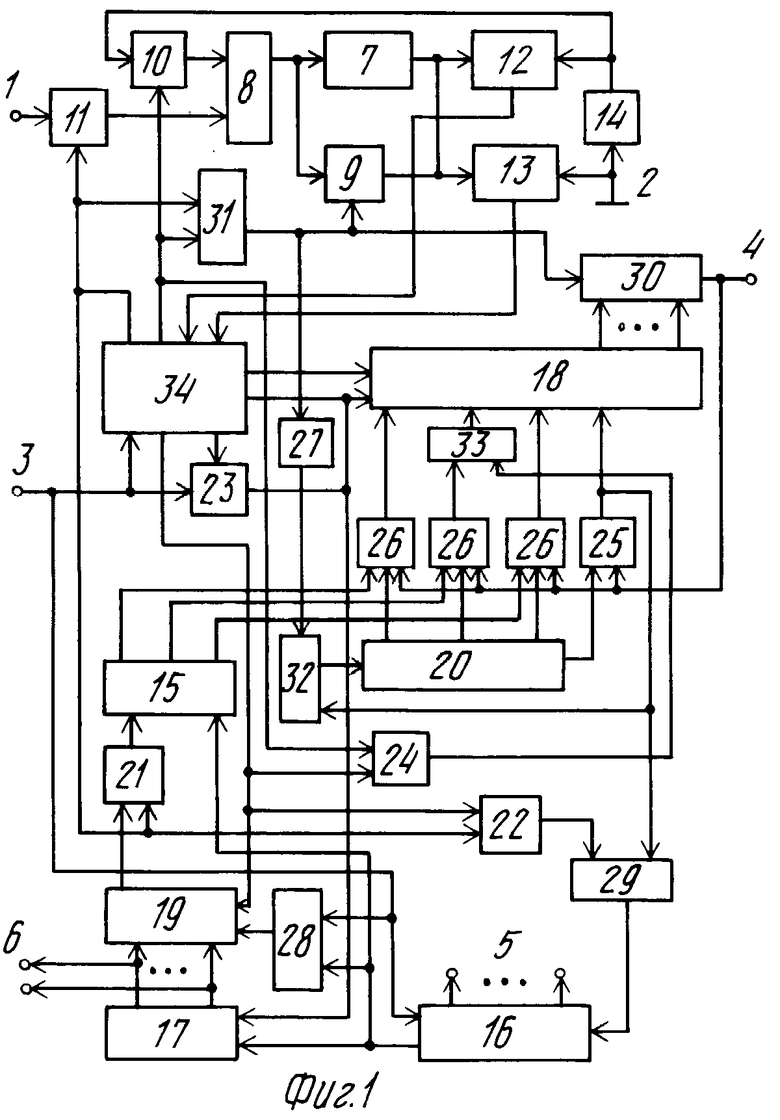

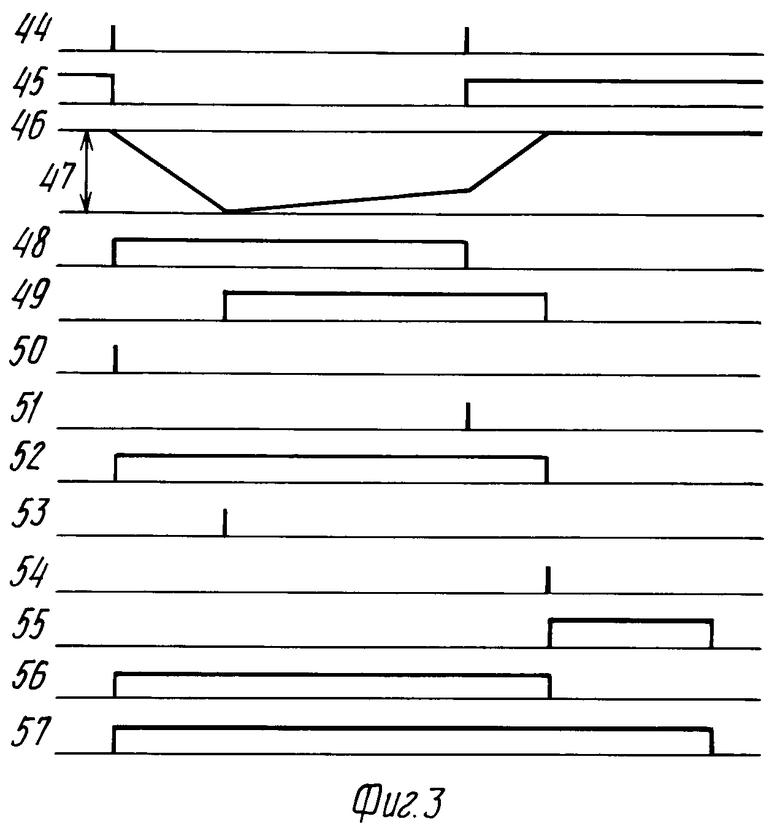

На фиг. 1, 2 и 3 приведены блок-схемы АЦП и его блок управления и временная диаграмма их работы, где 1 и 2 - шины преобразуемого и нулевого напряжений, 3 и 4 - шины синхронизации АЦП и готовности результата преобразования, 5 и 6 - шины результата преобразования и величины его кванта. 7 - интегратор, например, выполненный на операционном усилителе с конденсатором в цепи отрицательной обратной связи, 8 - аналоговый сумматор, например, выполненный на резисторах, 9, 10 и 11 - первый, второй и третий ключи, первый из которых размыкается при наличии сигнала на управляющем входе, а второй и третий замыкаются при наличии этого сигнала, 12 - компаратор, 13 - нуль-орган, 14 - источник опорного напряжения, 15-18 - с первого по четвертый счетчики, 19 - делитель частоты, 20 - многозвенная линия задержки, 21-25 - с первого по пятый элементы И, 26 - группа шестых элементов И, 27 - формирователь импульсов, 28-33 - с первого по шестой элементы ИЛИ, 34 - блок управления, 35 - накопительный элемент, 36 и 37 - первый и второй триггеры, 38 - управляемый генератор импульсов, 39-41 - с первого по третий элементы И, 42 и 43 - первый и второй элементы ИЛИ, 44 - импульсы синхронизации, 45 - сигнал на выходе элемента И 40, 46 и 47 - напряжения на выходе интегратора 7 и источника 14, 48 - 49 - сигналы на выходах "1" триггеров 37 и 36, 50 и 51 - импульсы на выходах элементов И 23 и 39, 52 и 53 - сигналы на выходах нуль-органа 13 и компаратора 12, 54 - импульс формирователя 27, 55 - время работы линии 20 задержки, 56 и 57 - сигналы на выходах элементов ИЛИ 31 и 30.

Шина 1 соединена с входом ключа 11, шина 2 - с входом источника 14 и вторым входом нуль-орагана 13, шина 3 - с вторыми входами блока 34, элементов И 23 и ИЛИ 28 и с входом установки "0" счетчика 16, шина 4 - с выходом элемента ИЛИ 30 и с вторыми входами элементов И 25 и 26, шина 5 - с выходами разрядов счетчика 16, шина 6 - с выходами разрядов счетчика 17 и с входами разрядов делителя 19, вход установки "0" которого соединен с выходом элемента ИЛИ 28, вход - с четвертым выходом блока 34 и вторыми входами элементов И 22 и 24, выход - с вторым входом элемента И 21. Первый вход элемента И 21 соединен с первым и вторым входами элементов И 22 и ИЛИ 31, с вторым выходом блока 34 и с входом управления ключа 11, а выход - со счетным входом счетчика 15, выходы разрядов которого соединены с вторыми входами элементов И 26, а вход установки "0" - с первым входом элемента ИЛИ 28, со счетным входом счетчика 17 и с выходом переполнения счетчика 16. Счетный вход последнего соединен с выходом элемента ИЛИ 29, первый и второй входы которого соединены с выходами элементов И 22 и 25. Последний из них соединен с первым входом элемента ИЛИ 32 и с входом первого старшего разряда счетчика 18, вход первого среднего разряда которого соединен с выходом элемента ИЛИ 33. Остальные входы средних и младших разрядов соединены с выходами элементов И 26, кроме среднего, выход которого соединен с вторым входом элемента ИЛИ 33. Первый вход элемента ИЛИ 33 соединен с выходом элемента И 24, первый вход которого соединен с первым и управляющим входами элементов ИЛИ 31 и ключа 10 и с первым выходом блока 34. Первый и четвертый входы блока 34 соединены с выходами нуль-органа 13 и компаратора 12, а пятый выход и третий вход - с входами управления вычитанием и установки "0" счетчика 18, последний из которых соединен с одноименным входом счетчика 17 и с выходом элемента И 23. Первый вход элемента И 23 соединен с третьим выходом блока 34. Выходы старших разрядов счетчика 18 соединены с входами элемента ИЛИ 30, последний вход которого соединен с выходом элемента ИЛИ 31, с входом управления ключа 9 и через формирователь 27 с вторым входом элемента ИЛИ 32. Выход элемента ИЛИ 32 соединен с входом линии 20 задержки, выходы звеньев которой соединены с первыми входами элементов И 26, а выход - с первым входом элемента И 25. Выходы интегратора 7 и ключа 9 и первые входы нуль-органа 13 и компаратора 12 объединены, второй вход последнего соединен с выходом источника 14 и с входом ключа 10. Выход ключа 10 и выход ключа 11 соединены с входами сумматора 8, выход которого соединен с входами интегратора 7 и ключа 9.

В блоке 34 первый вход соединен с первым входом элемента И 41 и с входом "0" триггера 36, второй вход - с вторым входом элемента И 39, третий вход - с входом "1" триггера 37, четвертый вход - с первым входом элемента ИЛИ 43, первый и второй выходы - с входами элемента ИЛИ 42, и с выходами "1" триггеров 36 и 37. Последний объединен с первым входом элемента И 39, третий и четвертый выходы - с входом и выходом генератора 38, первый из которых объединен с выходом элемента И 40, пятый выход - с первым входом последнего и с выходом "0" триггера 36. Вход "1" триггера 36 соединен с выходом элемента ИЛИ 43, второй вход которого соединен с выходом элемента И 41. Второй вход элемента И 41 соединен с выходом элемента И 39 и с входом "0" триггера 37, выход "0" которого соединен с вторым входом элемента И 40. Выход элемента ИЛИ 42 соединен с выходом элемента 35.

Предлагаемый АЦП работает следующим образом.

При включении питания на время переходных процессов на шинах питания накопительный элемент 35, который может быть выполнен, например, на конденсаторе и резисторе, подключением к шине питания, поддерживает на выходе сигнал с нулевым уровнем. Этот сигнал через элемент ИЛИ 42 поддерживает также нулевой уровень на выходах "1" триггеров 36 и 37, что обеспечивает их установку в нулевое состояние. Сигналы с их выходов "0" с помощью элемента И 40 образуют сигнал 45, который выключает из работы генератор 38 и разрешает работу элемента И 23. Отсутствие сигналов 48 и 49 на выходах "1" триггеров 37 и 36 обеспечивает, во-первых, отключение преобразуемого Uх и опорного напряжений с помощью ключей 11 и 10 от сумматора 8, а, во-вторых, обеспечивает отсутствие сигнала 56 с выхода элемента ИЛИ 31, благодаря чему ключ 9 находится в замкнутом состоянии и интегратор 7 выключен из работы. В этом состоянии АЦП готов к началу выполнения преобразования.

Преобразование в АЦП выполняется по внешним импульсам 44 синхронизации, временной интервал Ти между которыми определяет время интегрирования Uх.

Как и в прототипе, время Ти может изменяться от То - минимального его значения до роТо - наибольшего времени интегрирования Uх. В прототипе временной квант работы АЦП равен t = To/No, а время Тиоценивается величиной

Ти = (pNo + n)t = p (No + n/p)t.

В предлагаемом АЦП величина временного кванта уменьшена в ро раз, т. е. он равен t/ро, и соответственно в ро раз увеличены емкости счетчиков, участвующих в получении р и n/р, которые определяют цифровое значение величины Ти.

Работа АЦП начинается по первому импульсу 44, который устанавливает в "0" счетчик 16 и делитель 19, пройдя через элемент ИЛИ 28, а также, пройдя через элемент И 23 (импульс 50), счетчики 17 и 18 и в "1" триггер 37. Сигнал 48 последнего с помощью ключа 11 подключает Uх к сумматору 8 и далее к интегратору 7, который включается в работу, так как ключ 9 этим сигналом, прошедшим через элемент ИЛИ 31, размыкается и начинается интегрирование Uх.

С появлением сигнала 48 разрешается работа элементов И 21 и 22, снимается сигнал 45 и включается в работу генератор 38, имеющий частоту повторения импульсов po/t, которая определяет временной квант t/pоработы АЦП.

Эти импульсы проходят через элементы И 22 и ИЛИ 29 на счетный вход счетчика 16. Его емкость Nс увеличена в ро раз по сравнению с емкостью Nо прототипа (Nc = No/po).

Через время To = Nct/po, как и в прототипе, на выходе переполнения счетчика 16 появляются импульсы, которые подсчитываются счетчиком 17. За время Ти таких импульсов может быть р, а в интервалах времени То между ними по текущему значению кода р с помощью делителя 19 выполняется формирование импульсов с периодом повторения p˙ t/po. Эти импульсы проходят через элемент и 21 и подсчитываются счетчиком 15.

Делитель частоты может быть выполнен по схеме, приведенной в прототипе, или, например, на основе счетчика, в который записывается код р и выполняется вычитание импульсов входной частоты до получения кода "0", по которому разрешается работа элемента И. Через этот элемент проходит импульс, сдвинутый во времени относительно входных импульсов, на выход делителя частоты и на вход записи кода р в счетчик. Эти циклы повторяются с частотой, уменьшенной в р раз, т. е. на выходе появляются импульсы по прошествии р входных импульсов. Синхронизация работы делителя частоты осуществляется импульсами по входу установки "0", по которым в счетчик записывается код р. При нулевом коде р запрещается работа элемента И и делителя частоты.

К окончанию Ти в младших разрядах счетчика 16, имеющих емкость ро, получен код η , а в старших разрядах с емкостью Nо - код n , т. е. получен общий код (nро + η ). За это время в счетчике 17 образован код р, а в счетчике 15 - код nд=  . В прототипе код n/р формировался при использовании временного кванта, равного pt, и поэтому он имел погрешность

. В прототипе код n/р формировался при использовании временного кванта, равного pt, и поэтому он имел погрешность  , так как

, так как

nt= (pt)nд+(p-1)t

и

nд=  -

-  .

.

В данном АЦП точность получения nд повышена, так как используемый временной квант равен p˙ t/po, а

(npo+η) = nд(p

= nд(p )+(P-1)

)+(P-1)

и

ng=  -

-  = pon/p+η/p-

= pon/p+η/p-  .

.

Код n/р будет получен в старших разрядах счетчика 15, а код η /р - в его младших разрядах, имеющих емкость ро.

Погрешность в nд меньше единицы младшего разряда, вес которого по сравнению с прототипом уменьшен в ро раз, соответственно во столько же раз уменьшена и эта погрешность.

В течение Ти в результате интегрирования Uх интегратором 7 на его выходе будет изменение напряжения -Uи 46 -Uи = -kUх Ти, которое при определенных величинах Uх и Ти может достичь напряжения 47 -Uо, которое принято, как в прототипе, равным рабочему диапазону интегратора.

Для исключения работы интегратора 7 с напряжениями, превышающими этот рабочий диапазон, напряжение -Uи сравнивается компаратором 12 с напряжением 47, равным -Uо. При -Uи = -Uо компаратор срабатывает и его выходной импульс 53 проходит через элемент ИЛИ 43 и устанавливает в "1" триггер 36. Его выходной сигнал 49 с помощью ключа 10 подключает к сумматору 8 опорное напряжение -Uо и разрешает работу элемента И 24. Начиная с этого момента, в интеграторе 7 выполняется режим компенсации при интегрировании напряжения (Ux - Uo) ≅ 0 и его выходное напряжение 46 увеличивается, а счетчиком 18 подсчитываются импульсы генератора 38, прошедшие через элементы И 24 и ИЛИ 33 на счетный вход его первого среднего разряда.

Счетчик 18 имеет три группы разрядов: младшие с емкостью Nо, средние с емкостью ро и старшие с емкостью Noро. Если вес первого старшего разряда принять равным единице, то вес первого среднего разряда равен 1/ро, а первого младшего разряда - 1/Noро. Выходные импульсы, поступающие на счетные входы разрядов счетчика 18, в нем суммируются или вычитаются с учетом этих величин и они используются в выражениях для получаемых кодов.

За время Тк выполнения режима компенсации в первый средний разряд счетчика 18 поступает Nк импульсов

Nк=  = nкpо+ηк, которые образуют код

= nкpо+ηк, которые образуют код

.

.

Окончание Ти определяется по второму импульсу 44, который устанавливает в "0" счетчик 16 и проходит через элемент И 39, образуя импульс 51, а он устанавливает в "0" триггер 37, сигнал 48 которого снимается и отключает от интегратора Uх. Если к этому моменту времени на выходе интегратора 7 Uи1 ≠ 0, о чем подтверждает сигнал 52 нуль-органа 13, и триггер 36 находился в "0", то импульс 51 проходит через элементы И 41 и ИЛИ 43 и устанавливает его в "1".

Режим компенсации, который выполнялся в течение Тк, на этом заканчивается, а сигнал 49 триггера 36 подключает (или поддерживает включенным) к интегратору 7 напряжение -Uо для выполнения режима разынтегрирования остаточного напряжения -Uи1.

Величина -Uи1 определяется по результату интегрирования Uх в течение Ти и выполнения компенсации в течение Тк, т. е.

-Uи1 = к Ux ( Tи - Тк ) -к (Uo - Ux ) Тк

и

-Uи1 = к Ux Ти - к Uo Тк.

При этом необходимо отметить, что в зависимости от соотношения величин Uх и Ти компенсации можно достигнуть до окончания Ти. В этом случае снятие сигнала 52 устанавливает в "0" триггер 36 и отключает от интегратора напряжение -Uо, но он продолжает выполнение интегрирования напряжения Uх до окончания Ти. Для этого случая между Тк и Тр будет временной промежуток.

Подобные случаи могут происходить не для всех величин Uх. Так, например, если в АЦП принять, как и в прототипе, следующие соотношения: Ux = 0 - Um, Um = Uо и при их интегрировании выходное напряжение интегратора -Uи достигает допустимого рабочего диапазона -Uо за время То, т. е. коэффициент интегрирования K = 1/То, то для Ux=  Um или Ux=

Um или Ux=  Um окончание Тк в течение Ти происходит при Ти ≥ 5 1/3 То, а для Ux = 1/2 Um - при Ти ≥ 4 То. Преобразование Ux = Um не приводит к этому при всех значениях Ти = To - poTo.

Um окончание Тк в течение Ти происходит при Ти ≥ 5 1/3 То, а для Ux = 1/2 Um - при Ти ≥ 4 То. Преобразование Ux = Um не приводит к этому при всех значениях Ти = To - poTo.

Процесс разыинтегрирования -Uи1 напряжением -Uо продолжается в течение Тр до выполнения равенства -Uи1 + kUoТр = 0, когда сигнал 52 снимается и устанавливает в "0" триггер 36. Снятие его сигнала 49 отключает от интегратора 7 напряжение -Uо, снимает сигнал 56, который выключает из работы интегратор 7, запускает формирователь 27, образующий импульс 54, и формирует сигнал 45, который выключает из работы генератор 38.

За время Тр, как и при режиме компенсации в течение времени Тк, в первый средний разряд счетчика 18 от генератора 38 поступают импульсы, число которых равно

Nр=  = nрpo+ηр, и они увеличивают код Nк/ро на Nр/ро, сформировав код

= nрpo+ηр, и они увеличивают код Nк/ро на Nр/ро, сформировав код

Nx=  = (nк+nр)+

= (nк+nр)+  = nx+ηx/po.

= nx+ηx/po.

Изменение напряжения -Uи на выходе интегратора за время Ти, Тк и Трможно описать следующим выражением:

kUx(Ти - Тк) - k(Uo - Ux) Ти - k Uo Тр = 0, откуда = U

= U .

.

В этом выражении величина Uх представляет собой среднее значение преобразуемого напряжения за время Ти, полученное в результате интегрировании Uх.

С увеличением Ти величина интеграла от преобразуемого напряжения увеличивается, это позволяет повысить относительную точность в получении величины Uх, т. е. получать результат преобразования с меньшим квантом. Если, как и в прототипе, принять наименьшее время интегрирования равным To = Not = Nopo (t/po), которому соответствует величина кванта Δ= Uo/No, то для Ти ≥ 2То квант результата преобразования может быть уменьшен и для каждого из интервалов времени Ти = рТо - (р + 1) То равен Δр = Δ/р = Uo/Nop.

Величину Ти с учетом временного кванта t/ро, используемого для получения р и nд, можно представить в виде

Ти = (p Nopo + n po + η) t/po, а величины Тк и Тр соответственно

Тк = (nкpo + η к) t/po

и

Тр = (nppo + η p) t/po.

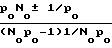

Используя эти величины в выражении Uх, а также значения nд, nx и Δр, получают = U

= U =

=  ·

·  =

=

=  ·

·  = Δр·xр, где Хр представляет собой частное от деления кода Nх, находящегося в счетчике 18, на величину 1 + nд/Nopo.

= Δр·xр, где Хр представляет собой частное от деления кода Nх, находящегося в счетчике 18, на величину 1 + nд/Nopo.

Величина Хр формируется с помощью счетчика 18, линии 20 задержки и элементов И 25, 26 и ИЛИ 30 и 33.

С окончанием Тр, когда снимается сигнал 56, сигнал 57 остается, так как в счетчике 18 находится код Nх, и он разрешает работу группы элементов И 26 и элемента И 25.

Импульс 54 через элемент ИЛИ 32 поступает на вход многозвенной линии 20 задержки, каждое звено которой может быть выполнено, например, на формирователе импульсов ил на пассивных LC-элементах, или на основе их комбинаций. На выходах ее звеньев последовательно во времени появляются импульсы, которые проходят только через те элементы И 26, у которых на входах от разрядов счетчика 15 присутствуют сигналы "1" кода nд. С выходов элементов И 26, соответствующих разрядам счетчика 15, импульсы поступают на счетные входы соответственно младших и средних разрядов счетчика 18, на вход управления вычитанием которого подан сигнал с выхода "0" триггера 36. Благодаря этому в счетчике 18 выполняется поразрядное вычитание кода nд/Nopo.

Импульс с выхода последнего звена линии 20 задержки проходит через элемент И 25 на счетный вход первого старшего разряда счетчика 18, уменьшая код Nх на единицу, и через элемент ИЛИ 32 на вход линии 20 задержки. Так начинается следующий цикл ее работы. Циклы уменьшения кода Nх в счетчике 18 повторяются в течение времени 55 Тс до получения кода "0" в старших его разрядах, по которому сигнал 57 снимается, работа элементов И 25 и 26 запрещается.

В течение Тс импульсы с выхода элемента И 25 проходят также через элемент ИЛИ 29 на счетный вход счетчика 16, в котором подсчитываются. Число этих импульсов равно Хр, так как в счетчике 18 выполнена операция вычитания, описываемая выражением

Nx - Xp (1 + nд/Nopo)

или

xр=  .

.

Таким образом, с окончанием Тс в счетчике 16 сформирован результат преобразования Хр, который передается по шине 5, а о его готовности информирует снятие сигнала 57 на шине 4, при этом по шине 6 передается код р, который характеризует величину кванта Δ р = Δ /р, соответствующую единице младшего разряда кода Хр результата преобразования.

При Uх = 0 с окончанием Ти сигналы 56 и 57 снимаются, операция вычитания в счетчике не выполняются, в счетчике 16 остается код Хр = 0 и преобразование выполняется за время Ти.

В отличие от прототипа, имеющего точность преобразования, определяемую квантом Δ = Uo/No для всех значений времени интегрирования Ти, которое может изменяться в диапазоне от То до роТо, предлагаемый АЦП обеспечивает повышение точности результата преобразования с увеличением времени Ти = рТо (р > 1), при котором уменьшается в р раз вес младшего разряда кода Хр результата преобразования, соответствующий кванту Δ р = Δ /р для Ти, находящемуся в диапазоне временного интервала от рТо до (р + 1)То.

Таким образом предлагаемый АЦП решает поставленную перед ним задачу по устранению недостатка прототипа, в сравнении с которым достигается повышение точности его работы. Это достигается благодаря тому, что исключены составляющие погрешности, присущие прототипу и возникающие при разряде конденсатора интегратора, когда превышается его рабочий диапазон, и при преобразовании кода n/р в напряжение, суммируемое с опорным напряжением при выполнении режима разынтегрирования, а погрешность при получении n/р уменьшена. Достигнуто это без изменения рабочего диапазона интегратора для всех значений времени измерения Ти и при сохранении возможности задания по внешним сигналам произвольной длительности Ти, изменяемой в широких пределах, включающих несколько периодов частоты помехи или ее гармоник, что необходимо для повышения точности и обеспечения подавления помех, положенных на преобразуемое напряжение.

Для оценки повышения точности в выражении для Хр необходимо учесть погрешности, которые могут возникать от квантования временных интервалов при получении кодов Nх и nд и от выполнения операции деления при получении Хр. Наибольшая погрешность в Хр будет при преобразовании Ux = Um = Uо за время Tm = poTo в код Xm = No/po, а наибольшие погрешности Nxи nд равным соответственно ±  и -1. В этом случае уравнение для определения Хр с учетом погрешности ±1, возникающей при выполнении операции деления, примет вид

и -1. В этом случае уравнение для определения Хр с учетом погрешности ±1, возникающей при выполнении операции деления, примет вид

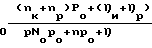

x =

=  ± 1. Для величины Xm = poNo получают Xm1 с числителем (poNo ± 1/po) и знаменателем (poNo - 1) 1/Nopo:

± 1. Для величины Xm = poNo получают Xm1 с числителем (poNo ± 1/po) и знаменателем (poNo - 1) 1/Nopo:

x =

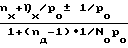

=  ± 1 ≃ Nоpо+1±

± 1 ≃ Nоpо+1±  ± 1= pоNо+(2±

± 1= pоNо+(2±  )= Nоpо+δm, т. е. Xm1 может отличаться от точного результата преобразования Xm на величину погрешности δm незначительно превышающую две единицы младшего разряда Хр, которые соответствуют кванту преобразования Δ po = Uo/Nopo.

)= Nоpо+δm, т. е. Xm1 может отличаться от точного результата преобразования Xm на величину погрешности δm незначительно превышающую две единицы младшего разряда Хр, которые соответствуют кванту преобразования Δ po = Uo/Nopo.

Это показывает, что наибольшая погрешность в Хр может возникнуть при пpеобразовании за наибольшее время Tm = = poTo наибольшего значения Ux = Uo, когда результат преобразования получается с наименьшим квантом Δ ро = Δ /ро, и эта погрешность может быть равной двум квантам Δ ро. Для этого наихудшего случая точность работы АЦП по сравнению с прототипом повышается почти в ро/2 раза.

Необходимо отметить, что по сравнению с прототипом при реализации АЦП целесообразно для уменьшения времени Тс и общего времени преобразования младшие и средние разряды счетчика 18, а также элементы И 25 и 26, ИЛИ 30 и 33 выполнить с использованием быстродействующих интегральных схем, например, серии 100 или 500. Это позволит упростить выполнение многозвенной линии 20 задержки.

Количественную оценку положительного эффекта, который получен при реализации предлагаемого АЦП, можно выполнить, используя параметры преобразователя-прототипа. Этот АЦП имеет точность 0,1% (Nо = 103), То = 20 мс, t = 20 ˙10-6 с, Uo = Uxm= 10 в, квант Δ= 10 мВ. При реализации АЦП современная элементная база не вызывает трудностей обеспечения погрешностей интегратора, не превышающих величины Δ , при его работе в течение нескольких периодов То, например Тm = 16 То = 0,32 с, т. е. величина ро может быть принята равной 16. В этом случае при преобразовании Uх = 10 В за время Ти = 0,32 с точность повышена в 8 раз, а затраты времени на выполнение Тс равны Tcm = (Nopo)qτ , где q - число звеньев линии 20 задержки, которое на единицу больше числа разрядов кода Хр, τ - время задержки одним ее звеном. При величине τ = 0,1 мкс и числе разрядов кода Хр, равном 14, величина

Tсm= 16·103·15·0,1·10-6с= 24 мс.

Для этого случая по сравнению с прототипом в данном АЦП время на получение результата преобразования по окончании разынтегрирования также существенно уменьшается.

Изобретение относится к импульсной технике, в частности к преобразователям напряжения в цифровой код с интегрированем преобразуемого напряжения, и может быть использовано в устройствах сбора аналоговой информации систем контроля и управления, выполняемых на средствах вычислительной техники. Целью изобретения является повышение точности преобразователя за счет исключения и уменьшения погрешностей, влияющих на получение результата преобразования. АЦП содержит интегратор, нуль-орган, компаратор, источник опорного напряжения, сумматор, три ключа, четыре счетчика, делитель частоты, блок управления и логические элементы И и ИЛИ. Новым является введение дополнительных элементов И, двух элементов ИЛИ, формирователя импульсов и многозвенной линии задержки, благодаря которым исключаются и уменьшаются составляющие погрешности и тем самым повышается точность работы АЦП. 1 з. п. ф-лы, 3 ил.

Авторы

Даты

1994-04-30—Публикация

1991-06-21—Подача