1

Изобретение относится к области вычислительной техники и может быть использовано Б устройствах обмена дискретной информации между приборами автоматизированных систем управления .

И;;вестно устройство для передачи и приема ,4искретной информации, содержащее усилители в приемной и передающей частях, связанных линией связи i .

Недостатком его является невысокое быстродействие.

Наиболее близким является устройство для передачи и приема сигналов , содержащее на передающей стороне элемент ИЛИ, входы которого являются входами управляющих сигналов устройства, два усилителя, выходы которых соединены через линию связи со входами усилителей на приемной стороне, выходы которых подключены к двум входам элемента ИЛИ, выход которого соединен со счетным входом счетчика, выход которого подключен к стробирующему входу дешифратора, выходы которого подключены к выходам устг ойства, устройство . также содержит на обеих сторонах

блоки управления, шифраторы и дешифраторы .

Недостатком его является низкая скорость передачи сигналов. Из-за того, что один из информационных сигналов передается по линии связи двумя импульсами: положительным и отрицательным.

Цель изобретения - увеличить

10 быстродействие устройства.

Это достигается тем, что в устройство, содержащее на передающей стороне элемент ИЛИ, входы которого соединены со входами управляющих

15 сигналов устройства, усилители, выходы которых соединены через линию связи со входами усилителей на приемной стороне, выходы которых подключены к двум входам элемента ИЛИ,

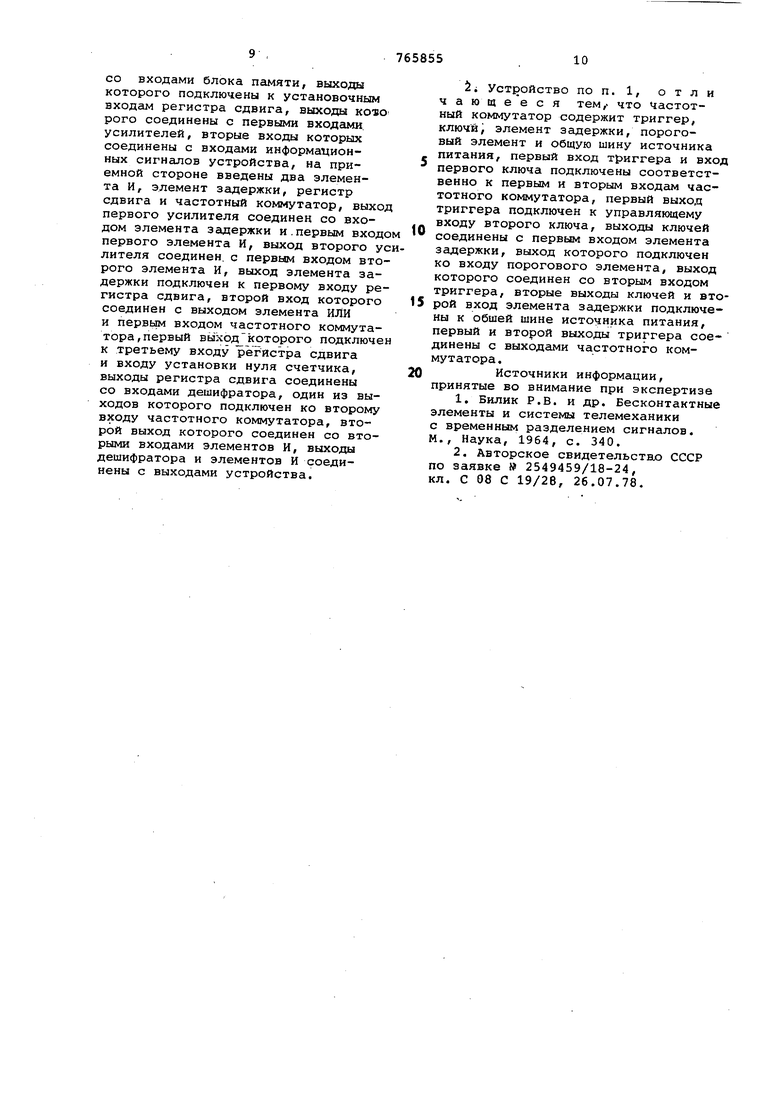

20 выход которого соединен со счетным входом счетчика, выход которого подключен к стробирующему входу дешифратора, выходы которого подключены к выходам устройства, введены на передающей стороне элемент И, счетчик триггер, блок памяти, регистр сдвига и генератор импульсов, который соединен с первым входом элемента И, второй вход которого подключен к первому выходу триггера, второй выход триггера соединен со своим первым входом , выход элемента И подключен к первому входу регистра сдвига и ко входу счетчика, выход которого соединен со вторым входом триггера, третий вход которого подключен к вых ду элемента ИЛИ, входы которого соединены со входами блока памяти, выходы которого подключены к установочным входам регистра сдвига,, выходы которого соединены с первыми входами усилителей, вторые входы которых соединены со входами информационных сигналов устройства, на приемной стороне введены два элемента И элемент задержки, регистр сдвига и частотный коммутатор, выход первого усилителя соединен со входом элемента задержки и первым входом первого элемента И, выход второго усилителя соединен с первьм входом второго элемента И, выход элемента задержки подключен к первому входу регистрасдвига, второй вход которого соединен с выходом элемента ИЛИ и первым входом частотного коммутатора, первый выход которого подключен к третьему входу регистра сдвига и входу установки нуля счетчика, выхо ды регистра сдвига соединены со вхо дами дешифратора, один из выходов которого подключен ко (Второму входу частотного коммутатора, второй -выхо которого соединен со вторыми входам элементов И, выходы дешифратора и элементов И соединены с выходами ус ройства. Кроме того, частотный коммутатор содержит триггер, ключи, элемент задержки , пороговый элемент и общую шину источника питания, первый вход триггера и вход первого ключа подключены соответственно к первым и вторым входам частотного коммутатор первый выход триггера подключен к управляющему входу второго ключа, выходы ключей соединены с первым входом элемента задержки, выход которого подключен ко входу элемента, выход которого соединен со вторым входом триггера, вторые выходы ключей и второй вход элемента задержки подключены к общей шине источника питания, первый и второй выходы триггера соединены с выхода ми- частотного коммутатора. . На фиг. 1 приведена функциональн я схема устройства; на фиг. 2 функциональная схема частотного коммутатора. Предлагаемое устройство содержи генератор 1 импульсов, элемент И 2 триггер 3, разрешающий прохождение импульсов с генератора 1 на элемен И 2, устанавливающий триггер 3 в состояние О после прохождения имп сов, счетчик 4, регистр 5 сдвига, пр йдназначенный для формирования к довой группы, соответствующей одно из управляющих сигналов, поступаю:;их на вход устройства, элемент ИЛИ б с выхода которого задний фронт управляющего сигнала, поступившего на его вход, устанавливает триггер 3 в состояние 1, блок памяти 7, устанавливающий кодовую группу в регистре 5 сдвига, соответствующую одному из поступивших на ее вход ут равляющих сигналов, усилитель 8 положительных импульсов, предназначенный для формирования положительных импульсов напряжения в линии связи; усилитель 9 отрицательных импульсов,предназначенный для формирования в линии связи отрицательных импульсов напряжения; линию связи 10, усилитель 11 положительных импу льсов, для формирования поступивших с линиисвязи положительных сигналов; усилитель 12 отрицательных импульсов, для формирования поступивших с линии связи отрицательных импульсов; линию задержки 13, элемент ИЛИ 14, элементы И 15 и 16; счетчик 17, предназначенный для выработки строба, подаваемо- го на дешифратор после прохождения кодовой группы; регистр 18 сдвига для приема и хранения кодовс й группы, поступившей с линии связи; дешифратор 19 для расшифровки кода управляющего сигнала, хранимого на регистре 18, частотный коммутатор 20 для выработки сигнала, разрешающего выдачу через элементы И 15 и 16 информационных сиуналов, поступивших с линии связи 10, на выходы устройства. Цепи 21, 22 входы устройства, на которые подаются управляющие сигналы, подлежащие передаче по линии связи; на цепи 23 и 24 подаются информационные сигналы единица и нуль соответственно, которые необходимо передать по ли,ции связи; к цепям 25 и 26 подключены принятые информационные сигналы единица и нуль, к цепям 27 и 28 - пойключены принятые управляющие сигналы. Работа устройства в режиме передачи. Перед началом работы счетчики 4 и 17, регистры сдвига 5 и 18 и триг.гер 3 устанавливаются в состояние О (цепь установки на фиг.1 не показана). После этого можно начать передачу управляющих сигналов . Пусть управляющий сигнал приходИт на вход 21. Он вызывает на выходах блока памяти 7 определенную комбинацию установочных импульсов, соответствующую управляющему сигналу Число выходных шин п блока памяти 7 выбирается равным числу разрядов регистров сдвига 5 и 18. При этом количество входов устройства не должно превышать числа 2. Далее блок памяти 7 устанавливает в регистре сдвига 5 двоичный пойиционный код, где единица этого,

кода соответствует положительному импульсу в линии связи 10, а нуль отрицательному, После окончания импульса на цепи 21 он своим задним фронтом через элемент ИЛИ б устанавливает триггер 3 в состояние единицы, разрешая тем самым прохождение импульсов с генератора импульсов 1 на выход элемента И 2. Поступление импульсов на сдвиговой вход регистра сдвига 5 выдвигает записанный в него код на усилители положительных и отрицательных импульсов 8, 9, и таким образом каждый импульс сдвига вызывает формирование в линии связи 10 положительного или отрицательного импульса напряжения. После поступления п-го импульса счетчик 4 устанавливает себя к триггер 3 в нуль, тем самым запрещая прохождение импульсов на выход элемента И 2, Аналогич работает устройство и при передаче управляющих сигналов, поступающих на другие входы. Отличие заключается только в коде, устанавливаемом в регистре сдвига 5. Например, если число управляющих сигналов, подлежащих передаче, равно 8, то регистры сдвига 5, 18 должны быть трехразрядными, а счетчик 4 после 3-го импульса должен установить себя и триггер 3 в состояние нуль. При этом коды, соответствуквдие управляющим сигналами и устанавливаемые в регистре сдвига 5, могут принимать следующие значения: 000, 001, 010, 011, 100, 101, 110, 111. Если, например, в регистр сдвига был записан код 111, то после поступления сДйигающих импульсов по линии связи 10 пройдет кодовая группа из трех положительных импульсов напряжения, в отличие от управляющих сигналов информационные сигналы единица и нуль, поступающие соответственно на входы 23 и 24 устройства, а затем на передающие усилители 8 и 9, не преобразуются в кодовые группы и передаются по линии связи с максимально возможной для нее частотой. .

Работа устройства в режиме прием управляющих сигналов.

До Начала приема счетчик 17, регистр сдвига 18 установлены в нуль, а на шине 29 - запрещающий сигнал, который не дает возможности импульсам с усилителей 11 и 12 попасть на информационные выходы 25 и 26 устройства. Поступающие с линии связи 10 импульсы напряжения формируются усилителями 11 и 12 и поступают на сдвигающий вход регистра сдвига 18 и счетный вход счетчика 17 через элемент ИЛИ 14 Сдвиг кода в регистре 18 производится по заднему фронту приходящего импульса. Кроме этого, на информационный вход

сдвигового регистра 18 подается задержанный импульс с выхода усилителя, 11 положительных импульсов через линию задержки 13, Величина линии задержки выбирается такой, чтобы произошло надежное совпадение импульса на информационном входе и заднего фронта импульса на сдвигающем входе регистра сдвига 18. Таким образом обеспечивается запись импульсов, поступающих с линии связи 10

0 в регистр сдвига 18. После прихода п-го импульса счетчик 17 устанавливает себя в. нуль и вырабатывает стробирующий сигнал, который разрешает расшифровку дешифратором 19 кода,

5 установленного на регистре сдвига 18. При этом на одной из выходных шин дешифратора, соответствующий принятому управляющему сигналу, возникает импульс, который посту0пает на выход устройства.

Работа устройства в режиме приема информации.

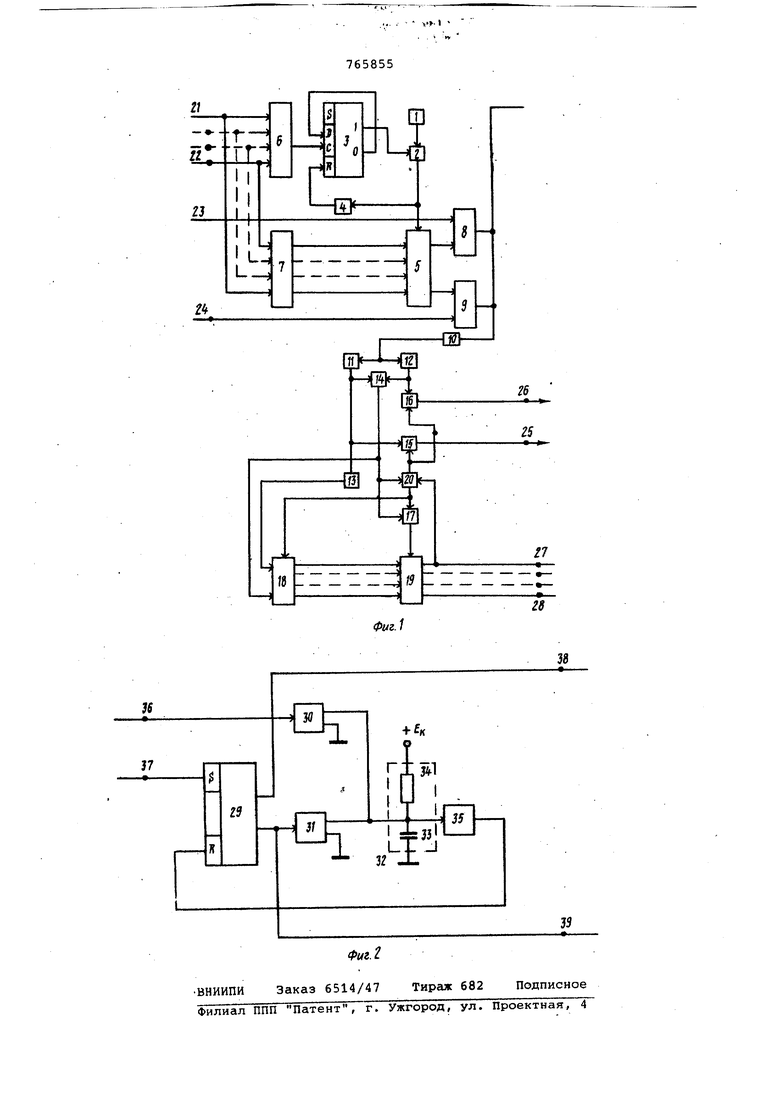

До этого с линии связи должен поступить управляющий сигнал, который означает, что после него бу5дут поступать информационные, сигналы Этот управляющий сигнал с выхода 27 дешифратора 19 поступает на установочный вход частотного коммутатора 20 и включает его. Рассмотрим бо0лее подробно работу частотного коммутатора. В состав частотного коммутатора входит триггер 29, управляемые ключи 30 и 31, времязадающая цепочка 32, состоящая из конденса5тора 33 и резистора 34, пороговый элемент 35. Кроме этого, цепь 36 частотный вход; цепь 37 - установочный вход; |Цепь 38 - выход триггера 29, (подключается к элементам И 15 и 16); цепь 39 - инверсный

0 выход триггера 29 (на фиг. 1 подключен ко входам установки в нуль . регистра сдвига 18 и счетчика 17) В исходном состоянии триггер 29 находится в состоянии нуль (запрещаю5щий сигнал на цепи 38 и разрещающий - на цепи 39) . Выход управляемого ключа 30 разомкнут, а выход Управляемого ключа 31 замкнут. Конденсатор 34 разряжен, а на вы0ходе порогового элемента 35 разрешающий сигнал.

Работает частотный коммутатор следующим образом. При поступлении импульса на установочный вход 37

5 триггер 29 устанавливается в единицу , па выходе 38 появляется разрешающий сигнал, на выходе 39-запрещающий, а выход управляемого ключа 31 размыкается. Конденсатор 33 начи0нает заряжаться до +Е через резистор 34. При достижении напряжения на конденсаторе 38 уровня срабатывания порогового элемента 35 на его выходе появляется сигнал, устанавливающий триггер 29 в нуль.

5

Однако это происходит только в том случае, если за время заряда конденсатора 38 до уровня срабатывания порогового элемента 35 на частотный вход 36 не поступил импуль Если же он поступил, то он открывает управляемый ключ 30, который разряжает конденсатор 33 до нуля. После прохождения импульса на входе 36 управляемый ключ 30 размыкается и конденсатор 33 снова начинает заряжаться. Этот.процесс в частотном коммутаторе продолжается до тех пор, пока на частотном входе 36 не появится временной интервал между импульсами, чем время заряда конденсатора 33 до напряжения срабатывания порогового .элемента 35. В этом случае, пороговый элемент 35 устанавливает триггер 29 в нуль управляемый ключ 31 замыкается и разряжает конденсатор 33, после чего на выходе порогового элемента 35 в цепи 39 устанавливается разрешающий сигнал, а в цепи 38 запрещающий . В предлагаемом устройств время заряда конденсатора до порога срабатывания элемента 35 выбирается менее длительности двух периодов следования импульсов в линии связи, но более одной длительности периода следования импульсов в линии связи. Следовательно, для нормальной работ устройства после завершения передачи информационных сигналов требуется пауза длительностью более одного периода следования импульсов в лини связи. Таким образом, после появления управляющего импульса на выходе 27 дешифратора 19, означающего, что следом за ним .будут поступать информационные сигналы, частотный коммутатор одним своим выходом разрешает прохождение информационных сигналов единица и нуль на соответствующие выходы 25 и 26 устройства, а другим удерживает счетчи 17 и регистр сдвига в состоянии нуль. После завершения передачи информационных сигналов частотный коммутатор переключится, на цепи 29 устанавливается запрещающий сигнал, сигнал установки в нуль регистра сдвига 18 и счетчика 17 снимается и устройство вновь может принимать управляющие сигналы

Внедрение изобретения позволяет значительно сократить время обмена меЯсду приборами АСУ. Произведем ориентировочный расчет сокращения времени обмена по сравнению с аналогом на примере идеологии обмена. Для организации обмена ОСТ 5.8346-7 рекомендует использовать щесть управляющих сигналов. Обмен дискретно двоичной информацией между приборами производится 34 разрядными словами. Из управляющих сигналов только два: Начало слова и Конец слова

выдаются в начале и конце каждого слова. Остальные управляющие сигналы могут использоваться только один раз за сеанс связи. Таким образом, подавляющее время сеанса связи используется на передачу информационных сигналов, и поэтому временем передачи управляющих сигналов можно пренебречь. Предположим, что за сеанс связи количество переданных информационных сигналов 1 и О одинаково

0 и равно К. В рассматриваемом аналоге на передачу информационного сигнала О затрачивается период следования одного импульса Т в линии связи, а на передачу информационного сигнала 5 1 затрачивается .два периода следования импульсов в линии связи 2т. В предлагаемом устройстве на передачу информационного сигнала 1 или О затрачивается одинаковое время, равное Т..

0

Таким образом, ориентировочное сокращение N времени обмена в процентах можно-посчитать по формуле .о, .2Т)-2КТ

-1007ь N 100% i3V/o,

Т7

КТ-ьК.2Т -

где T время, затрачиваемое на передачу К информационных сигналов О и К информационных, сигналов 1 в аналоге; Т - время, затрачиваемое на пе0редачу, 2К информационных сигналов 1 и ;0 в предлагаемом устройстве.

35

Формула изобретения

1. Устройство для передачи и приема сигналов, содержащее на передающей стороне -элемент ИЛИ, входы которого соединены со входами управляющих сигналов устройства, усилители, выходы которых соединены через линию связи со входами усилителей на приемной стороне, выходы которых

подключены к двум входам элемента ИЛИ, выход которого соединен со счетным входом счетчика, выход которого подключен к стробирующему входу дешифратора, выходы которого подключены

к выходам устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, в него введены на передающей стороне элемент И, счетчик, триггер, блок памяти, регистр сдвига, и генератор импульсов, который соединен с первым входом элемента И, второй вход которого подключен к первому выходу триггера, второй выход триггера соединен со своим первым входом, выход

элемента И подключен к первому входу регистра сдвига и ко входу счетчика, выход которого соединен со вторым входом триггера, третий вход которого подключен к выходу элемента ИЛИ, входы которого соединены ,

со входами блока памяти, выходы которого подключены к установочным входам регистра сдвига, выходы коно рого соединены с первыми входами, усилителей, вторые входы которых соединены с входами информационных сигналов устройства, на приемной стороне введены два элемента И, элемент задержки, регистр сдвига и частотный коммутатор, выход первого усилителя соединен со входом элемента задержки и.первым входо первого элемента И, выход второго услителя соединен, с первым входом второго элемента И, выход элемента задержки подключен к первому входу регистра сдвига, второй вход которого соединен с выходом элемента ИЛИ и первым входом частотного коммутатора, первый BbdkoflJ которого подключе к третьему входу регистра сдвига и входу установки нуля счетчика, выходы регистра сдвига соединены со входами дешифратора, один из выходов которого подключен ко второму входу частотного коммутатора, второй выход которого соединен со вторыми входами элементов И, выходы дешифратора и элементов И соединены с выходами устройства.

2i Устройство по п. 1, о т л и чающееся тем,- что Частотный коммутатор содержит триггер, ключи, элемент задержки, пороговый элемент и общую шину источника питания, первый вход триггера и вход первого ключа подключены соответственно к первым и вторым входам частотного коммутатора, первый выход триггера подключен к управляющему входу второго ключа, выходы ключей

О соединены с первым входом элемента задержки, выход которого подключен ко входу порогового элемента, выход которого соединен со вторым входом триггера, вторые выходы ключей и второй вход элемента задержки подключены к обшей шине источника питания, первый и второй выходы триггера соединены с выходами частотного коммутатора.

0 Источники информации,

принятые во внимание при экспертизе

1.Билик Р.В. и др. Бесконтактные элементы и системы телемеханики

с временным разделением сигналов. М., Наука, 1964, с. 340.

2.Авторское свидетельства СССР по заявке 2549459/18-24,

кл. С 08 С 19/28, 26.07.78.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи дискретной информации | 1978 |

|

SU769594A1 |

| Устройство передачи и приема дискретной информации | 1979 |

|

SU902296A1 |

| Устройство для задержки импульсов | 1986 |

|

SU1359896A1 |

| Устройство для регулирования скорости лентопротяжного механизма | 1988 |

|

SU1501002A1 |

| АКУСТИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕЩЕНИЙ | 1994 |

|

RU2099864C1 |

| АКУСТИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕЩЕНИЙ | 1994 |

|

RU2090840C1 |

| Адаптивный коммутатор системы телеизмерений | 1980 |

|

SU886032A1 |

| Устройство для передачи и приема информации | 1989 |

|

SU1656572A1 |

| Система контроля движения маршрутного транспорта | 1983 |

|

SU1138820A1 |

| Линия задержки на приборах с переносом заряда | 1989 |

|

SU1626334A1 |

Авторы

Даты

1980-09-23—Публикация

1978-10-20—Подача