Изобретение относится к импульсной технике и может найти применение в Устройствах управляемой временной задержки импульсных сигналов.

Целью изобретения является расширение функциональных возможностей за счет получения возможности управления временем задержки и расширение диапазона времени задержки

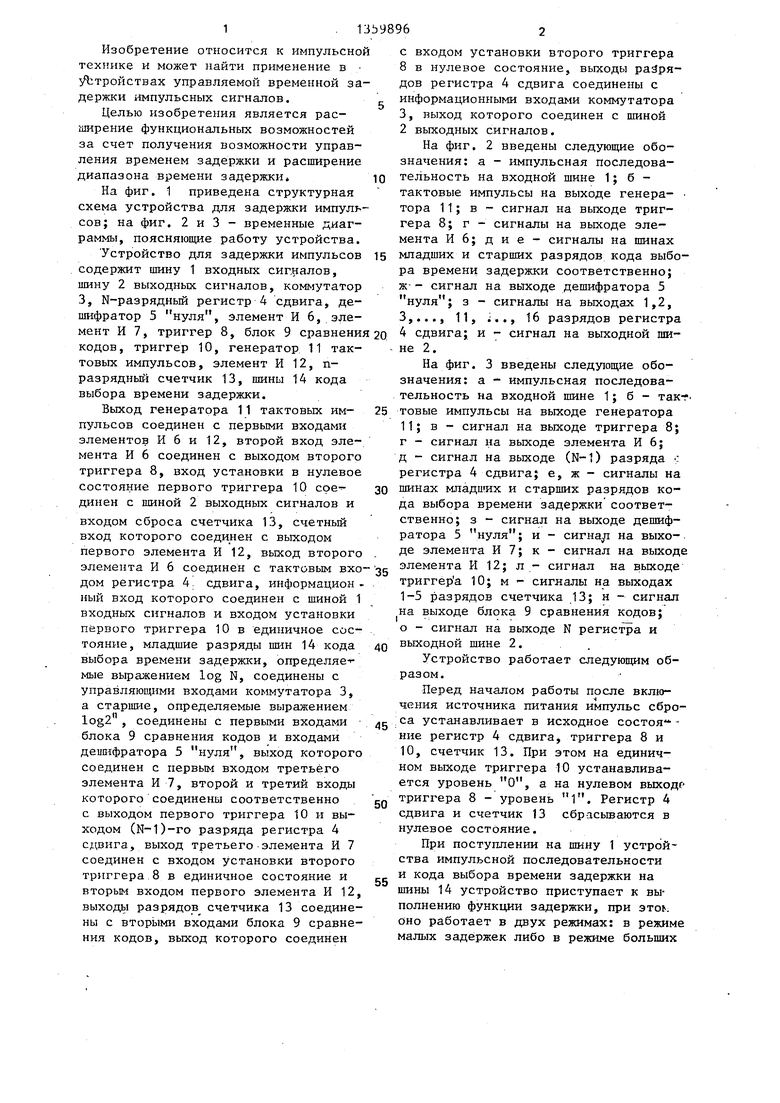

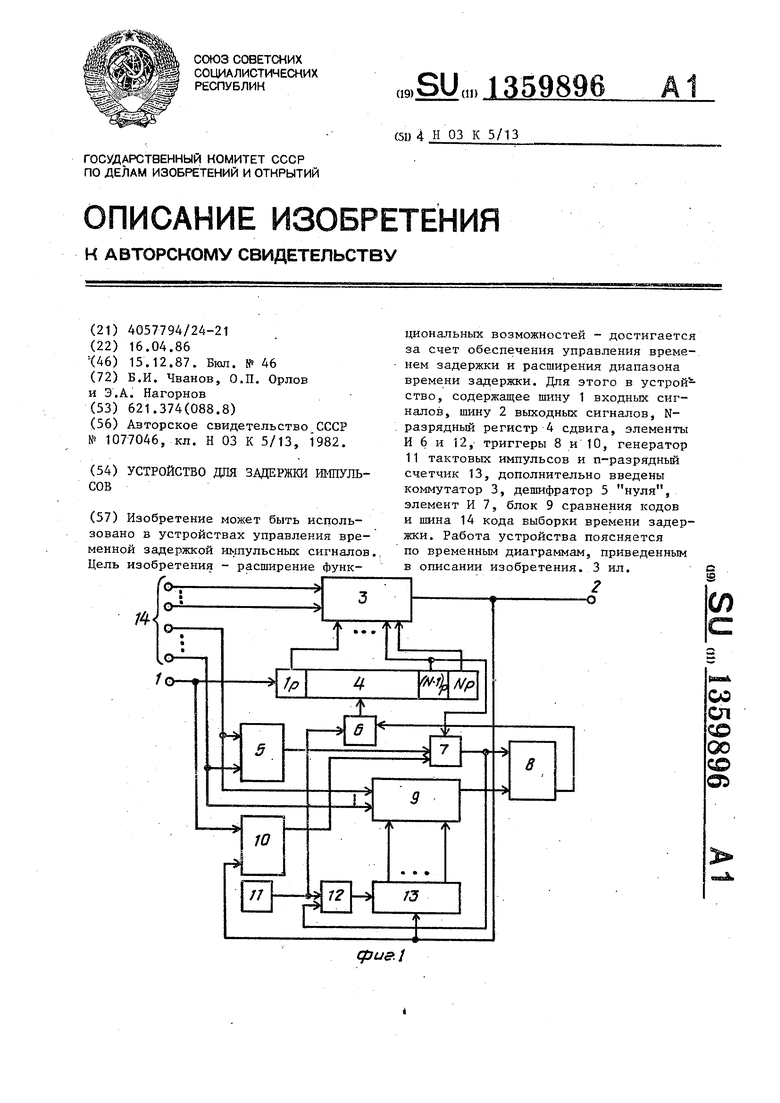

На фиг, 1 приведена структурная схема устройства для задержки импульсов; на фиг, 2 и 3 - временные диаграммы, поясняющие работу устройства.

Устройство для задержки импульсов содержит шину 1 входных сигналов, шину 2 выходных сигналов, коммутатор 3, N-pазрядный регистр 4 сдвига, дешифратор 5 нуля, элемент И 6, элемент И 7, триггер 8, блок 9 сравнения кодов, триггер 10, генератор 11 тактовых импульсов, элемент И 12, п- разрядньй счетчик 13, шины 14 кода выбора времени задержки.

Выход генератора 11 тактовых им- пульсов соединен с первьши входами элементов И 6 и 12, второй вход элемента И 6 соединен с выходом второго триггера 8, вход установки в нулевое состояние первого триггера 10 сре- динен с шиной 2 выходных сигналов и

входом сброса счетчика 13, счетный вход которого соединен с выходом первого элемента И 12, выход второго элемента И 6 соединен с тактовым вхо дом регистра 4. сдвига, информационный вход которого соединен с шиной 1 входных сигналов и входом установки первого триггера 10 в единичное состояние, младшие разряды шин 14 кода выбора времени задержки, определяе- мые выражением log N, соединены с управляющими входами коммутатора 3, а старшие, определяемые выражением Iog2, соединены с первыми входами блока 9 сравнения кодов и входами деишфратора 5 нуля, выход которого соединен с первым входом третьего элемента И 7, второй и третий входы которого соединены соответственно с выходом первого триггера 10 и выходом (N-l)-ro разряда регистра 4 сдвига, выход третьего-элемента И 7 соединен с входом установки второго триггера 8 в единичное состояние и вторым входом первого элемента И 12, выходь разрядов счетчика 13 соединены с вторыми входами блока 9 сравнения кодов, выход которого соединен

с входом установки второго триггера 8 в нулевое состояние, выходы райря- дов регистра 4 сдвига соединены с информационными входами коммутатора 3, выход которого соединен с шиной 2 выходных сигналов,

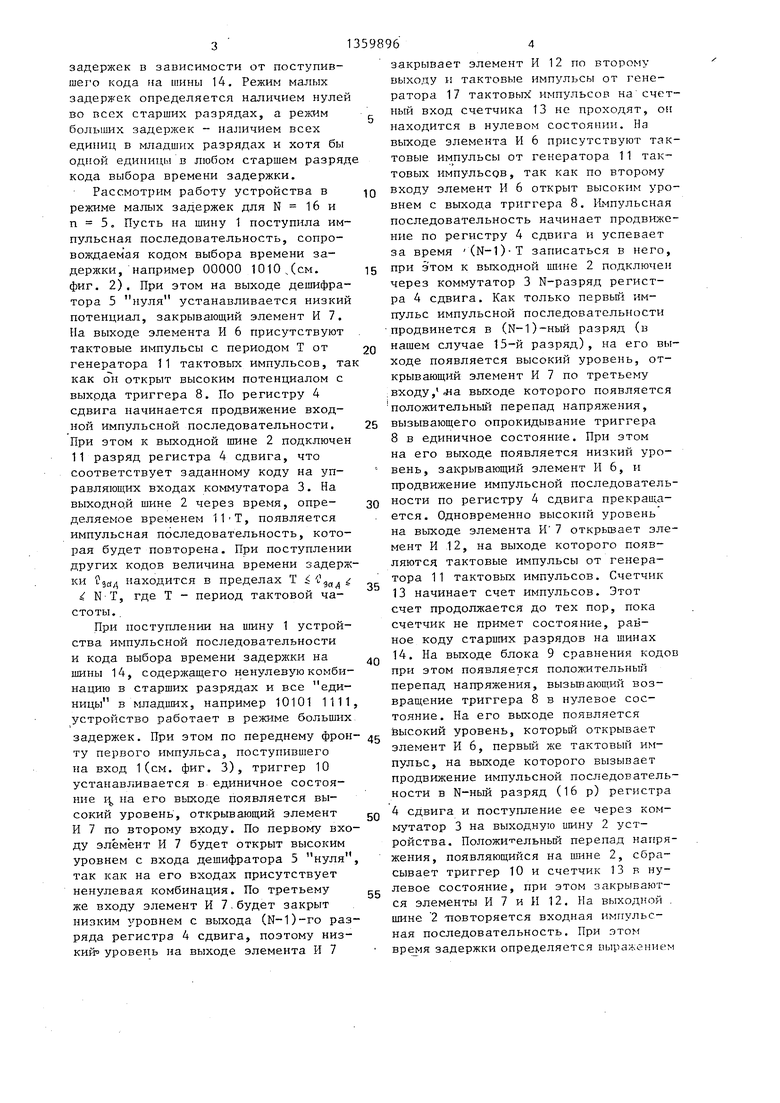

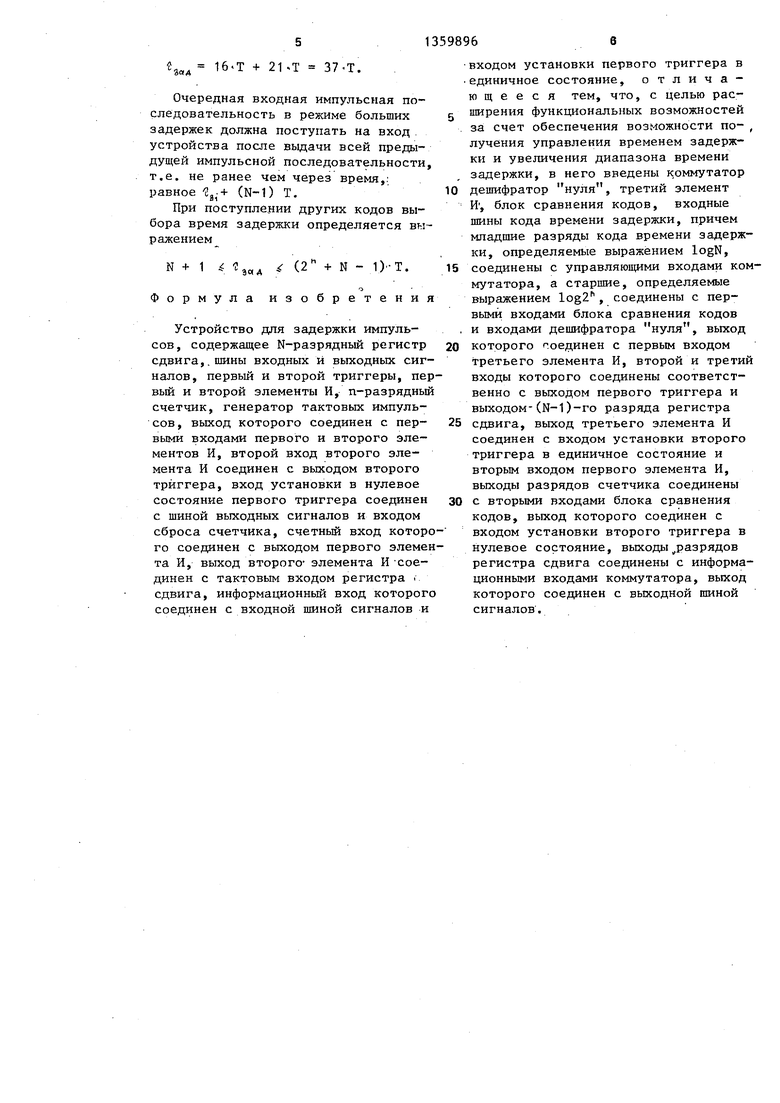

На фиг, 2 введены следующие обозначения; а - импульсная последовательность на входной шине 1; б - тактовые импульсы на выходе генера- тора 11; в - сигнал на выходе триггера 8; г - сигналы на выходе элемента И 6; д и е - сигналы на шинах младших и старших разрядов кода выбора времени задержки соответственно; ж- - сигнал на выходе дешифратора 5 3 - сигналы на выходах 1,2, 3,,,,, 11, ;,,, 16 разрядов регистра 4 сдвига; и - сигнал на выходной шине 2,

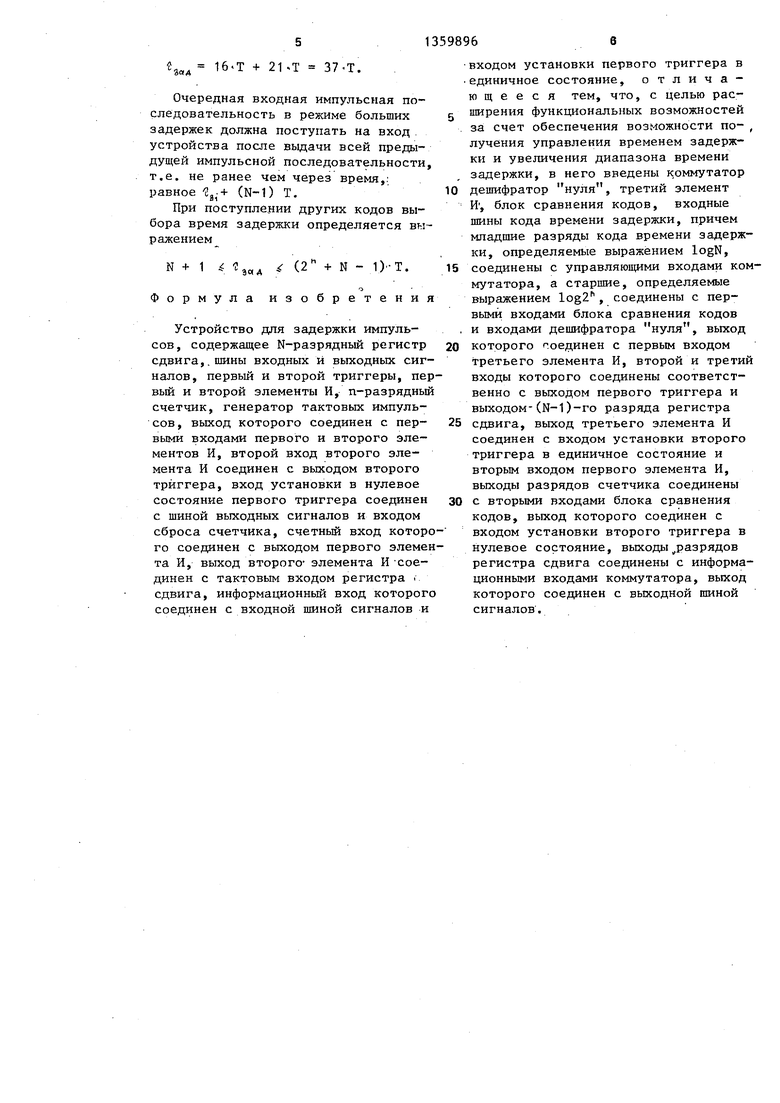

На фиг, 3 введены следующие обозначения: а - импульсная последовательность на входной шине 1; б - так товые импульсы на выходе генератора 11; в - сигнал на выходе триггера В; г - сигнал на выходе элемента И 6; д - сигнал на выходе (N-1) разряда : регистра 4 сдвига; е, ж - сигналы на шинах младших и старших разрядов кода выбора времени задержки соответственно; 3 - сигнал на выходе дешифратора 5 и - сигна/1 на выходе элемента И 7; к - сигнал на выход элемента И 12; л - сигнал на вькоде триггер а 10; м - сигналы на выходах 1-5 разрядов счетчика 13; и - сигнал на выходе блока 9 сравнения кодов; о - сигнал на выходе N регистра и выходной шине 2,

Устройство работает следующим образом.

Перед началом работы после включения источника питания импульс сброса устанавливает в исходное состоя - ние регистр 4 сдвига, триггера 8 и 10, счетчик 13, При этом на единичном выходе триггера 10 устанавливается уровень О, а на нулевом ВЫХОД триггера 8 - уровень 1, Регистр 4 сдвига и счетчик 13 сбрасьшаются в нулевое состояние.

При поступлении на шину 1 устройства импульсной последовательности и кода выбора времени задержки на шины 14 устройство приступает к выполнению функции задержки, при STOh. оно работает в двух режимах: в режим малых задержек либо в режиме больших

задержек в зависимости от поступившего кода па пшпы 14. Режим малых задержек определяется наличием нулей во всех старших разрядах, а режим больших задержек - наличием всех единиц в младших разрядах и хотя бы одной единицы в любом старшем разряд кода выбора времени задержки.

Рассмотрим работу устройства в режиме малых задержек для N 16 и п 5, Пусть на шину 1 поступила импульсная последовательность, сопровождаемая кодом выбора времени задержки, например 00000 1010,(см. фиг. 2). При этом на выходе дешифратора 5 нуля устанавливается низкий потенциал, закрывающий элемент И 7. На выходе элемента И 6 присутствуют тактовые импульсы с периодом Т от генератора 11 тактовых импульсов, та как он открыт высоким потенциалом с выхрда триггера 8. По регистру 4 сдвига начинается продвижение входной импульсной последовательности. При этом к выходной шине 2 подключен 11 разряд регистра 4 сдвига, что соответствует заданному коду на уп- равляюш;их входах коммутатора 3. На выходно,й шине 2 через время, определяемое временем 11 Т, появляется импульсная последовательность, которая будет повторена. При поступлении других кодов величина времени задержки находится в пределах Т ,

NT, где Т - период тактовой частоты.

При поступлении на шину 1 устройства импульсной последовательности и кода выбора времени задержки на шины 14, содержаш,его ненулевую комбинацию в старших разрядах и все единицы в младших, например 10101 1111 устройство работает в режиме больших

задержек. При этом по переднему фрон- 45 гсокий уровень, который открывает

элемент И 6, первьш же тактовый имту первого импульса, поступившего на вход 1(см. фиг. 3), триггер 10 устанавливается в единичное состояние i-j, на его выходе появляется высокий уровень, открывающий элемент И 7 по второму входу. По первому входу элемент И 7 будет открыт высоким уровнем с входа дешифратора 5 нуля, так как на его входах присутствует ненулевая комбинация. По третьему же входу элемент И 7.будет закрыт низким уровнем с выхода (N-l)-ro разряда регистра 4 сдвига, поэтому низ- кий уровень на выходе элемента И 7

50

55

пульс, на выходе которого вызывает продвижение импульсной последователь ности в N-ный разряд (16 р) регистра 4 сдвига и поступление ее через ком- гутатор 3 на выходную шину 2 устройства. Положи т ельный перепад напря жения, появляющийся на шине 2, сбрасывает триггер 10 и счетчик 13 в нулевое состояние, при этом закрываются элементы И 7 и И 12. На выходной шине 2 тювторяется входная импульсная последовательность. При этом время задержки определяется выражением

3598964

закрывает элемент И 12 по второму выходу и тактовые импульсы от генератора 17 тактовых импульсов на счетный вход счетчика 13 не проходят, он находится в нулевом состоянии. На выходе элемента И 6 присутствуют тактовые импульсы от генератора 11 тактовых импульсов, так как по второму Q входу элемент И 6 открыт высоким уровнем с выхода триггера 8. -1мпульсная последовательность начинает продвижение по регистру 4 сдвига и успевает за время (N-l)-T записаться в него, при этом к выходной шине 2 подключен через коммутатор 3 N-разряд регистра 4 сдвига. Как только первьш импульс импульсной последовательности продвинется в (Н-1)-ный разряд (в нашем случае 15-й разряд), на его выходе появляется высокий уровень, открывающий элемент И 7 по третьему ;Входу, ла выходе которого появляется положительный перепад напряжения, 25 вызывающего опрокидывание триггера 8 в единичное состояние. При этом на его выходе появляется низкий уро15

20

0

5

0

вень, закрывающий элемент И 6, и продвижение импульсной последовательности по регистру 4 сдвига прекращается. Одновременно высокий уровень на выходе элемента И 7 открьшает элемент И ,12, на выходе которого появляются тактовые импульсы от генератора 11 тактовых импульсов. Счетчик 13 начинает счет импульсов. Этот счет продолжается до тех пор, пока счетчик не примет состояние, равное коду старших разрядов на шинах 14. На выходе блока 9 сравнения кодов при этом появляется положительньп перепад напряжения, вызьшающий возвращение триггера 8 в нулевое состояние. На его выходе появляется

0

5

пульс, на выходе которого вызывает продвижение импульсной последовательности в N-ный разряд (16 р) регистра 4 сдвига и поступление ее через ком- гутатор 3 на выходную шину 2 устройства. Положи т ельный перепад напряжения, появляющийся на шине 2, сбрасывает триггер 10 и счетчик 13 в нулевое состояние, при этом закрываются элементы И 7 и И 12. На выходной , шине 2 тювторяется входная импульсная последовательность. При этом время задержки определяется выражением

«д 16.Т +

2ЬТ 37-Т.

Очередная входная импульсная последовательность в режиме больших задержек должна поступать на вход . устройства после выдачи всей предыдущей импульсной последовательности, т.е. не ранее чем через время,; равное 33.+ (N-1) Т.

При поступлении других кодов выбора время задержки определяется выражением

N + 1 - э«д , (2 + N - .

о

Формула изобретени

я

Устройство для задержки импульсов, содержащее N-разрядный регистр сдвига,, шины входных и выходных сигналов, первый и второй триггеры, первый и второй элементы И, п-разрядный счетчик, генератор тактовых импульсов, выход которого соединен с первыми входами первого и второго элементов И, второй вход второго элемента И соединен с выходом второго триггера, вход установки в нулевое состояние первого триггера соединен с шиной выходных сигналов и входом сброса счетчика, счетный вход которого соединен с выходом первого элемента И, выход второго- элемента И -соединен с тактовьш входом регистра сдвига, информационный вход которого соединен с входной шиной сигналов и

входом установки первого триггера в единичное состояние, отличающееся тем, что, с целью расс Етирения функциональных возможностей за счет обеспечения возможности по- , лучения управления временем задержки и увеличения диапазона времени задержки, в него введены коммутатор

10 дешифратор нуля, третий элемент И , блок сравнения кодов, входные шины кода времени задержки, причем мпадшие разряды кода времени задержки, определяемые выражением logN,

15 соединены с управляющими входами коммутатора, а старшие, определяемые выражением logZ, соединены с первыми входами блока сравнения кодов . и входами дешифратора нуля, выход

20 которого соединен с первым входом третьего элемента И, второй и третий входы которого соединены соответственно с выходом первого триггера и выходом-(N-1)-го разряда регистра

25 сдвига, выход третьего элемента И соединен с входом установки второго триггера в единичное состояние и вторым входом первого элемента И, выходы разрядов счетчика соединены

30 с вторыми входами блока сравнения кодов, выход которого соединен с входом установки второго триггера в нулевое состояние, выходы разрядов регистра сдвига соединены с информационными входами коммутатора, выход которого соединен с выходной шиной сигналов.

tjmifl-/

,

7)max fsr

j):r

M

IIIIIIIIIIIHIIIIHIHIIIlllllllMllll

Ш

iiiiiiiiiiiiiii

iiiiiiiiiiiiii

a- лгиишлллшшЛЛ П-П-П1JIL

-TjL

фиг г

Редактор A. Долинич

Составитель A. Титов Техред Л.Сердюкова

Заказ 6163/55 Тираж 900Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д . А/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

(pue.J

Корректор Н.Король

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для дискретной регулировки фазы | 1987 |

|

SU1450079A1 |

| Комбинированное устройство временной задержки и формирования импульсов | 1987 |

|

SU1443151A1 |

| Генератор псевдослучайной М-последовательности | 1985 |

|

SU1264317A2 |

| Устройство для умножения двоичных чисел | 1980 |

|

SU981996A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1992 |

|

RU2012014C1 |

| Устройство для сопряжения микроЭВМ с внешним устройством | 1985 |

|

SU1283780A1 |

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

| Устройство для формирования импульсных последовательностей | 1990 |

|

SU1758845A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 2000 |

|

RU2170444C1 |

| Синтезатор интервалов времени | 1986 |

|

SU1406558A1 |

Изобретение может быть использовано в устройствах управления временной задержкой икшульсных сигналов. Цель изобретения - расширение функциональных возможностей - достигается за счет обеспечения управления временем задержки и расвшрения диапазона времени задержки. Для этого в устройство, содержащее шину 1 входных сигналов, шину 2 выходных сигналов, N- разрядный регистр 4 сдвига, элементы И 6 и 12, триггеры 8 и 10, генератор 11 тактовых импульсов и п-разрядный счетчик 13, дополнительно введены коммутатор 3, дешифратор 5 нуля, элемент И 7, блок 9 сравнения кодов и шина 14 кода выборки времени задержки. Работа устройства поясняется по временным диаграммам, приведенным в описании изобретения. 3 ил. со СП 00 со 35 фигЛ

| Устройство для задержки импульсов | 1982 |

|

SU1077046A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-12-15—Публикация

1986-04-16—Подача