Изобретение относится к области вычислительной техники и может быть использовацо для анализа фазовых погрешностей решения на вычислительных, системах задач, описываемых системами обыкновенных дифференциальных уравнений.

Известно устройство для гармонического анализа, содержащее щифро-аналоговый гетербдин, щифровой блок изменения фазы, блок перемножения, блок выделения постоянной составляющей и экстремальный блак, причем вход гетеродина соединен с выходом блока изменения фазы, а выход - с первым входом блока перемножения, второй вход которого соединен с выходом исследуемого устройства. Выход блока /перемножения заведен на вход |блока выделения постоянной составляющей, выход которого соединен со входом экстремального блока. ВходОМ у|Стройства является второй вход блока перемножения, а выходом - выход экстремального блока I.

OcHOiBHHM недостатком данного устройства является итеративность процесса измерения фазы из-за пошаговогозадания юода фазы в счетчике цифро-аналогового преобразователя и блока изменения фазы, что приводит к значительным временным затратам при однократном измерении фазы исследуемого сигнала.

Наиболее близким по технической сущности к предлагаемому устройству является устройство для оценки точности работы операционных усилителей, содержащее гармонический осциллятор, блок сравнения, цифровой блок управления и обработки, блок цифро-аналоговых преобразователей, цифро-аналоговый преобразователь, блок коммутации, два масштабных блока и блок управления осциллятором, причем выходы цифрового блока управления и обработки соответственно соединены со входом блока цифро-аналоговых преобразователей, со входом -цифро-аналогового преобразователя, со входом блока коммутации, выход блока дифро-аналоговых преобразователей соединен со входом первого масштабного блока, выход цифро-аналогового преобразователя соединен с одним из входов блока

20 сравнения, (выход первого масштабного блока соединен со входом блока коммутации, входы и выходы блока жом мутащии соответственно соединены со входами и выходами контролируемого блока операционных усилителей,Тармонического осциллятора, блока управления осциллятором, кроме того, выход блока коммутации соединен со входом второго масштабного блока, выход которого соединен со вторым входом блока

30 сравнения, а выход блока сравнения соединен со входом щифрового блока |упраВления II обработки 2.

К недостат.кзм данного устройства следует отнести, во-первых, несабходимость дояолнительных расчетов при определении фазовой погрешности, учитывающих фазовые погрешности вталонных усил41телей гармонического, Ооциллято.ра. Во-вторых, для оцеНКИ фазовой погрешности на данном устройстве необходимо в качестве эталонного иметь операционный усилитель пли вычислительное устройство, идентичное проверяемому. iKpoMe того, отсутствует возможность анализа погрешностей за мкнутого вычислительного контура, в частности аналого-цифрового, так 1как проверяются лишь отдельные операционные Элементы.

Целью изобретения является расширение класса .решаемых задач и павышение быстродействия при измерении фазовых погрешностей вычислительных систем (устройств).

Для достижения поставленной цели в устройство, содержащее генератор гармонических колебаний, вход которого Я1вляется входом запуска устройства, введены два комларатора, суммируюший счетчик,, два элемента ИЛИ, элемент И, генератор тактовых импульсов, блок индикации, триггер, формирователь импульса сброса, выход генератора тактовых импульсов соединен с первым входом Элемента И, выход которого подключен ко входу суммирующего счетчика, 1ВЫХОД которого соединен со входом блока индика1ции, выхо(д первого элемента ИЛИ подключен к счетному входу триггера, выход которого соединен со вторым входом элемента И, выход формирователя импульса сброса подключен ко входу сброса триггера и к первому вхоДу второго элемента ИЛИ, выход которого соединен со входом сброса суммирующего счетчика, второй вход второго элемента ИЛИ, объединен со входом генератора гармонических колебаний, выход которого подключен ко входу первого компаратора, выход которого подключен к первому входу первого элемента ИЛИ, второй вход которого соединен с аыходом второго комларатора, вход которого является входом устройства.

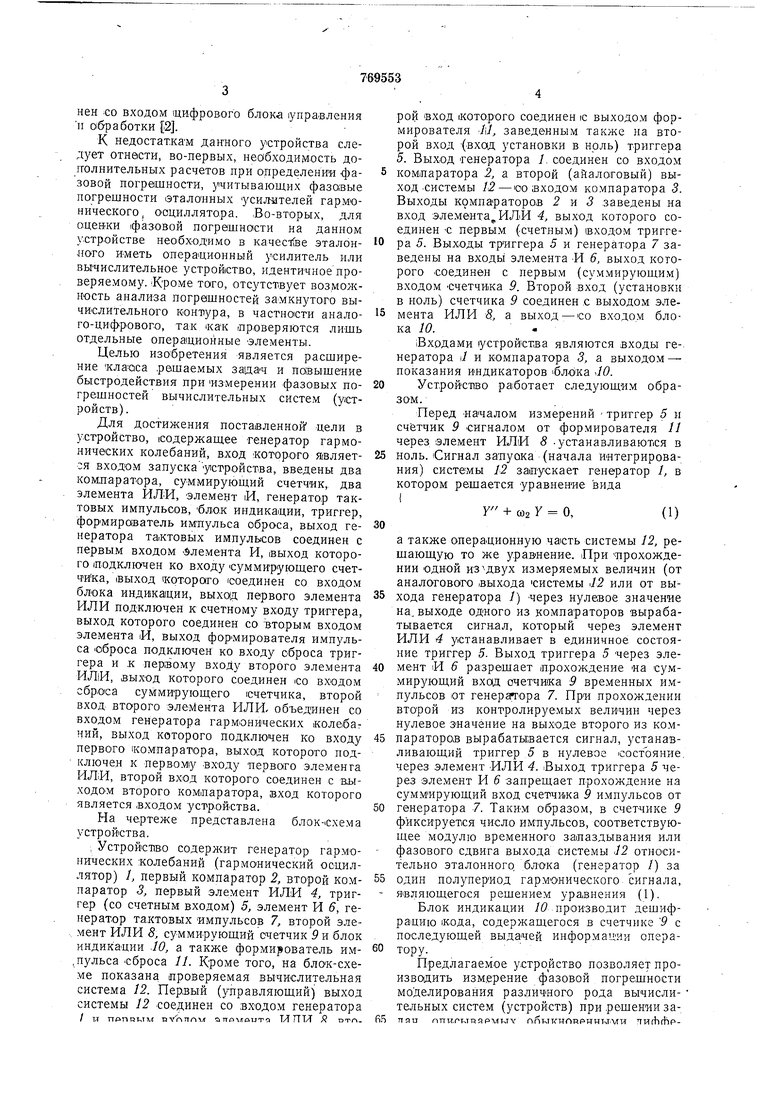

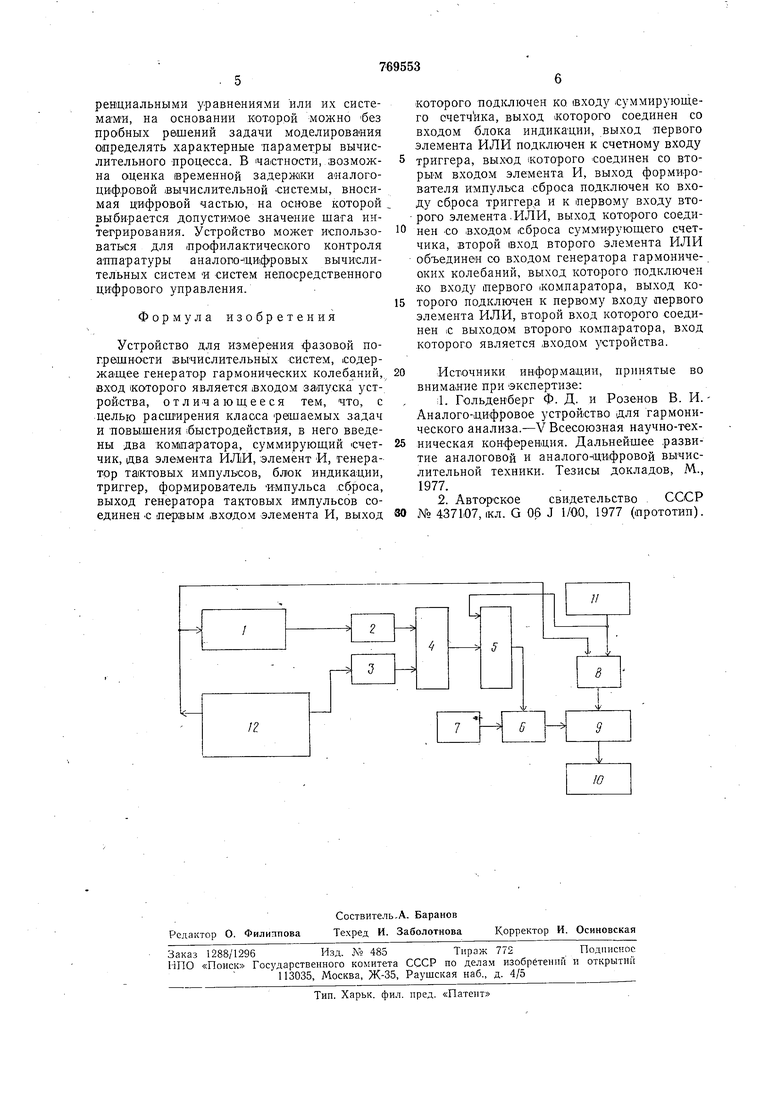

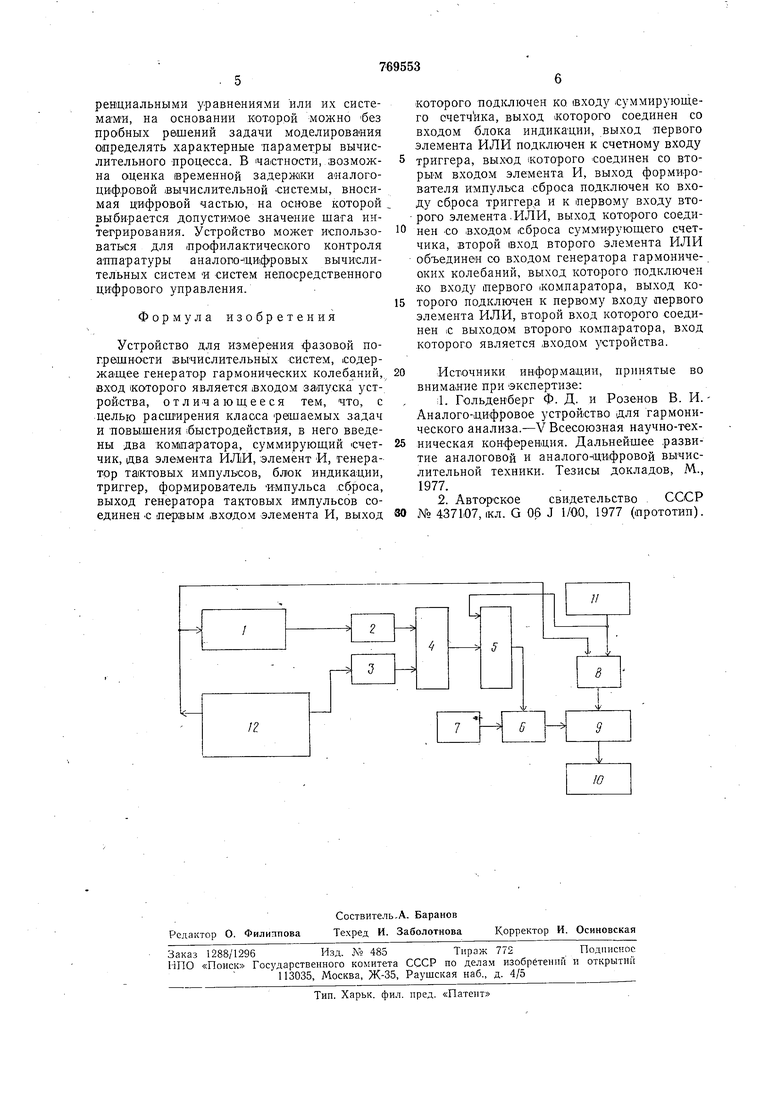

Иа чертеже представлена блок-схема устройства.

; Устройст1во содержит генератор гармонических колебаний (гармонический осциллятор) /, первый компаратор 2, второй компаратор 3, первый элемент ИЛИ 4, триггер (со счетным входом) 5, элемент И 6, генератор тактовых импульсов 7, второй эле, мент ИЛИ 8, суммирующий счетчик 9 и блок индикации .10, а также формирователь им, пульса сброса //. Кроме того, на блок-схеме показана, проверяемая вычислительная система 12. Первый (управляющий) выход системы 12 соединен со входом генератора

/ м nfinuMAJ пуплАл/г ололлоита ТЛ ЯТЛ л отп.

рой вход (Которого соединен с выходом формирователя 111, заведенным также на второй вход -(вход установки в ноль) триггера 5. Выход генератора 1. соединен со входом комларатора 2, а второй (айалоговый) выход системы 12 -100 входом компаратора 3. Выходы компараторов 2 и 3 заведены на вход элемента ИЛИ 4, выход которого соединен с первым (счетным) входом триггера 5. Выходы триггера 5 и генератор.а 7 заведены на входь элемента И 6, выход которого соединен с первым (суммирующим) входом счетчика 9. Второй вход (установки в ноль) счетчика 9 соединен .с выходом элемента ИЛИ 8., а выход - со входом блока /Л

(Входами 1устроЙ1ства являются входы ге-. нератора i/ и компаратора 3, а выходом - показания индикаторов блока JO.

УстройСТ1во работает следующим обраЗОМ.

Перед -началом измерений триггер 5 и счЬтчик 9 сигналом от формирователя // через элемент ИЛИ 8 -устанавливаются в ноль. Сигнал запуска (начала Интегрирования) системы 12 запускает генератор Д в котором решается -уравнение вида

(1)

Y -)- сй2 F О,

а также операционную часть системы 12, решающую то же уравнение. При -шрохождении одной издвух измеряемых величин (от аналогового выхода системы ./2 или от выхода генератора /) через нулевое значение на. выходе одного из компараторов вырабатывается сигнал, который через элемент ИЛИ 4 устанавливает в единичное состояние триггер 5. Выход триггера 5 через элемент И 6 разрешает прохождение на суммирзющий вход счетчика 9 вре.менных импульсов от генерат-ора 7. При прохождении второй из контролируемых величин через нулевое значение на выходе второго из компараторов вырабатывается сигнал, устанавливающий триггер 5 в нулевое состояние, через элемент ИЛИ 4. Выход триггера 5 через элемент И 6 запрещает прохождение на суммирующий вход счетчнка 9 импульсов от

генератора 7. Таким образом, в счетчике 9 фиксируется число импульсов, соответствующее мод)лю временного запаздывания или фазового сдвига выхода системы 12 относительно эталонного, блока (генератор /) за

один полупериод гармонического сигнала, являющегося решением уравнения (1).

Блок индикадии /О производит дешифрацию жода, содержащегося в счетчике 9 с последующей выдачей информации оператору.

Предлагаемое устройство позволяет производить измерение фазовой погрешности моделирования различного рода вычислительных систем (устройств) при решении заляп ппи.пыпярикту п.быкнпкрннкьии TWthrhpренциальными уравнениями или их системаМи, на основании которой можно -без пробных решений задачи моделировайня определять характерные параметры вычислительного процесса. В частности, возможна оценка временной задерж1ки аналогоцифровой 1вычислительной .системы, вносимая цифровой частью, на основе которой выбирается допустимое значение шага интегрирования. Устройство может использоваться для .профилактического контроля аппаратуры аналого-щифровых вычислительных систем И систем непосредственного цифрового управления.

Формула изобретения

Устройство для измерения фазовой погрешности вычислительных систем, содержащее генератор гармонических колебаний, вход iKoooporo является ;входом запуска устройства, отличаюш;ееся тем, что, с целью расширения класса решаемых задач и повышения 1быстродействия, в него введены два компаратора, суммирующий счетчик, два элемента ИЛИ, элемент И, генератор тактовых импульсов, блок индикации, триггер, формирователь импульса сброса, выход генератора тактовых импульсов соединен с лервым «входом элемента И, выход

которого подключен ко входу суммирующего счетчика, выход которого соединен со входом блока индикации, выход первого элемента ИЛИ подключен к счетному входу

триггера, выход которого соединен со вторьш входом элемента И, выход формирователя импульса сброса подключен ко входу сброса триггера и к первому входу второго элемента .ИЛИ, выход которого соединей со входом сброса суммирующего счетчика, второй вход второго элемента ИЛИ объединен со входом генератора гармонических колебаний, выход которого подключен ко входу первого компаратора, выход которого подключен к первому входу первого элемента ИЛИ, второй вход которого соединен с выходом второго компа-ратора, вход которого является входом устройства.

Источники информации, принятые во внимание при экспертизе:

:1. Гольденберг Ф. Д. и Розенов В. И. Аналого-цифровое устройство для гармонического анализа.-V Всесоюзная научно-техническая конференция. Дальнейшее развитие аналоговой и аналого-(цифровой вычислительной техники. Тезисы докладов, М., 1977.

2. Авторское свидетельство СССР

№ 4371,07, кл. G 06 J 1/0-0, 1977 (.прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления частной производной | 1983 |

|

SU1105913A1 |

| Устройство подавления помех | 1988 |

|

SU1578814A1 |

| Стабилизатор переменного напряжения | 1988 |

|

SU1534434A1 |

| Устройство для определения моментов экстремумов гармонических сигналов | 1981 |

|

SU1004899A1 |

| Устройство для измерения напряженности поля коллапса цилиндрических магнитных доменов | 1985 |

|

SU1275541A1 |

| СПОСОБ ИЗМЕРЕНИЯ УГЛА ПОВОРОТА ВАЛА | 1993 |

|

RU2107390C1 |

| УСТРОЙСТВО КОРРЕКЦИИ ФОРМЫ КРИВОЙ НАПРЯЖЕНИЯ | 2014 |

|

RU2580944C1 |

| Вихретоковый дефектоскоп | 1983 |

|

SU1103141A1 |

| Устройство для считывания графической информации | 1980 |

|

SU883937A1 |

| Устройство для считывания графической информации | 1982 |

|

SU1043692A1 |

Авторы

Даты

1980-10-07—Публикация

1978-12-20—Подача