Изобретение относится к радиотехнике и может найти применение в устройствах обработки дискретных сигналов.

Цель изобретения - повышение эффективности подавления.

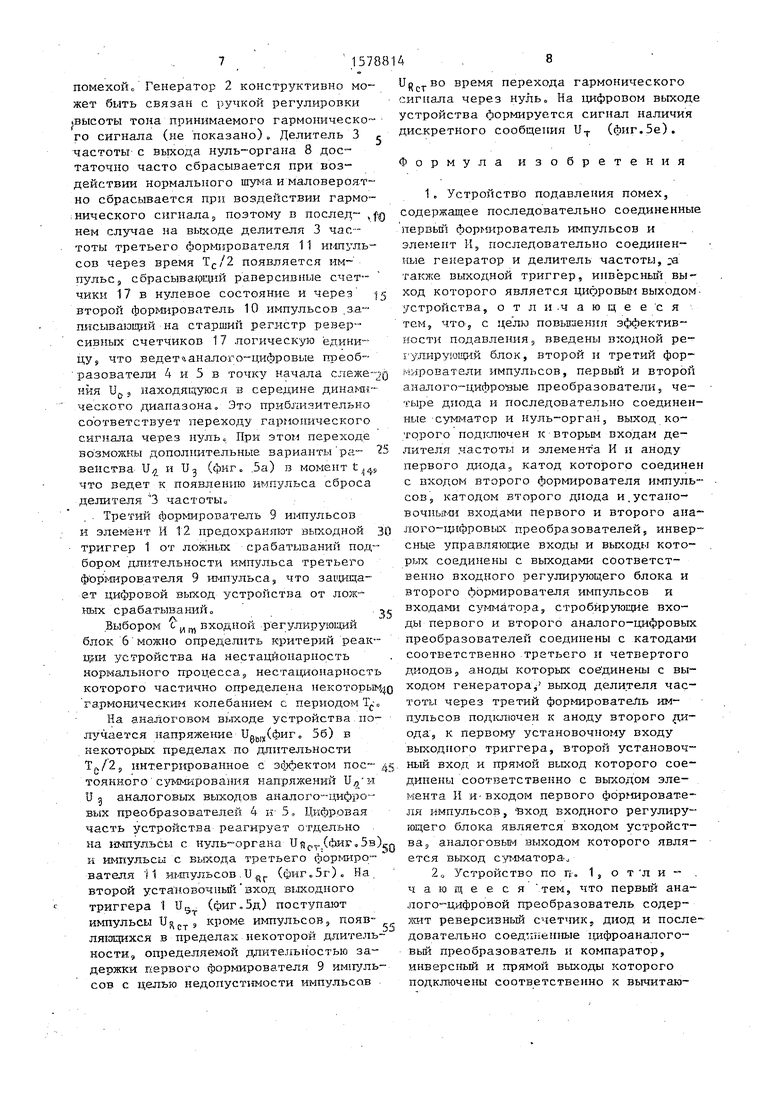

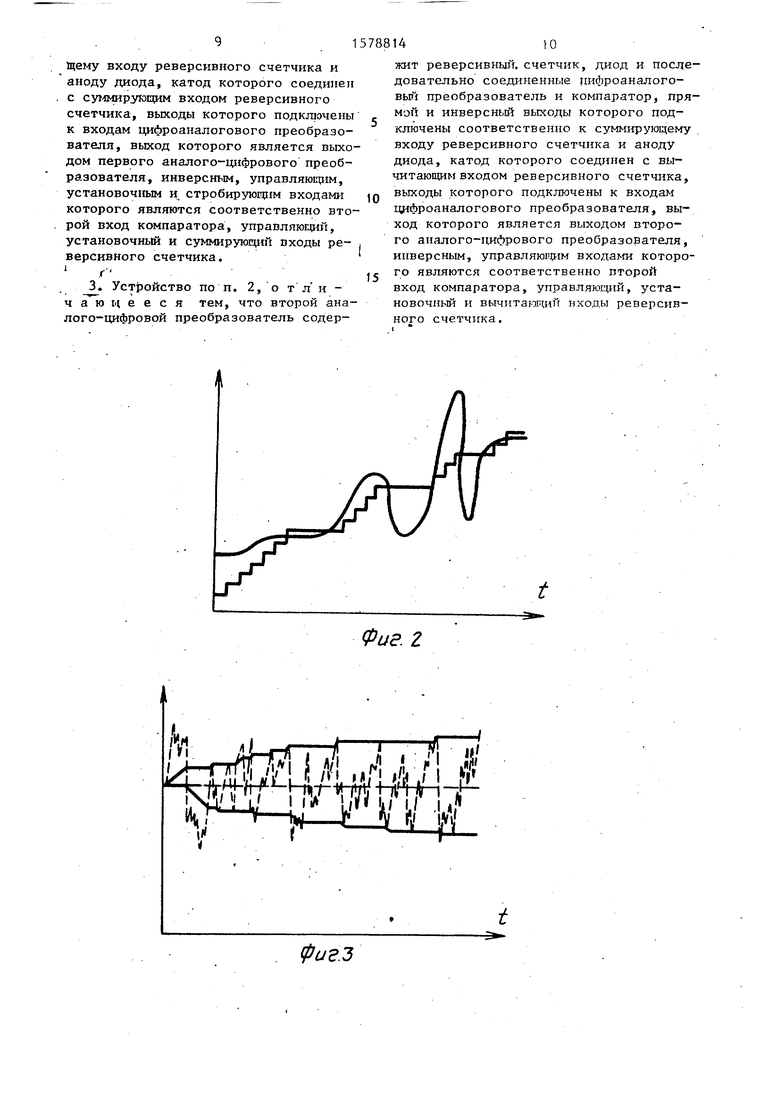

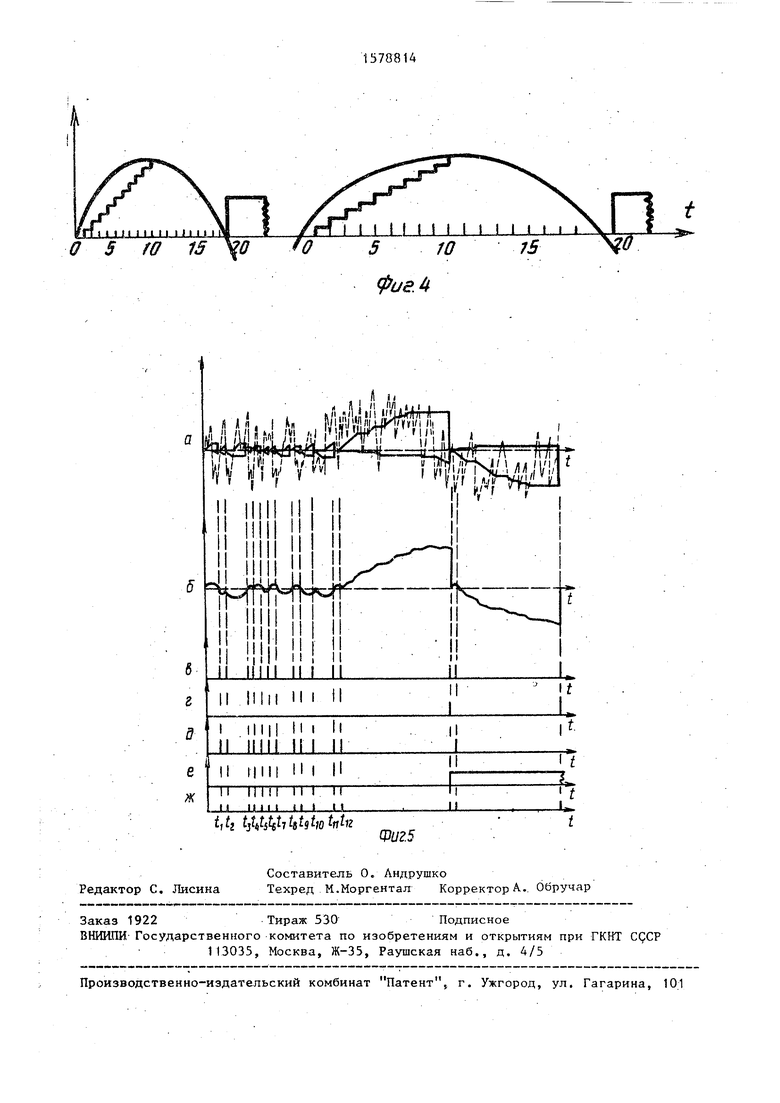

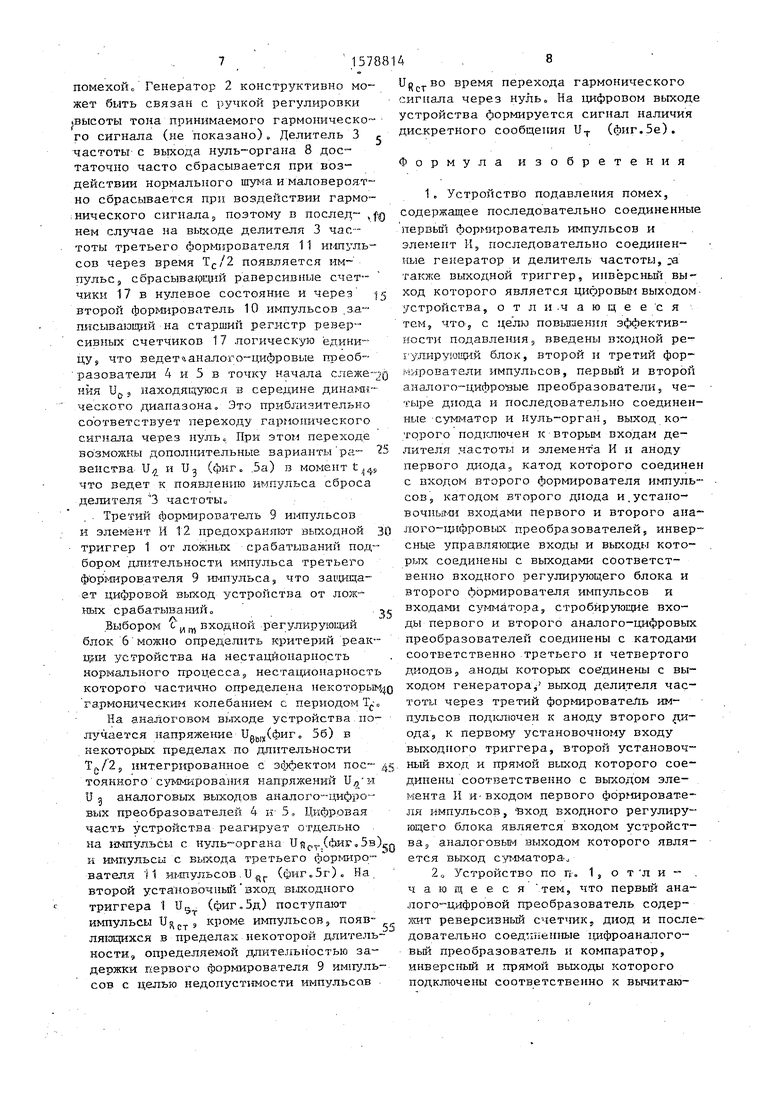

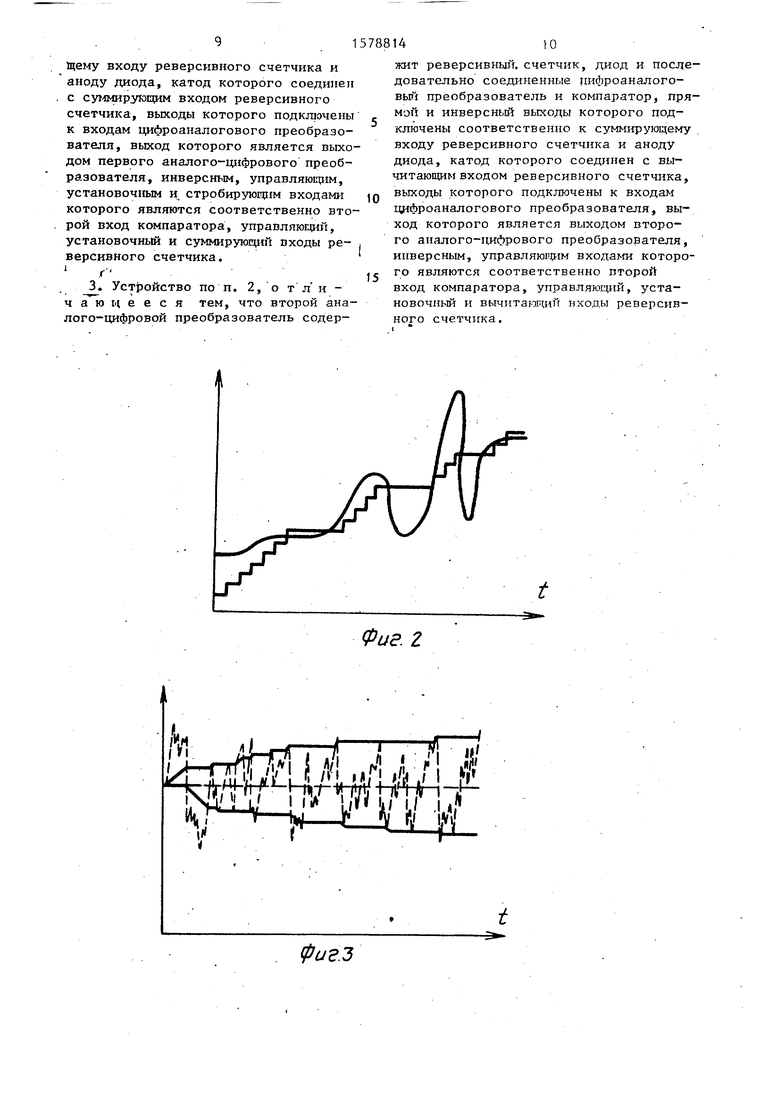

На Лиг. 1 изображена отруктурно- электрическая схема предлагаемого устройства; на фиг. 2 - эпюра напря- жения, поясняющая работу первого и второго аналого-цифровых преобразователей; на фиг. 3 - эпюра напряжения, поясняющая работу первого и второго аналого-цифровых: преобразователей при воздействии шума; на фиг. 4 - эпюра напряжения, поясняющая работу генератора, первого и второго аналого-цифровых преобразователей и делителя частоты; на фиг о 5 - эпюры напряжений, поясняющие работу устройства.

Устройство содержит выходной триггер 1, генератор 2, делитель 3 частоты, первый аналого-цифровой преобразователь 4, второй аналого-цифровой преобразователь 5, входной регулирующий блок 6, сумматор 7, нуль-орган 8, первый 9, второй 10 и третий 11 формирователи импульсов, элемент И 12, первый 13, второй 14, третий 15, чет- вертый 16 диоды, причем каждый аналого-цифровой преобразователь содержит реверсивный счетчик 17, цифроанапого- вый преобразователь 18, компаратор 19 и диод 20„

, Устройство подавления помех работает следующим образом.

Сигнал подается на входной регулирующий блок 6, где автоматически регулируется по усилению с некоторой Јдру Тс/2-полупериода полезного сигнала, и с некоторой погрешностью производится регулировка по амплитуде полезного сигналао С выхода входного регулирующего блока 6 сигнал подается на инверсные входы аналоге-цифровых преобразователей 4 и 5, на выходах которых формируется сигнал, представляющий сигнал слежения за выходным сигналом на первом аналого-цифровом преобразователе 4 в положительную сторону, на втором аналого-цифровом преобразователе 5 - в отрицательную сторону относительно математического ожидания входного сигнала в пределах . Сформированный сигнал на выхода аналого-цифровых преобразователей 4 и 5 преобразует1 эти сигналы в разность ПолУченный разностный сигнал является

g 5 0

5 Q

Q

5

50

аналоговым выходом устройства Этот же разностный сигнал поступает на нуль-орган 8, который фиксирует прохождение через нуль и формирует положительный импульс. Положительный импульс через первый диод 13 развязки подается на установочные входы аналого-цифровых преобразователей 4 и 5 и на второй формирователь 10 импульсов. Сформированный импульс поступает на управляющие входы аналого-цифровых преобразователей 4 и 5. Напряжение с выхода генератора 2 через диоды 15 и 16 поступает на стробирующие входы аналого-цифровых преобразователей 4 и 5. Напряжений генератора 2 поступает на делитель 3 частоты, который работает при отсутствии положительных импульсов с нуль-органа 8. С выхода делителя 3 частоты сигнал поступает на третий формирователь 11 импульсов, с выхода которого сформированный импульс через второй диод 14 подается на установочные входы аналого-цифровых преобразователей 4 и 5 и на формирователь 10 импульсов, а также поступает на первый установочный вход выходного триггера 1, который при помощи первого формирователя 9 импульсов и элемента И 12 формирует выходной цифровой сигнал, при этом на второй вход элемента И 12 поступает сигнал с выхода нуль-органа 8.

Аналого-цифровые преобразователи 4 и 5 при сигнале на входе U|, изменяющемся со сравнительно небольшой скоростью по сравнению со скоростью сигнала сравнения (отслеживания), который подается на первый вход компаратора 19, производит отслеживание этого сигнала, т,е-0 сигналы на входах компараторов 19 в пределах одного шага квантования по напряжению равны. Если сигналы на входах компараторов

19 значительно отличаются один от другого, то время, необходимое для восстановления зналого-цифровых преобразователей 4 и 5 в состояние слежения, зависит от напряжения между входами компараторов 19 и частоты генератора 2. При изменении входного сигнала выше максимально возможной скорости отслеживания аналого-цифровых преобразователей 4 и 5 в момент, когда последние находятся в состоянии слежения, происходит срыв слежения аналого-цифровых преобразователей 4 и 5, и сигнал сравнения по первом

515788

входе компараторов 19 идет по максимально возможной траектории за изменившимся входным сигналом (фиг. 2) для первого аналого-цифрового преобразова- теля 4. Сигнал с генератора 2 с час- торой f g подается через третий и четвертый диоды 15 и 16 на суммирующий вход реверсивного счетчика 17 первого аналогр-цифрового преобразователя 4 и JQ вычитающий вход реверсивного счетчика 17 второго аналого-цифрового преобразователя 5, На этих входах компараторами 19 формируется через диоды 20 значение логического нуля в моменты, j j когда U , U или U 1 U j. Тактовые импульсы положительной полярности с генератора 2 через третий и четвертый диоды 15 и 16 производят запись в один реверсивный счетчик 17 в сторону 20 слежения или в другой реверсивный счетчик 17 в сторону вычитания, в результате чего осуществляется работа первого аналого-цифрового преобразователя 4 по подаваемому напряжению Uf 25 в моменты U U, сравниваемые на компараторе 19, и работа второго аналого- цифрового преобразователя 5 по подаваемому напряжению U) в моменты U -s-Uj, сравннваемг- i на компараторе 19 (фиг.З), JQ где виднс, что при воздействии нормального шума, напряжения 11, и U-j относительно середины динамического диапазона U0 приблизительно-равны между собой. Значения напряжений U2 и Ъ з подаются на сумматор 7 (фиг„ 5а), выход которого является аналоговьм выхоом устройства. Значения напряжений U3 зависят от отклонений математического ожидания нормального ироцес

са относительно составляющей U0, формируемой входным регулирующим блоком 6, равной половине динамического диапазона U Q U-i/2, в пределах времени значительно -превышающего время инте- грирования (фиг.5а), соответственно времени и частоте отклоняющих вверх или вниз по осциллограмме возмущающих помех. При даже небольших отношениях сигнал/шум математическое ожидание процесса, а соответственно,время и частота отклоняющих возмущений - помех неоднозначны. В пределах некоторого временного интервала интегрирования на сумматоре 7 относительная U $ сумма (разность в абсолютном смысле) U Ј и иэ несколько отличается от нуля (фиг. 5а) напряжения аналогового выхода и&вд, что позволяет су

JQ j 20 25 Q

0

.,-

0

5

14

дить о наличии сигнала. Вследствие того, что на входной регулирующий блок 6 поступает пораженный помехой гармонический сигнал, то на выходе сумматора 7 ожидается положительный и отрицательный полупериоды сигнала Тс/2. При воздействии нормального шума переход через нуль на выходе сумматора 7 достаточно частое явление. Нуль-орган 8 при переходе через нуль формирует положительный импульс, который воздействует на установочные входы реверсивных счетчиков 17, и через второй формирователь 10 импульсов производит запись на старший разряд реверсивных счетчиков 17. Аналоговые преобразователи 4 и 5 устанавливаются в начальное состояние, т„е. на их выходах напряжение становится равным U0 (фиг. 5а) в моменты ,t. Если появляется какой-то небольшой по отношению к шуму гармонический сигнал с периодом Тс, тс прохождение через нуль на выходе сумматора 7 в течение времени Тс/2 маловероятно и установка аналого-цифровых преобразователей 4 и 5 в начальное состояние (фиг.5ж) в момент t , 115- осуществляется делителем 3 частоты через время, приблизительно равное , так как при суммировании гармонического сигнала с нормальным шумом вероятность сброса делителя 3 частоты за время Тй/2 ничтожно мала.

Скорость отслеживания входного сигнала на входах аналого-цифровых пре- образователен регулируется изменением частоты генератора 2, которая при нормальной амплитуде входного полезного сигнала изменяется пропорционально изменению частоты входного гаг чоничес- кого сигнала )f , т.е. при увеличении (уменьшении) частоты гармонического сигнала соответственно увеличивается (уменьшается) частота генератора 2 Ur (фиг„ 4)

Соответственно пропорционально этим изменениям изменяется время между подачей фронтов логических сигналов с выхода делителя 3 частоты UCT (фиг„ 4), коэффициент деления которого подобран так, что время между подачей фронтов с выхода делителя 3 частоты приблизительно равно времени Т./2 - половине периода входного сигнала Частота генератора 2 зависит от частоты подаваемого на вход устройства гармонического сигнала, пораженного

помехой Генератор 2 конструктивно может быть связан с ручкой регулировки (Высоты тона принимаемого гармонического сигнала (не показано). Делитель 3 , частоты с выхода нуль-органа 8 достаточно часто сбрасывается при воз™ действии нормального шума и маловероятно сбрасывается при воздействии гармонического сигнала, поэтому в послед- kfg нем случае на выходе делителя 3 частоты третьего формирователя 11 импульсов через время Тс/2 появляется импульс, сбрасывающий раверсивные счетчики 17 в нулевое состояние и через 15 второй формирователь 10 импульсов записывающий на старший регистр реверсивных счетчиков 17 логическую единицу 9 что ведетъаналого-цифровые преобразователи 4 и 5 в точку начала слеже- Q ния UD 5 находящуюся в середине динэми- ческого диапазона Это приблизительно соответствует переходу гармонического сигнала через нуль. При этом переходе возможны дополнительные варианты ра 25 венства U и U (фиг. 5а) в момент что ведет к появлению импульса сброса делителя 3 частоты.

Третий формирователь 9 импульсов и элемент И 12 предохраняют выходной 3 триггер 1 от ложных срабатываний подбором длительности импульса третьего формирователя 9 импульса, что защищает цифровой выход устройства от ложных срабатыванийо

Выбором си mвходной регулирующий блок 6 можно определить критерий реакции устройства на нестацйонарность нормального процессаэ нестационарностъ которого частично определена некоторым гармоническим колебанием с периодом Тс„ На аналоговом выходе устройства получается напряжение иоЬ1Х(фигв 5б) в некоторых пределах по длительности TC/2S интегрированное с эффектом пос- 4 тоянного суммирования напряжении и„ и U з аналоговых выходов аналоге-цифро - вых преобразователей 4 и 5, Цифровая часть устройства резгяруат отдельно на импульсы с нуль-органа ияРг.(Фиг.5вХ; ь импульсы с выхода третьего формирователя И импульсов (фиг.5г). На второй установочный вход выходного триггера I и5т (фиг.Зд) поступают импульсы , кроме импульсов, появ- г ляющихся в пределах некоторой длитель- ности, определяемой длитеиьностыо задержки первого формирователя 9 импульсов с целью недопустимости импульсов

UUCTBO время перехода гармонического сигнала через нуль. На цифровом выходе устройства формируется сигнал наличия дискретного сообщения UT (фиг.5е).

Формула изобретения

1. Устройство подавления помех, содержащее последовательно соединенны первый формирователь импульсов и элемент И, последовательно соединенные генератор и делитель частоты,;а также выходной триггер, инверсный выход которого является цифровым выходом устройства, отличающееся тем, что, с целю повышения эффективности подавления, введены входной ре- i/лируощий блок, второй и третий фор- рователи импульсов, первый и второй аналого-цифровые преобразователи, четыре диода и последовательно соединенные сумматор и нуль-орган, выход которого подключен к вторым входам делителя частоты и элемента И и аноду первого диода, катод которого соедине с входом второго формирователя импульсов, катодом второго диода и.установочными входами первого и второго аналого-цифровых преобразователей, инверсные управляющие входы и выходы которых соединены с выходами соответственно входного регулирующего блока и второго формирователя импульсов и входами сумматора, стробирующие входы первого и второго аналого-цифровых преобразователей соединены с катодами соответственно третьего и четвертого диодов, аноды которых соединены с выходом генератора, выход делителя частоты через третий формирователь импульсов подключен к аноду второго диода, к первому установочному входу выходного триггера, второй установочный вход и прямой выход которого соединены соответственно с выходом эле- veHTa И и входом первого формирователя импульсов, Вход входного регулирующего блока является входом устройства , аналоговым выходом которого является выход с/мматорао

2„ Устройство по п 1з о т л и - чающееся тем, что первьй аналого-цифровой преобразователь содер- хсит реверсивный счетчик, диод и последовательно соедчьенные цифроаналого- вый преобразователь и компаратор, инверсный и прямой выходы которого подключены соответственно х вычитаю91

щему входу реверсивного счетчика и аноду диода, катод которого соединен с суммирующим входом реверсивного счетчика, выходы которого подключены к входам цифроаналогового преобразователя, выход которого является выходом первого аналого-цифрового преобразователя, инверсным, управляющим, установоч сым и стробируюгщм входами которого являются соответственно второй вход компаратора, управляющий, установочный и суммирующий входы реверсивного счетчика. 1 f

3. Устройство по п. 2, о т л и - ч ц е е с я тем, что второй аналого-цифровой преобразователь содер7881410

жит реверсивный, счетчик, диод и последовательно соединенные цифроаналого- вый преобразователь и компаратор, прямой и инверсный выходы которого под- ключены соответственно к суммирующему входу реверсивного счетчика и аноду диода, катод которого соединен с вычитающим входом реверсивного счетчика, выходы которого подключены к входам цийроаналогового преобразователя, выход которого является выходом второго аналого-цифрового преобразователя, инверсным, управляющим входами которого являются соответственно пторой вход компаратора, управляющий, установочный и вычитающий ьходы реверсивного счетчика.

10

15

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь угла поворота вала в код | 1986 |

|

SU1410277A1 |

| Устройство для измерения коэффициента пульсаций постоянного напряжения | 1989 |

|

SU1742644A1 |

| Стабилизатор переменного напряжения | 1989 |

|

SU1716496A1 |

| Аналого-цифровой интегратор | 1978 |

|

SU805345A1 |

| Аналого-цифровой функциональный преобразователь | 1975 |

|

SU748857A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ В ЦИФРОВОЙ КОД ОТКЛОНЕНИЯ | 1992 |

|

RU2074396C1 |

| Программируемый преобразователь напряжения произвольной формы в напряжение требуемой формы | 1990 |

|

SU1711303A1 |

| Преобразователь сдвига фаз вцифРОВОй КОд | 1974 |

|

SU817603A1 |

| СПОСОБ УПРАВЛЕНИЯ ЭЛЕКТРОПРИВОДОМ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2020724C1 |

| Цифровой анализатор спектра | 1985 |

|

SU1298679A1 |

Изобретение относится к радиотехнике и может найти применение в устройствах обработки дискретных сигналов. Целью изобретения является повышение эффективности подавления. Поставленная цель достигается за счет введения входного регулирующего блока 6, второго 10 и третьего 11 формирователей импульсов, первого 4 и второго 5 аналого-цифровых преобразователей, четырех диодов 13, 14, 15, 16, сумматора 7 и нуль-органа 8. Подбором длительности импульса третьего формирователя импульса 11 защищают цифровой выход устройства от ложных срабатываний. Выбором постоянной времени входного регулирующего блока 6 определяют критерий реакции устройства на нестационарность нормального процесса. 2 з.п. ф-лы, 5 ил.

MWW

н

I

VL

if LNr nW -jftf

фиг.з

Фиг. Z

-jb

tf

И И И 1 Ill

IIMI in и

II ill it

IHl|| H i It

IIMill II I II

II Hill П I |l

ж

TI ПТЛ ГП IT in и 11 i ill II

У2 foto

фиеЛ

t

II

J

Фиг5

| Цифровой асинхронный регенератор дискретных сигналов | 1985 |

|

SU1241486A1 |

Авторы

Даты

1990-07-15—Публикация

1988-09-19—Подача