блоком считывания,блоком кодировани блоком вычисления, блоком индикаций генератором тестового линейно нарастающего напряжения, дополнительной линией задержки с отводалш, дополнительными блоками выборки и дополнительными усилителями-расширителями. Причем выходы последних соединены с входом блока считывания, а входы с выходами дополнительных блоков выборки, одни входы которых подключены к выходам блоков формирования строб-импульсов с регулируемой задержкой, а другие входы - к отводам дополнительной линии задержки, вход которой-связан с выходом генератора тестового линейно нарастающегх напржения, входом соединенного с вторым

ВЫХОДОМ блока формирования синхроимпульсов третий выход которого соединен с его первым выходом, при это выходы основных усилителей-расширителей подключены к другому входу блка считывания, выход которого связан с входом блока кодирования, выхдом саединенно17О. с входом блока вычисления, выход которого подключен к входу блока индикации.

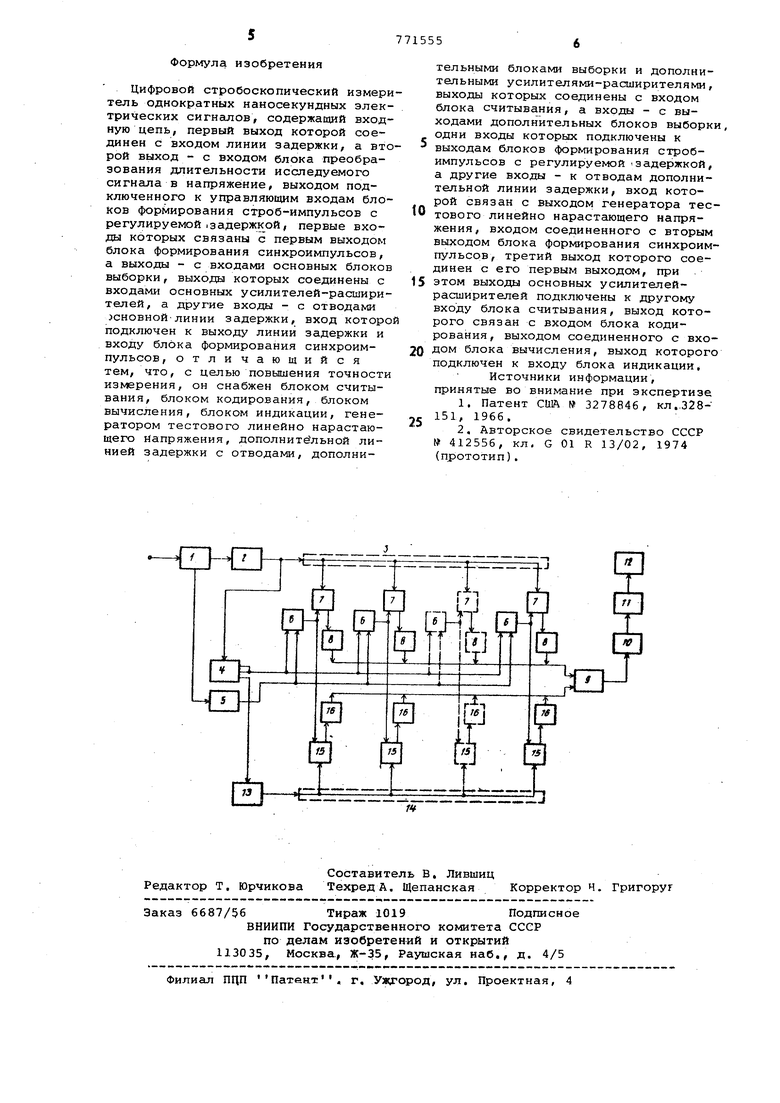

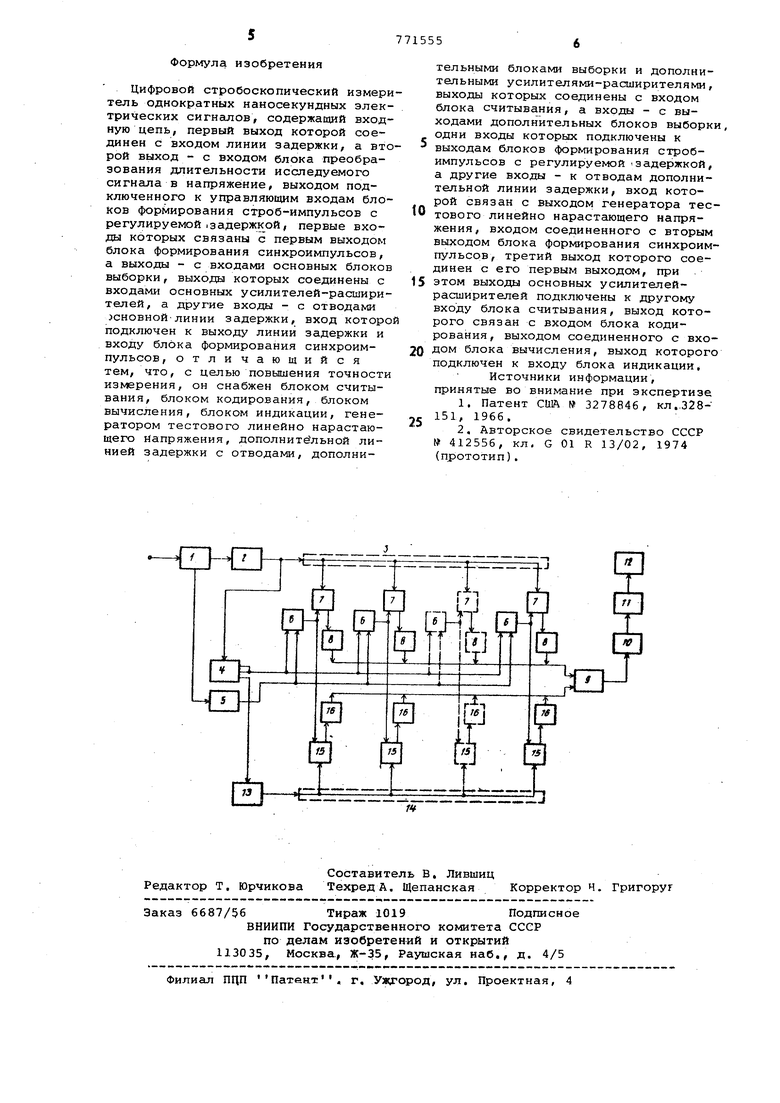

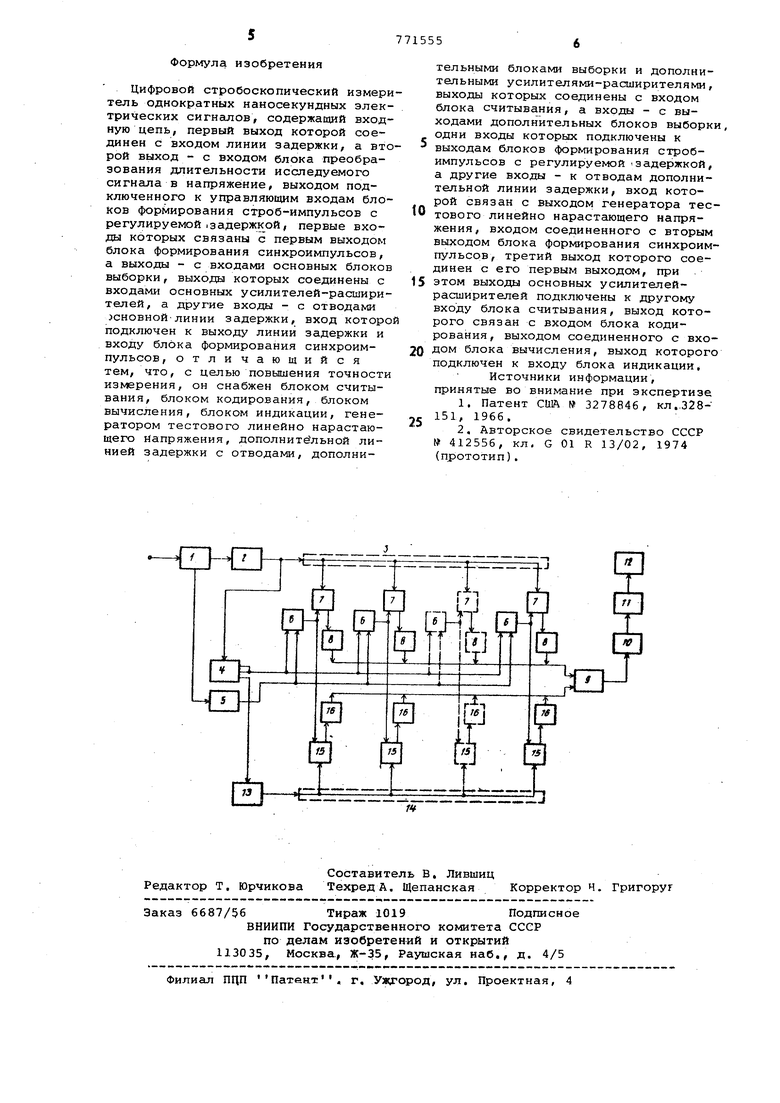

Структурная электрическая схема устройства представлена на чертеже.

Устройство состоит из входной цепи 1, линии задержки 2, основной линии заДержки 3 с отводами, блока формирования 4 синхроимпульсов, блока 5 преобразования длительности исследуемого сигнала в напряжение, блоков б формирования строб-импульсов с регулируемой задержкой, основных блоков выборки 7, основных усилителей-расширителей 8, блока считывания 9, блока кодирования 10, блока вычисления 11,блока индикации 12, генератора тестового линейно нарастающего напряжения 13, допонительной линии задержки 14 с отводами, дополнительных блоков выборки 15 и дополнительных усилителей-расширителей 16,

Устройство работает следующим образом.

Исследуемый сигнал поступает через входную цепь 1 в линию задержки 2 и в блок 5 преобразования длительности исследуемого сигнала в напряжение. Пока исследуемый сигнал достигает фронтом входа линии задержки 3, в блоке преобразования длительности вырабатывается напряжение управления, пропорциональное длительности исследуемого сигнала и определяющее;величину шага считывания Это напряжение подается на управляющие входы блоков 6 формирования строб-импульсов с регулируемой 3 адержкой. На пер вые входа этих блоков поступают импульсы запуска из блока 4. Задержанные относительно импульсов запуска (и сигнала) строб-импульсы последовательно отпирают ключи блоков выборки 7 на время считывания выборки сигнала,, распространяющегося в линии задержки 3, Разность задержек строб-импульсов соседних блоков .6 увеличивается с увеличением длительности исследуемых сигналов. Усиленные и расширенные усилителями 8 импульсы выборок считываются с тактовой частотой блоком считывания 9 и закодированные в блоке 10 запоминают0ся в регистрах памяти блока вычисления 11,

Одновременно дополнительными блоками выборки 15 считываются выборки тестового линейно нарастающего

5 напряжения, сформированного в генераторе 13 и распространяющегося в линии задержки 14 синхронно с исследуемым сигналом. При этом отпирание ключей дополнительных блоков

0 выборки осуществляется строб-импульсами, сформированными в блоках 6 формирования строб-импульсов с регулируемой задержкой. Синхронизация тестового напряжения осуществляется синхроимпульсом, поступающим из

5 блока 4, Считанные блоком 9 выходные импульсы дополнительных усилителейрасширителей 16 кодируются в виде последовательно дискретных значений напряжения, пропорционального истин0ному временному положению стробимпульсов во времени в моменты стробирования однократного сигнала. Затем по содержащимся в регистрах памяти блока вычисления 11 дискрет5ным значениям выборок и их истинному временному положению сигнал восстанавливается и воспроизводится в блоке индикации 12, Так как считывание пар последовательностей мгно0венных значений исследуемого и тестового сигналов осуществляется одними и теми же строб-импульсами, то фиксируются как медленные, так и мгновенные вре1 кнные их нестабильности, что позволяет при обработке резуль5татов в блоке вычисления уменьшить амплитудные искажения преобразованного сигнала.

§Q Вслед за регистрацией исследуе мого сигнала формируется повторный импульс синхронизации (третий выход блока 4) и осуществляется повторный запуск формирователей строб-импуль. сов блока б, что позволяет по двум парам зарегистрированных реализаций ( .нулевой линии и исследуемого сигнала и нулевой линии и тестсигнала) при обработке данных произвести коррекцию систематических или

&Q сил|ьно коррелированных во времени сшибок преобразования, присущих обоим каналам.

Устройство обеспечивает повышени точности измерения широкого класса

45 исследуемых сигналов,

Формула изобретения

Цифровой стробоскопический измеритель однократных наносекундных электрических сигналов, содержащий входную цепь, первый выход которой соединен с входом линии задержки, а второй выход - с входом блока преобразования длительности исследуемого сигнала в напряжение, выходом подключенного к управляющим входам блоков формирования строб-импульсов с регулируемой 13адержк ой, первые входы которых связаны с первым выходом блока формирования синхроимпульсов, а выходы - с входами основных блоков выборки, выходы которых соединены с входами основных усилителей-расширителей, а другие входы - с отводами основной-линии задержки, вход которо подключен к выходу линии задержки и входу блока формирования синхроимпульсов , отличающийся тем, что, с целью повышения точности измерения, он снабжен блоком считывания, блоком кодирования, блоком вычисления, блоком индикации, генератором тестового линейно нарастающего Напряжения, дополнительной линией задержки с отводами, дополнительными блоками выборки и дополнительными усилителями-расширителями, выходы которых соединены с входом блока считывания, а входы - с выходами дополнительных блоков выборки, одни входы которых подключены к выходам блоков формирования стробимпульсов с регулируемой Задержкой, а другие входы - к отводам дополнительной линии задержки, вход которой связан с выходом генератора тес0тового линейно нарастающего напряжения, входом соединенного с вторым выходом блока формирования синхроимпульсов, третий выход которого соединен с его первым выходом, при

5 этом выходы основных усилителейрасширителей подключены к другому входу блока считывания, выход которого связан с входом блока кодирования , выходом соединенного с входом блока вычисления, выход которого подключен к входу блока индикации,

Источники информации, принятые во внимание при экспертизе

1.Патент США № 3278846, кл..328151, 1966.

5

2.Авторское свидетельство СССР 412556, кл. G 01 R 13/02, 1974 (прототип).

Авторы

Даты

1980-10-15—Публикация

1978-11-29—Подача