Изобретение относится к радиотех-нике и может использоваться в радиоприемных устройствах для приема непрерывного потока информации с постоянной кодовой структурой.

Известно устройство синхрониза1ХИИ, содержащее последовательно соединенные реверсивный счетчик,блок обнаружения и формирователь сигнала, объединенный с входом согласованного фильтра, другой вход которого через первый делитель частоты соединен с выходом блока добавления вычитания, соединенного по входу с реверсивным счетчиком, второй вход которого соединен с выходом первого делителя частоты, и друзтим входом блока обнаружения, и второй делитель частоты, соединенный по входу с первым делителем частоты 1,

Однако такое устройство имеет невысокую скорость вхождения в синхронизм..

Цель изобретения - повышение скорости вхождения в синхронизм.

Цель достигается тем, что в устройство синхронизации, содержащее последовательно соединенные реверсивный счётчик, блок обнаружения и формирователь сигнала, объединенный

с входом согласованного фильтра, другой вход которого через первый делитель частоты соединен с выходом блока добавления-вычитания, соединенного по входу с реверсивным счетчиком, второй вход которого соединен с выходом первого делителя частоты и другим входом блока обнаружения, и второй делитель частоты, соедиtoненный по в.чоду с первым делителем частоты, введены последовательно соединенные бинарный квантователь, регистр сдвига, перемножитель, блок формирования стробов и блок эле15ментов И-ИЛИ, а также третий и четвертый делители частоты, два блока совпадения и триггер, причем инверсный выход триггера подключен к вторым входам блока элементов И-ИЛИ и

20 через последовательно соединенные первый блок совпадения, третий и четвертый делители частоты подключен к входу триггера, другой вход которого через второй блок совпаде25ния соединен с выходом третьего делителя частоты, а прямой выход триггера подключен к третьим входам блока элементов И-ИЛИ,четвертые входы которого соединены с выходом второ;; го делителя частоты,а выходы блока

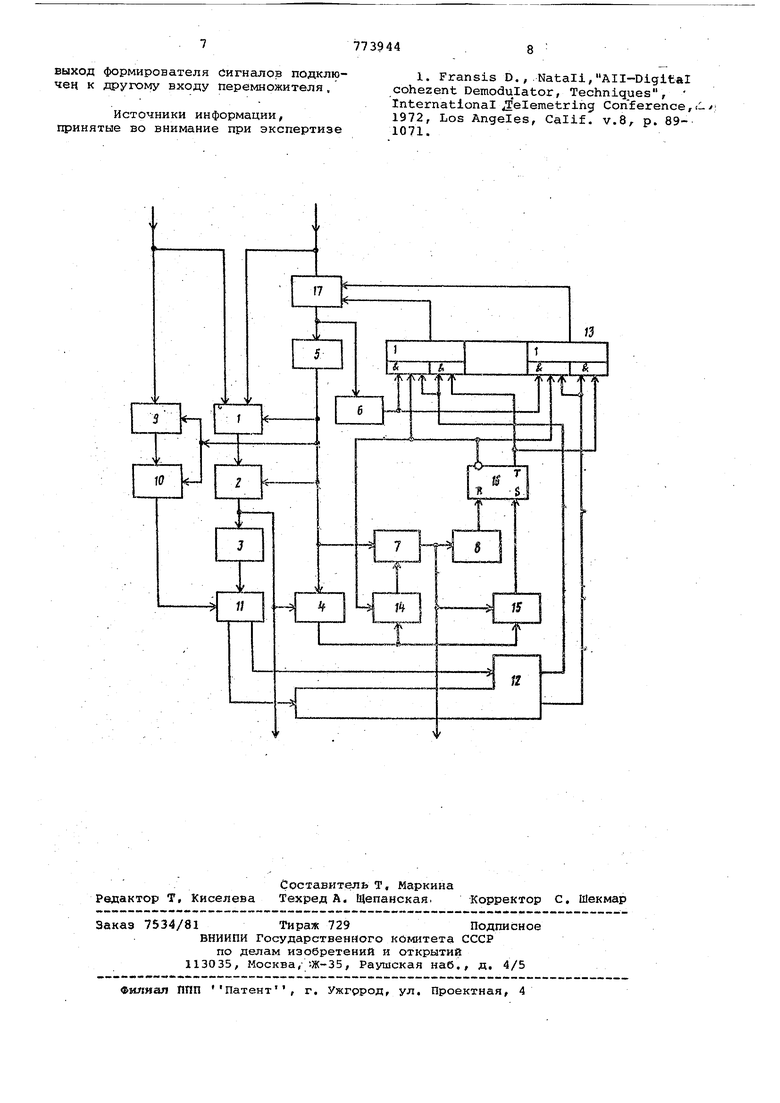

30 элементов И-ИЛИ подключены к другим входам блока добавления-вычитания, причем вход бинарного квантователя объединен с третьим входом реверсивного счетчика, выход первого делителя частоты подключен к другим входам бинарного квантователя, регистра сдвига и третьего делителя частоты, при этом выход согласованного фильтра подключен к другим входам блоков совпадения, а выход формирователя сигналов подклю чен к другому входу перемножителя. На чертеже дана структурная элек рическая схема предложенного устройства. Устройство содержит реверсивный счетчик 1, блок 2 обнаружения, формирователь 3 сигнала, .согласованный фильтр 4, делители 5-8 частоты, бинарный квантователь 9, регистр 10 сдвига, перемножитель 11,- блок 12 формирования стробов, блок 13 элементов И-ИЛИ, блоки 14 и 15 совпадения, триггер 16 и-блок 17 добавления-вычитания. Устройство работает следующим образом. Входной информационный сигнал, ограниченный по амплитуде и привязанный по уровню к логическим 0 или выбранной элементной базы подается на вход реверсивного счетчика 1, На другой вход которого подается импульсная последовательность опорной частоты fon Частота fpf,. выбирает с я намного выше символьной частоты информации f чтобы иск чить энергетические потери за счет дйухуровнего ограничения входного процесса при цифровом интегрировании. Входной сигнал подается на шину управления, а опорная импульс ная последовательность на счетный вход реверсивного счетчика 1. Объем реверсивного счетчика 1 2 долже быть больше отношения N : f /2ff, причем старший разряд является знаковым и его выходной потенциал является входным сигналом блока 2, Дпй обеспечения сброса реверсив ного сигнала 1 и опроса блока 2 служат блок 17 и делитель 5, Часто та следования импульсов на выходе делителя 5 связана с опорной часто той fpf, зависимостью f г fon/N . В режиме синхронизма f f- мо менты появления импульсов совпадаю с границами принимаемых символов и формации. Реверсивный счетчик 1 за период интегрирования Т,т 1 /fp производит подсчет разности количества импульсов опорной последова тельности, прошедааих по шине сложения и шине вычитания. В крице периода интегрирования в блоке 2 так товым импульсом с выхода делителя 5 производится опрос состояния зна кового разряда реверсивного счетчи а 1, после чего он сбрасывается. сли потенциал знакового разряда ыл высоким, принимается решение о ом, чтобы передавался символ , сли - низким, принимается решение передаче символа О, С выхода блока 2 информация поступает на выход устройства и на ход согласованного фильтра 4, на ругой вход которого подается последовательность импульсов тактовой частоты f-y с выхода делителя 5, В согласованном фильтре 4 производится оптимальная фильтрация кадрового слова и сравнение выходного сигнала фильтра с некоторым порогом,по превышении которого принимается решение о наличии синхронизации в устройстве. Для формирования оптимальной дискриминационной характеристики тактовой синхронизации сигнал с выхода блока 2 через формирователь 3 подается на перемножитель 11. В формирователе 3 формируется сигнал 4-1 каждый раз при смене символа с О на 11 и сигнал - 1 при обратной смене символов. Если смена символов не прои-сходит г вырабатывается сигнал О, В перемножителе 11 производится перемножение выходных сигналов формирователя 3 с задержанными на длительность одного символа бинарно квантованными отсчетами входного процесса. Квантование производится с тактовой частотой f в бинарном квантователе 9, а задержка на один символ осуществляется с помощью- регистра 10, на информационный вход которого поступают отсчеты входного процесса с выхода бинарного кванто вателя 9, а на счетный вход импульсная последовательность тактовой частоты f с выхода делителя 51. Перемножитель 11 выполняется на логических элементах исключающее ИЛИ, Импульсный сигнал управления с первого или второго выхода перемножителя 11 через блоки 12 и 13 подается на управляющие входы блока 17, Появление импульса управле выходе перемножителя 11 приводит к добавлению импульса в опорную последовательность и фазовому сдвигу тактовой последовательности .импульсов, на выходе делителя 5 на величину Дф 211/М .Появление импульса управления на другом выходе пёремножителя 11 приводит к исключению импульса из опорной последовательности и фазовой задержке сигнала тактовой частоты f.f на А1 -2й./п, . Количество добавленных или исключенных за один период регулирования импульсов определяется эквивалентной полосой пропускания тактоВОЙ синхронизации, т.е. режимом работы устройства. В режиме вхождения в связь экви валентная полоса пропускания широка В этом режиме разраиающий потенциал с инверсного входа триггера 16 открывает блок 13, Количество импул сов, попадающих во временной интервал действия строба, определяет расширение эквивалентной полосы пропускания устройства. В режиме синхронизма устройства разрешающий потенциал с прямого выхода триггера 16 открывает блок 13 и строб с выхода блока 12 ПРОИЗВОДИ одноразовое за период регулирования изменение фазы сигнала тактовой частоты. При этом необходимо, чтобы дпительность стробов была меньше периода регулирования, т.е. длительность символа. Работой триггера 16 управляет согласованный фильтр 4. Для уменьше ния вероятности ложной синхронизации по кадрам в режиме вхождения в связь, а также-уменьшения количества сбоев у кадровой синхронизации в режиме синхронизма в устройстве предусмотрена блокировка работы три гера 16 от ложных срабатываний и сбоев, которая работает следующим образом. Из тактовой импульсной последовательности с помощью делителя 7 формируется импульсная последовательность с периодом, равным периоду кадра информации. В режиме вхождения в связь первый импульс с выхо да согласованного фильтра 4 через открытый триггером 16 блок 14 синхронизирует делитель 7 и одновременно подается на блок 15, на второй вход которого подаются импульсы с выхода делителя 7. Если первый кадровый импульс был не ложный и если не произошло сбоя второго кадрового импульса, то произойдет совпадение по времени второго кадрового импуль са с выходным импульсом делителя 7 и выходной импульс блока 15 установит триггер 16 в , переведя, тем.самым, устройство в режим синхронизма и заблокировав блок 14 от повторной синхронизации делителя 7. Обратный перевод устройства в режим .вхождения в связь производится при условии сбоя подряд кадровых импульсов. Для этого делитель 8, сбрасываемый в О импульсами с блока 15, подсчитывает количество кадровых импульсов с делителя 7 в случае отсутствия подряд 6 импульсов на выходе блока 15, переполняется и импульсом переполнения устанавливает триггер 16 в О . Использование в предложенном .устройстве промежуточной системы кадровой синхронизации и формирование :оптимальной фазовой дискриминационной характеристики позволяет создать автоматическую систему синхронизации с изменяющимися параметрами в зависимости от режима работы, т.е. обеспечить надежное вхождение в связь за минимальное время, производить квазиоптимальную посимвольную обработку информации в режиме синхронизма с малой вероятностью сбоя кадровой синхронизации. Изменением частоты опорной последовательности можно просто осуществлять обработку сигналов с различной скоростью передачи информации. Формула изобретения Устройство синхронизации, содержащее последовательно соединенные реверсивный счетчик, блок обнаружения и формирователь сигнала, объединенный с входом согласованного фильтра, другой вход которого через первый делитель частоты соединен с выходом блока добавления-вычитания, соединенного по входу с реверсивным счетчиком, второй вход которого соединен с выходом первого делителя частоты и другим входом блока обнаружения, и второй делитель частоты, соединенный по входу с первым делителем частоты, отличающеес я тем, что, с целью повьиаения скорости вхождения в синхронизм, введены последовательно соединенные бинарный кантователь, регистр сдвига, перемножитель, блок формирования стробов и блок элементов И-ИЛИ, а также третий и четвертый делители частоты, два блока совпадения и триггер, причем инверсный выход триггера подключен к вторым входам блока элементов И-ИЛИ и через последовательно соединенные первый блок совпадения, третий и четвертый делители частоты подключен к входу триггера, другой вход которого через второй блок совпадения соединен с выходом третьего делителя частоты, а прямой выход триггера подключен к третьим входам блока элементов И-ИЛИ, четвертые входы которого соединены с выходом второго делителя частоты, а выходы блока элементов И-ИЛИ подключены к ругим входам блока добавления-выитания, причем вход бинарного кванователя объединен с третьим входом еверсивного счетчика, выход первого елителя частоты подключен к друим входам бинарного квантователя, егистра сдвига и третьего делитея частоты, при этом выход соглаованного фильтра подключен к друим входам блоков совпадения, а

выход формирователя сигналов подключен к другому входу перемножителя,

Источники информации, принятые во внимание при экспертизе

1. Fransis D.,.Natali,All-Digital cohezent Demodulator, Techniques, International elemetring Conference, 1972, Los Angeles, Calif, v.8, p. 891071.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство символьной синхронизации | 1990 |

|

SU1775869A1 |

| Устройство для выделения кадрового синхронизирующего слова | 1989 |

|

SU1704146A1 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| Устройство для выделения маркера кадровой синхронизации | 1983 |

|

SU1095434A1 |

| Устройство для выделения маркера кадровой синхронизации | 1989 |

|

SU1663775A1 |

| Устройство для выделения маркера кадровой синхронизации | 1978 |

|

SU752313A1 |

| СПОСОБ СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ | 1990 |

|

RU2011302C1 |

| Устройство цикловой синхронизации последовательного модема | 1986 |

|

SU1450123A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ ПРИЕМНИКА ШУМОПОДОБНЫХ СИГНАЛОВ | 1980 |

|

SU1840647A1 |

| Устройство для выделения кадрового синхронизирующего слова | 1990 |

|

SU1774325A2 |

Авторы

Даты

1980-10-23—Публикация

1979-01-25—Подача