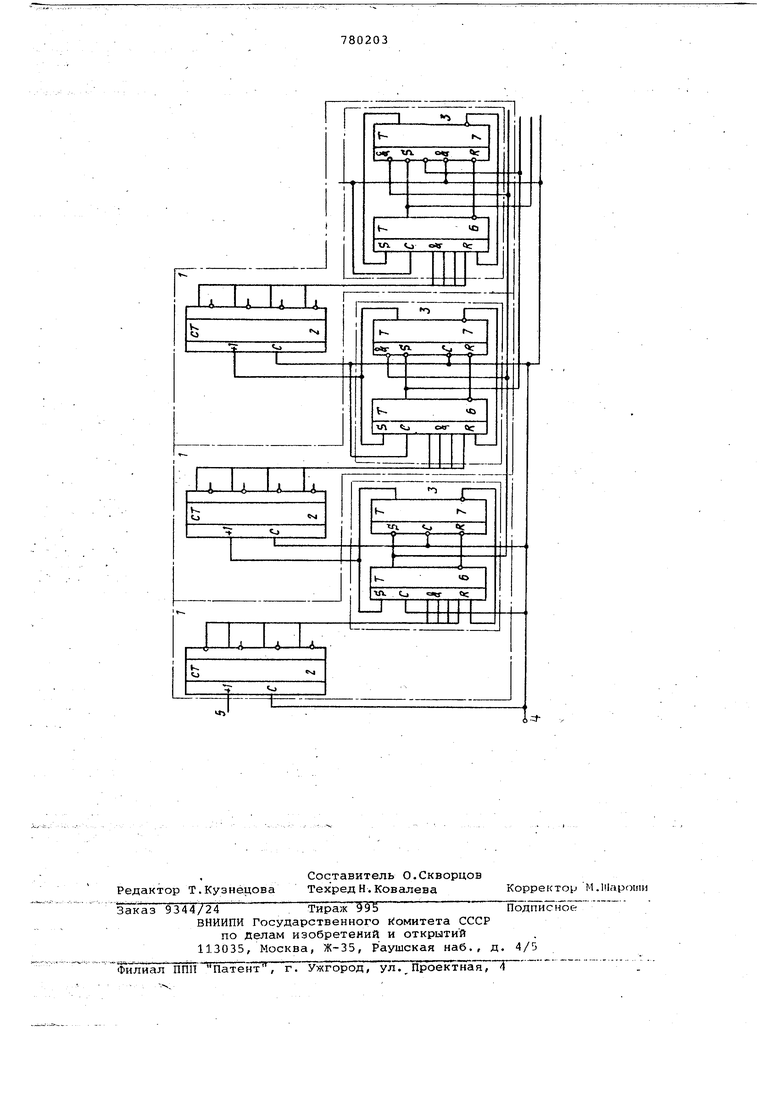

формирователя сигнала переноса первого разряда соединен с первым инверсним выходом счетчика первого разряда, тактовые входы формирователей сигналов переноса соединены с тактовым входом устройства, а управляющие входы формирователей сигналов переноса каждого из разрядов соединены с -вторыми выходами формирователей сигналов переноса предыдущих разрядов. Каждый формирователь сигнала переноса содержит первый и второй триггер, тактовые входы которых соединены с тактовым входом форм рователя сигнала переноса, информационные входы которого соединены с входами сброса первого триггера, объединенными по И, вспомогательный вход сброса которого соединен с инверсным выходом второго триггера, прямой выходкоторого соединён с.пер вым выходом формирователя сигнала пе реноса и входом установки первого триггера, инверсный выход которого соединен с инверсным входом сброса второго триггера, инверснь1й вход установки которого соединен с прямым выходом первого триггера и вторым выходом формирователя сигнала переноса, управляющие входы которого соединены с выходами устанбвкй второго триггера. Структурная схема счетного устрой ства показана на чертеже. Счетное устройство содержит в каж дом разряде 1 счетчик 2 и формирователь сигнала переноса 3, информацион ныё входы которого в каждом из разря дов , кроме первого входа первого раз ряда, соединены с единичными выходами счетчика 2 того же разряда, такто вые входы счетчиков 2 соединены с та товым входом 4 счетного устройства, первый выход формирователя сигнала переноса каждого разряда соединен со счетным входом счетчика 2 следующего разряда, а счетный вход счетчика 2 первого разярда соединен со счетным входом 5 устройства, первый информационный вход формирователя сигнала переноса 3 первого разряда соединены инверсным выходом счетчика 2 первого разряда, тактовые входы формирователей сигнала переноса 3 соединены с тактовым входом 4 устрой ства, а управляющие входы формирователей сигнала переноса 3 каждого из разрядов соединены с вторыми вых.одами формирователей сигналов 3 перенос предыдущих разрядов. Каждый формирователь сигнала переноса 3 содержит первый б и второй 7 триггера, тактовые входы которых соединены с тактов входом формирователя сигнала перено ТHa lV йЩорйЩйбнйШ ;входйк6 е)рого соединены с входами сброса Первого триггера 6, объединенными по И, всйо

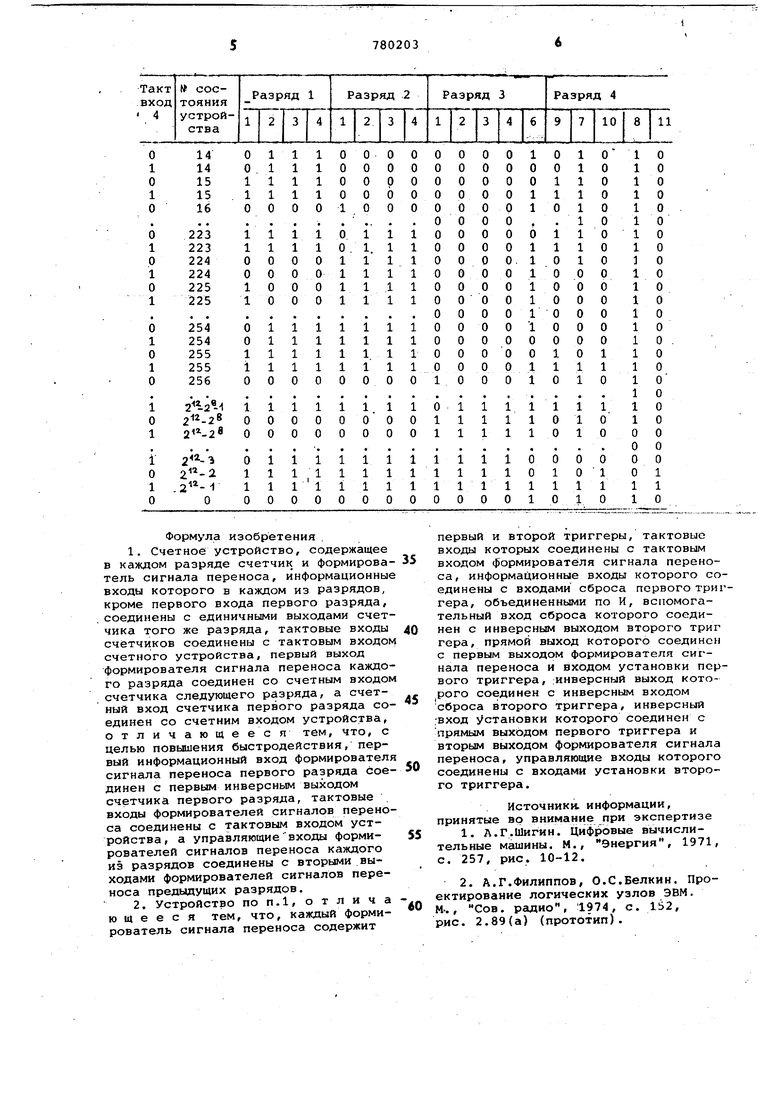

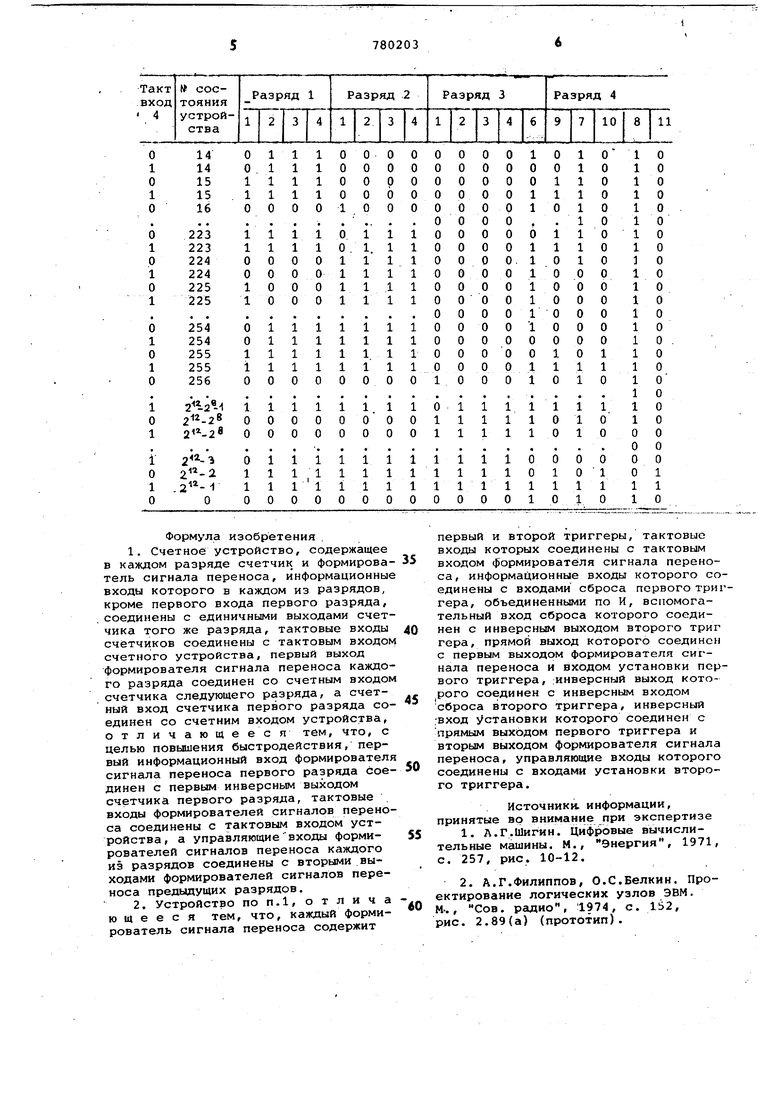

780203 огательный вход сброса которого содинен с инверсным выходом второго триггера 7, прямой выход которого соединен с первым выходом формирователя сигнала переноса 3 и входом установки первого триггера 6, инверсный выход которого соединен с инверсным входом сброса второго триггера 7, инвер-г сный вход установки которого соединен с прямым выходом первого триггера 6 и вторым выходом формирователя сигнала переноса, управляющие входы которого соединены со входами установки второго триггера. Счетное устройство работает следующим образом. При работе на счетный вход 5 подается сигнал логической единицы. Переключения сигналов на выходах разрядов и триггеров 7 происходят при сигнале логического нуля на тактовом входе 4. Переключения сигналов на выходах триггеров б происходят при сигна ле логической единицы на тактовом входе 4, Функционирование первых трех разрядов 1 и триггеров б и 7 поясняется таблицейсостояний. В таблице состбяний на всех строках, где тактовый сигнал принимает значения логического нуля (единицы) указаны значения сигналов на первых выходах разрядов 1 и триггеров б и 7 после окончания переходных процессов, вызванных переключением тактового сигнала в логический нуль (единицу). До состояния № 14 переключается тсэлько разряды группы 1. В состоянии № 14 при сигнале логической единицы на входе 4 переключается триггер б первого разряда в состояние логического нуля, так как на все его входы сброса подаются сигналы логической единицы. После переключения тактового сигнала в логический нуль устройство переходит в состояние № 15 и одновременно переключается триггер 7 первого разряда в состояние логической единицы. После переключения тактового сигнала в логическую единицу триггер б переключается в логи ческую единицу. Следующее переключение тактового сигнала вызывает переход устройства в состояние № 16. Дальнейшие переключения разрядов происходят аналогично. В состоянии счетчика № , когда все разряды находятся в состоянии логической единицы, происходит запись сигнала .лбгического нуля в триггер .6 последнего разряда. Переключение триггера ,7 последнего разряда в логическую единицу произойдет при состоянии счетчика vf 2 - 2 после того, когда переключится триггер 6 первого разряда в состояние логического г)уля. Формула изобретения 1. Счетное устройство, содержащее в каждом разряде счетчик и формирователь сигнала переноса, информационные входы которого в каждом из разрядов, кроме первого входа первого разряда, соединены с единичными выходами счетчика того же разряда, тактовые входы счётчиков соединены с тактовым входом счетного устройства, первый выход формирователя сигнала переноса каждого разряда соединен со счетным входом счетчика следующего разряда, а счетный вход счетчика первого разряда соединен со счетним входом устройства, отличающееся тем, что, с целью повьлшения быстродействия, первый информационный вход формирователя сигнала переноса первого разряда соединен с первым инверсным выходом счетчика первого разряда, тактовые входы формирователей сигналов переноса соединены с тактовым входом устройства, а управляющиевходы формирователей сигналов переноса каждого из разрядов соединены с вторьдми выходами формирователей сигналов переноса предыдущих разрядов. 2. Устройство по п.1, о т л и ч а ю щ е е с я тем, что, каждый формирователь сигнала переноса содержит первый и второй триггеры, тактовые входы которых соединены с тактовым входом формирователя сигнала переноса, информационные входы которого соединены с входами сброса первого три г гера, объединенными по И, вспомогательный вход сброса которого соединен с инверсным выходом второго триг гера, прямой выход которого соединен с первым выходом формирователя сигнала переноса и входом установки первого триггера, :инверсный выход которого соединен с инверсным входом сброса второго триггера, инверсный вход Установки которого соединен с прямым выходом первого триггера и вторым выходом формирователя сигнала переноса, управляющие входы которого соединены с входами установки второго триггера. Источники, информации, принятые во внимание при экспертизе 1.А.Г.Шигин. Цифровые вычислительные машины. М., Энергия, 1971, с. 257, рис. 10-12. 2.А.Г.Филиппов, О.С.Белкин. Проектирование логических узлов ЭВМ. М-., Сов. радио, 1974, с. 152, рис. 2.89(а) (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Счетное устройство | 1982 |

|

SU1080250A1 |

| Счетное устройство | 1981 |

|

SU1023664A1 |

| Счетное устройство | 1980 |

|

SU892737A1 |

| Устройство для контроля радиоэлектронных блоков | 1988 |

|

SU1640694A1 |

| Устройство для контроля логических блоков | 1988 |

|

SU1553980A1 |

| ЭЛЕКТРОННЫЙ ЗАМОК | 2002 |

|

RU2213191C1 |

| Устройство для числового программного управления | 1985 |

|

SU1352459A1 |

| Устройство для обработки сообщений | 1990 |

|

SU1803919A1 |

| Устройство для измерения мгновенного хода часов | 1985 |

|

SU1365044A1 |

| Комбинированное устройство временной задержки и формирования импульсов | 1987 |

|

SU1443151A1 |

Авторы

Даты

1980-11-15—Публикация

1978-04-05—Подача