Изобретение относится к вычислительной технике, в частности к устройствам автоматического контроля логических блоков вычислительной техники.

Цель изобретения - повышение достоверности контроля.

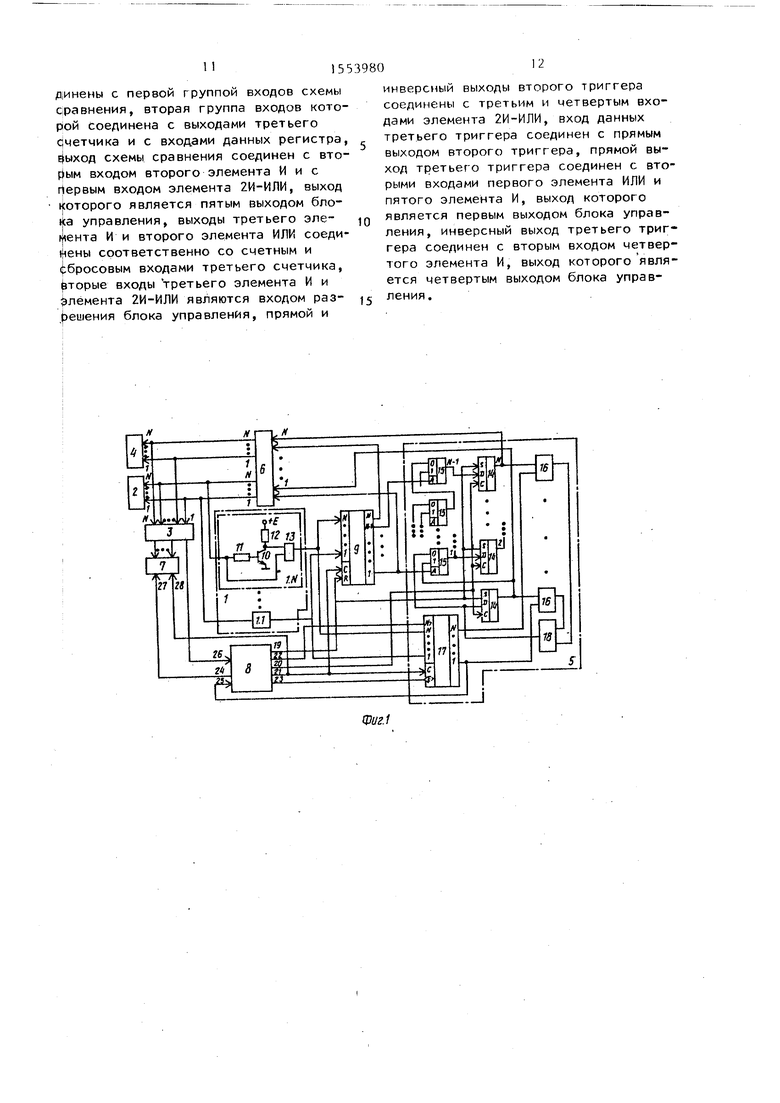

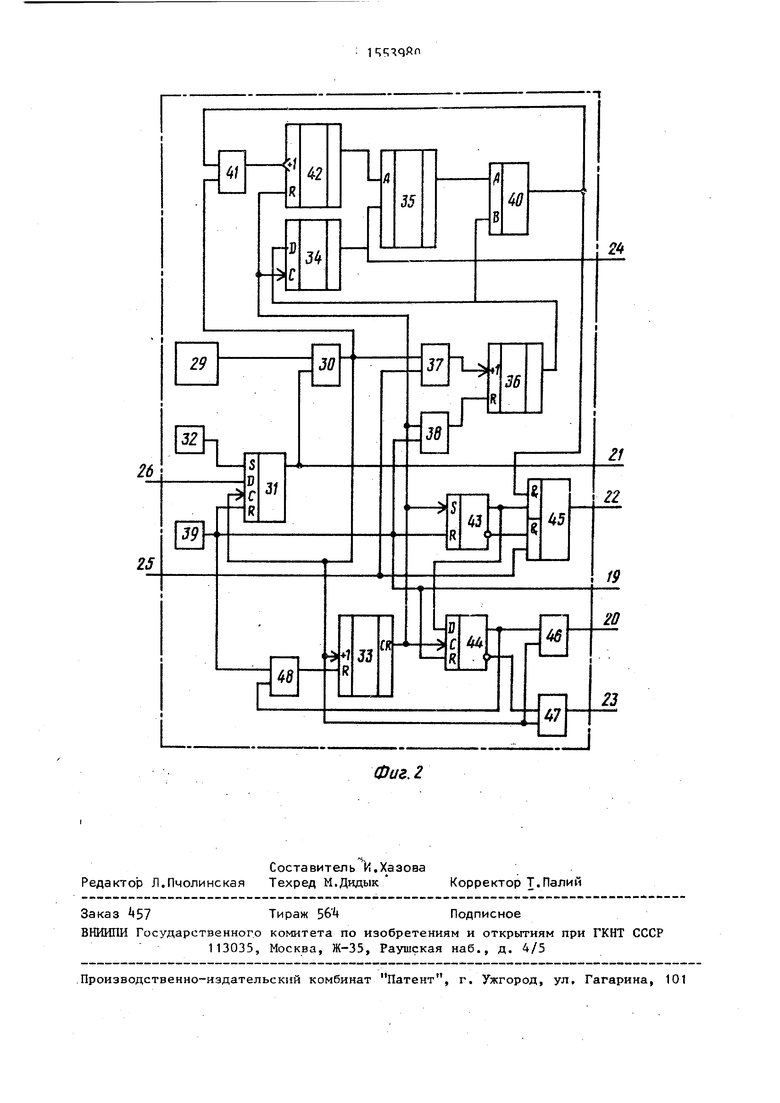

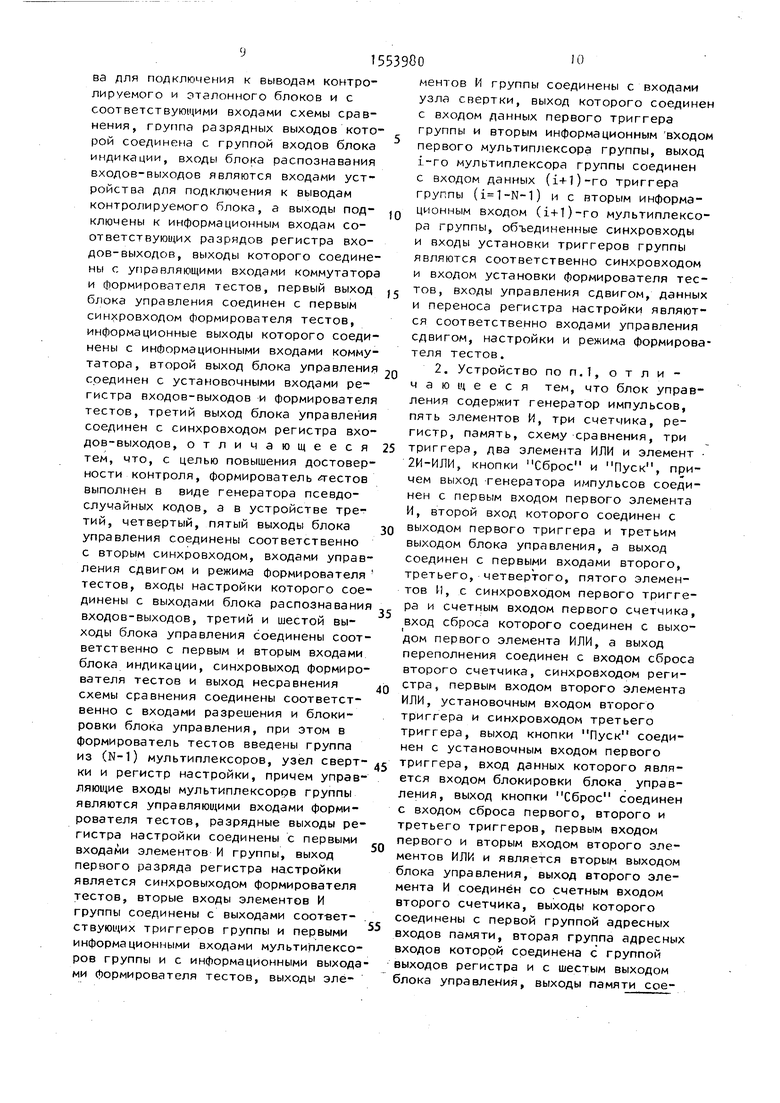

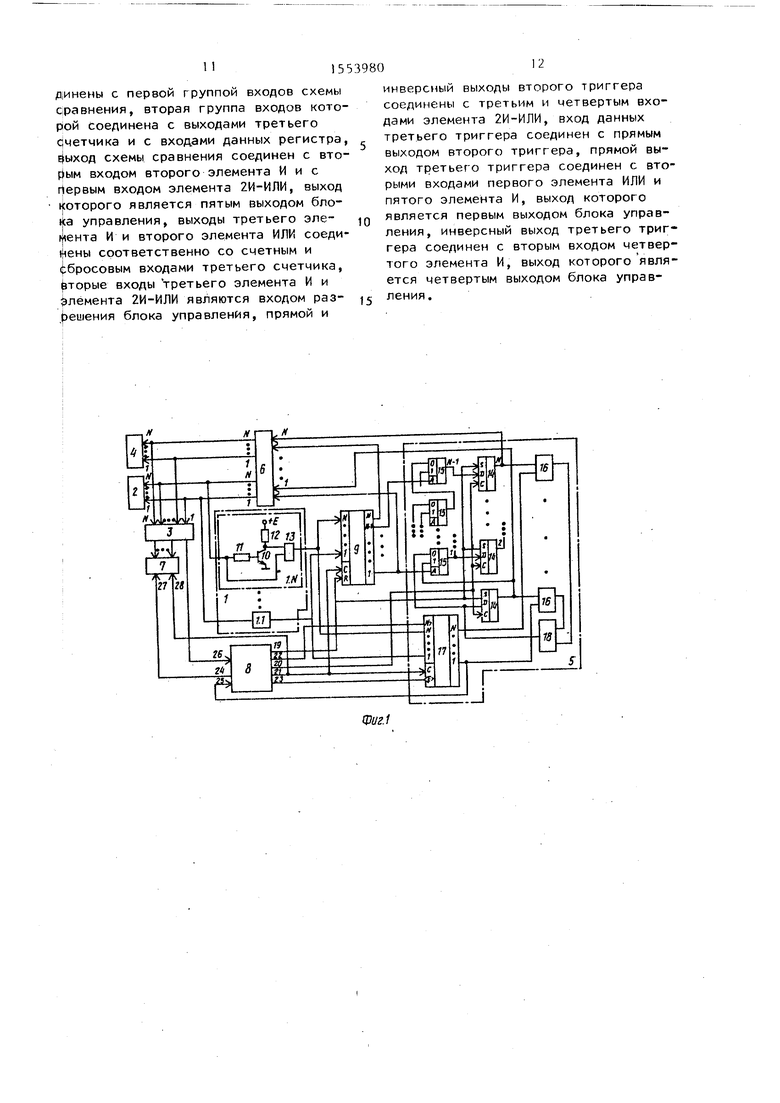

На фиг.1 представлена схема устройства для контроля логических блоков; на фиг.2 - схема блока управления.

Устройство контроля логических блоков содержит блок 1 распознавания входов-выходов, контролируемый блок 2, схему 3 сравнения, эталонный блок 4, формирователь 5 тестов (перестраиваемый генератор псевдослучайной

последовательности), коммутатор 6 входов-выходов, блок 7 индикации, блок 8 управления, регистр 9 входов- выходов.

Реализация одного разряда блока 1 распознавания входов-выходов показана на фиг.1. Он состоит из транзистора 10 с резисторами 11 и 12 в цепи базы и коллектора соответственно, включенного по схеме с общим эммите- ром, и элемента И 13

Формирователь 5 тестов состоит из группы триггеров (N-разрядного регистра псевДослучайной последовательности) 14, группы (N-1) мультиплексоров (коммутатора сдвигов) 15, группы N элементов И 16, регистра 17 настСЛ СП

00

со оо

ройки, узла 18 свертки (по модулю ива).

Блок 8 управления имеет выходы 19 2k, входы 25, 26, блок 7 индикации имеет входы 27 и 28.

Блок 8 управления (фиг.2) состоит из генератора 29 тактовых импульсов, первого элемента И 30, первого триггера 31 пуска, кнопки Пуск 32, nepиого счетчика 33 тактов, имеющего коэффициент пересчета N, равный количеству разрядов контролируемого бло- (а, регистра 34 количества входов, памяти 35 (ПЗУ).

В состав блока 8 управления входит третий счетчик 36 входов, третий элемент И 37, второй элемент ИЛИ 38, нопка 39 сброса, схема 40 сравнения зторой элемент И 41, второй счетчик ч2 количества разрядов обратной свя- :зи, второй триггер 43 цикла, третий триггер № запуска тестов, элемент 2И-ИЛИ 45, пятый элемент И 46, четвертый элемент И 47, первый элемент ИЛИ 48.

Устройство работает следующим образом.

При нажатии кнопки 39 Сброс (см. фиг.2) производится начальная установка блоков устройства. Сигнал Сброса через выход 19 блока 8 управ- Иения поступает (см фиг.1) на выход Начальной установки регистров 9 и 14 1а также на входы начальной установки триггеров 31, 43 и 44 (см. фиг.2), через элемент ИЛИ 48 на вход началь- йой установки счетчика 33 и через элемент ИЛИ 38 на вход начальной установки счетчика 36 входов.

После начальной установки нуль с триггера 31 пуска поступает на второй вход элемента И 30 и не пропускает через него тактовые импульсы с генератора 29.

По окончании начальной установки под действием нулевых сигналов с выхода регистра 9 выходы коммутатора 6 входов-выходов устанавливается в вы- сокоимпедансное состояние. При этом на выходе блока 1 распознавания устанавливается двоичный код с единицами в разрядах, соответствующих входным выводам контролируемого блока 2, и нулями в разрядах, соответствующих выходным выводам. Выполняется это следующим образом. Если вывод контролируемого блока 2 является выходом, находящимся в состоянии логического

5

0

0

5

0

5

0

5

нуля, и на нем присутствует напряжение ио, то низкий потенциал поступает на второй вход элемента И 13. При этом на выходе элемента И 13 присутствует сигнал логического нуля, соответствующий выходу контролируемого блока 2. Если вывод контролируемого блока 2 является выходом с уровнем напряжения U,, , соответствующим логической единице, то высокий потенциал через сопротивление 11 поступает в базу транзистора Г10 и открывает его. Низкий потенциал с коллектора открытого транзистора 10 поступает на первый вход элемента И 13 и обеспечивает нуль на выходе этого элемента, соответствующий выходу контролируемого блока 2. В случае, если распознаваемый внешний вывод является входом, на нем присутствует напряжение 11вУ (U0 U.,), которого недостаточно, чтобы открыть транзистор 10 ввиду значительной величины резистора 11. Таким образом, на первый вход логического элемента И 13 поступает высокий потенциал с коллектора закрытого транзистора 10, а на второй вход элемента И 13 - потенциал свободного входа , который воспринимается как сигнал логической единицы, следовательно, на выходе элемента И 13 будет высокий сигнал, соответствующий входу контролируемого блока 2.

Двоичный код с выхода блока 1 распознавания входов-выходов поступает на входы регистров 9 и 17 и заносится в эти регистры при запуске устройства. Это выполняется следующим образом. По нажатию кнопки 32 Пуск (см. фиг.2) сигнал, поступающий на вход триггера 31 пуска устанавливает этот триггер в единицу,, По перепаду из логического нуля в единицу, поступающему с выхода триггера 31 на выход 21 блока управления 8 и на входы записи регистров 9 и 17 (см. фиг.1), информация с выхода блока 1 распознавания записывается в регистр 9 входов-выходов и регистр 17 настройки.

Единица с выхода триггера 31 (см. фиг.2) поступает на второй вход логического элемента И 30 и разрешает прохождение через него тактовых импульсов с генератора 29о Начинается первый цикл настройки формирователя 5 тестов. Первый цикл настройки вада- ется нулевым состоянием триггера 43 цикла и триггера 44 запуска тестов

при выполнении сброса. При этом единица с инверсного выхода триггера A3 поступает на третий вход элемента 2И-ИЛИ 45 и обеспечивает прохождение информации с выхода первого разряда регистра 17 (сме фиг.1) на вход 25 блока 8 управления и далее через элемент 2И-ИЛИ 45 на выход 22 блока 8 управления и вход переноса сдвигового регистра настройки 17.

Единица с инверсного выхода триггера 44 поступает на первый вход элемента И 47 и разрешает прохождение тактовых импульсов с выхода элемента И 30 через элемент И 47 на выход 23 блока 8 управления и далее на вход управления сдвигом регистра 17 настройки. В первом цикле производится

10

15

на второй вход которого поступает единица с выхода триггера 43 цикла. Единица с выхода элемента 2И-ИЛИ 45 чеоез выход 2 блока 8 управления по ступает на вход переноса регистра 1 настройки. Таким образом, единицы за носятся в разряды регистра 17 настройки, выделенные под обратную связь

При сравнении очередного номера разряда единичный сигнал с выхода схемы 40 сравнения поступает на первый вход элемента И 41, на второй вход которого поступает тактовый импульс с выхода элемента И 30. Сигнал с выхода элемента И 41 поступает на счетный вход счетчика 42 и увеличивает его значение на единицу. Код с выхода счетчика 42 поступает

25

30

35

циклический сдвиг информации в регист-20 на адресный вход памяти 35 и служит ре 17 настройки. Одновременно в счетчике 36 подсчитывается количество единиц в регистре 17. Если в очередном такте сдвига в первом разряде регистра 17 находится единица, то сигнал высокого уровня поступает на второй вход элемента И 37 и разрешает прохождение тактового импульса на счетный вход счетчика 36. Содержимое счетчика увеличивается на единицу.

Тактовые импульсы с выхода элемента И 30 поступают на счетный вход счетчика 33.

По завершению N тактов сигнал с выхода переноса счетчика 33 поступает на вход записи регистра 3 и обеспечивает занесение в неги числа входов контролируемого блока из счетчика 36. Одновременно по сигналу переноса с выхода счетчика 33 производится начальная установка счетчика 42 и установка в единицу триггера 43 цикла. Начинается второй цикл настройки

Во втором цикле настройки производится последовательная запись единиц в разряды регистра 17 настройки, выделенные для обратной связи. Номера разрядов обратной связи записаны в памяти 35. Число входов с регистра 34 поступает на младшие разряды адресного входа памяти 35. Схема 40 сравнения сравнивает текущий номер разряда контролируемого блока, соответствующего входу, который находится в счетчике 36, с номером разряда обрат-ной связи, выбираемым из памяти 35. В случае совпадения номеров единица с выхода схемы 40 сравнения поступает на первый вход элемента 2И-ИЛИ 45,

40

45

50

55

для выборки следующего номера разряд обратной связи. По истечении N такто второго цикла настройки в регистре 1 настройки формируется код для выделе ния разрядов обратной связи, сигнал с выхода переноса счетчика 33 тактов поступает на вход записи триггера 44 запуска тестов, на вход данных которого поступает единица с прямого выхода триггера 43 цикла. Триггер 44 устанавливается в единицу. Нуль с ин версного выхода триггера 44 поступае на первый вход элемента И 4 и запре щает поохождение тактовых импульсов на выход 23 блока 8 управления и далее на вход управления сдвигом регистра 17 настройки. Таким образом, ин формация в регистре 17 остается неиз менной во время прохождения теста.

Логическая единица с прямого выхо да триггера 44 поступает на второй вход элемента ИЛИ 48, единица с выхо да которого сбрасывает счетчик 33 тактов. Во время прохождения теста информация в счетчике 33 и на его выходе переноса, а также в регистре 34 количества входов не изменяется. Информация с выхода регистра 34 поступает на выход 24 блока 8 управления и далее на вход 27 блока индикации 7 (см. фиг.1) для индикации числа входов контролируемого блока 2.

Логическая единица с прямого выхода триггера 44 поступает на первый вход элемента И 46 и разрешает прохождение тактовых импульсов на выход 20 блока 8 управления и далее на вход записи регистра 14 (см. фиг.1). Начальное значение в регистре 14 ус0

5

на второй вход которого поступает единица с выхода триггера 43 цикла. Единица с выхода элемента 2И-ИЛИ 45 чеоез выход 2 блока 8 управления поступает на вход переноса регистра 17 настройки. Таким образом, единицы заносятся в разряды регистра 17 настройки, выделенные под обратную связь.

При сравнении очередного номера разряда единичный сигнал с выхода схемы 40 сравнения поступает на первый вход элемента И 41, на второй вход которого поступает тактовый импульс с выхода элемента И 30. Сигнал с выхода элемента И 41 поступает на счетный вход счетчика 42 и увеличивает его значение на единицу. Код с выхода счетчика 42 поступает

5

0

5

0 на адресный вход памяти 35 и служит

0

5

0

5

для выборки следующего номера разряда обратной связи. По истечении N тактов второго цикла настройки в регистре 17 настройки формируется код для выделения разрядов обратной связи, сигнал . с выхода переноса счетчика 33 тактов поступает на вход записи триггера 44 запуска тестов, на вход данных которого поступает единица с прямого выхода триггера 43 цикла. Триггер 44 устанавливается в единицу. Нуль с инверсного выхода триггера 44 поступает на первый вход элемента И 4 и запрещает поохождение тактовых импульсов на выход 23 блока 8 управления и далее на вход управления сдвигом регистра 17 настройки. Таким образом, информация в регистре 17 остается неизменной во время прохождения теста.

Логическая единица с прямого выхода триггера 44 поступает на второй вход элемента ИЛИ 48, единица с выхода которого сбрасывает счетчик 33 тактов. Во время прохождения теста информация в счетчике 33 и на его выходе переноса, а также в регистре 34 количества входов не изменяется. Информация с выхода регистра 34 поступает на выход 24 блока 8 управления и далее на вход 27 блока индикации 7 (см. фиг.1) для индикации числа входов контролируемого блока 2.

Логическая единица с прямого выхода триггера 44 поступает на первый вход элемента И 46 и разрешает прохождение тактовых импульсов на выход 20 блока 8 управления и далее на вход записи регистра 14 (см. фиг.1). Начальное значение в регистре 14 ус

7 15

танавливается по сигналу сброса с выхода 19 блока 8 управления, при этом во всех разрядах устанавливается единичное значение. Это необходимо д|пя того, чтобы генерируемая псевдослучайная последовательность не была вырожденной, состоящей из нулей. Псевдослучайный код в очередном такте получается путем сдвига кода, сформированного в предыдущем такте, причем в сдвиге участвуют только раз pRflbi регистра 1, соответствующие входам контролируемого блока 2. Если i-и разряд контролируемого блока 2 является входом, то в i-м разряде регистра 9 записана единица, поступающая на адресный вход 1-го мультиплексора сдвига 15 и обеспечивающая прохождение информации с 1-го триггера 14 на выход мультиплексора 15 и далее на вход (1+1)-го триггера 14 и| нулевой вход (1+1)-го мультиплексо р(э 15.

Если i-й разряд вывода контролируемого блока является выходом, то в i-м разряде регистра 9 записан н|уль. Нуль с выхода этого разряда поступает на адресный вход 1-го мультиплексора 15 и обеспечивает прохож- д|эние информации с выхода (1-1)-го мультиплексора 15 на вход (1+1)-го триггера 14 и нулевой вход (1+1)-го мультиплексора 15. Таким образом, сдвиге обходятся разряды регист- р Ik псевдослучайной последователь- нрсти 4, соответствующие выходам контролируемого блока 2„

На вход первого триггера 14 и нулевой вход первого мультиплексора 15 поступает информация со свертки 18 разрядов обратной связи. Выделение разрядов обратной связи производят N элементов И 16, на первые входы которых поступают сигналы с триггеров 14, а на вторые входы - сигналы с выхода регистра 17 настройки. Информация с первого входа элемента И 16 проходит на выход, если в соответствующем разряде регистра 17 записана единица, если в разряде регистра 17 записан нуль, то на выходе соответствующего элемента И 16 присутствует нуль, который не влияет на входное значение свертки 18.

Псевдослучайная последовательност с выходов триггеров 14 поступает на

информационные входы коммутатора 6. Если 1-й разряд контролируемого блок

0

5

0

5

980

,,

0

0

45

0

5

я

2 является входом, то в 1-м разряде регистра 9 записана единица. Единичный сигнал с выхода 1-го разряда регистра 9 поступает на вход управления i-м разрядом коммутатора 6 и обеспечивает прохождение сигнала псевдослучайной последовательности на 1-й вход контролируемого 2 и эталонного 4 блоков. Если i-й разряд контролируемого блока 2 является выходом, то нулевой сигнал с выхода i-ro разряда регистра 9 поступает на управляющий вход 1-го разряда коммутатора 6 и обеспечивает высокоимпедансное состояние на выходе этого разряда.

Сигналы с выводов контролируемого 2 и эталонного 4 блоков поступают на схему 3 сравнения. В случае несовпадения сигналов по какому-то из разрядов нулевой сигнал с выхода схемы 3 сравнения поступает на вход 26 блока управления 8 и далее на вход данных триггера 31 пуска (см. фиг.2), на вход записи которого поступают импульсы с элемента И 30. Триггер 31 устанавливается в нулевое состояние. Сигнал логического нуля с выхода триггера 31 поступает на второй вход элемента И 30 и запрещает прохождение тактовых импульсов с выхода генератора 29 на узлы и блоки устройства. Устройство переходит в состояние Останов, о чем свидетельствует нулевой сигнал, поступающий с выхода триггера 31 на выход 21 блока 8 управления и далее на вход 28 блока 7 индикации. При этом сигналы поразрядного сравнения с выхода схемы сравнения 3 поступают на индикацию в блок 7 индикации.

Останов устройства производится нажатием кнопки 39 Сброс. При этом сигнал с кнопки 39 поступает на вход сброса триггера 31 и устанавливает его в нулевое состояние.

Формула изобретения

1. Устройство для контроля логических блоков, содержащее блок управления, блок распознавания входов-выходов, регистр входов-выходов, схему сравнения, блок индикации, коммутатор и формирователь тестов, включающий группу из N элементов И и группу из N триггеров, где N - число выводов контролируемого блока, выходы коммутатора соединены с выходами устройстУ

ва для подключения к выводам контролируемого и эталонного блоков и с соответствующими входами схемы срав

рой соединена с группой входов блока индикации, входы блока распознавания входов-выходов являются входами устройства для подключения к выводам контролируемого блока, а выходы подключены к информационным входам соответствующих разрядов регистра входов-выходов, выходы которого соединены с управляющими входами коммутатора и формирователя тестов, первый выход блока управления соединен с первым синхровходом формирователя тестов, информационные выходы которого соединены с информационными входами коммутатора, второй выход блока управления соединен с установочными входами регистра входов-выходов и формирователя тестов, третий выход блока управления соединен с синхровходом регистра входов-выходов, отличающееся тем, что, с целью повышения достоверности контроля, формирователь жестов выполнен в виде генератора псевдо- слуиайных кодов, а в устройстве третий, четвертый, пятый выходы блока управления соединены соответственно с вторым синхровходом, входами управления сдвигом и режима формирователя тестов, входы настройки которого соединены с выходами блока распознавания входов-выходов, третий и шестой выходы блока управления соединены соответственно с первым и вторым входами блока индикации, синхровыход формирователя тестов и выход несравнения схемы сравнения соединены соответственно с входами разрешения и блокировки блока управления, при этом в формирователь тестов введены группа

10

15

2Q253900 0

ментов И группы соединены с входами узла свертки, выход которого соединен с входом данных первого триггера группы и вторым информационным входом первого мультиплексора группы, выход i-ro мультиплексора группы соединен с входом данных (i+l)-ro триггера группы (i 1-N-1) и с вторым информационным входом (1+1)-го мультиплексора группы, объединенные синхровходы и входы установки триггеров группы являются соответственно синхровходом и входом установки формирователя тестов, входы управления сдвигом, данных и переноса регистра настройки являются соответственно входами управления сдвигом, настройки и режима формирователя тестов.

2. Устройство по п.1, о т л и 2Q25

30

5

0

чающееся тем, что блок управления содержит генератор импульсов, пять элементов И, три счетчика, регистр, память, схему сравнения, три триггера, два элемента ИЛИ и элемент 2И-ИЛИ, кнопки Сброс и Пуск, причем выход генератора импульсов соединен с первым входом первого элемента И, второй вход которого соединен с выходом первого триггера и третьим выходом блока управления, а выход соединен с первыми входами второго, третьего, четвертого, пятого элементов И, с синхровходом первого триггера и счетным входом первого счетчика, вход сброса которого соединен с выходом первого элемента ИЛИ, а выход переполнения соединен с входом сброса второго счетчика, синхровходом регистра s первым входом второго элемента ИЛИ, установочным входом второго триггера и синхровходом третьего триггера, выход кнопки Пуск соединен с установочным входом первого

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программного контроля | 1987 |

|

SU1464142A1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1259270A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство для формирования тестов | 1987 |

|

SU1429121A1 |

| Многоканальное устройство тестового контроля логических узлов | 1990 |

|

SU1837295A1 |

| Устройство для контроля программных автоматов | 1988 |

|

SU1571552A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1386998A1 |

| Устройство для функционального контроля интегральных схем | 1988 |

|

SU1737465A1 |

| Устройство для контроля и диагностики цифровых блоков | 1983 |

|

SU1167610A1 |

Изобретение относится к вычислительной технике и может быть использовано преимущественно для автоматического контроля логических блоков. Цель изобретения - повышение достоверности контроля. Устройство для контроля логических блоков содержит блок 1 распознавания входов-выходов, подключенный к выводам контролируемого блока 2, схему сравнения 3, эталонный блок 4, формирователь тестов (перестраиваемый генератор псевдослучайной последовательности) 5, предназначенный для генерации входной тестовой последовательности, поступающей через коммутатор 6 входов-выходов на контролируемый 2 и эталонный 4 блоки. Для индикации числа входов и номера вывода контролируемого блока 2, на котором обнаружена ошибка, а также состояния устройства контроля служит блок индикации 7, соединенный со схемой сравнения 3 и блоком управления 8. 1 з.п. ф-лы, 2 ил.

из (N-1) мультиплексоров, узел сверт- АС триггера, вход данных которого является входом блокировки блока управления, выход кнопки Сброс соединен с входом сброса первого, второго и третьего триггеров, первым входом первого и вторым входом второго элементов ИЛИ и является вторым выходом блока управления, выход второго элемента И соединен со счетным входом второго счетчика, выходы которого соединены с первой группой адресных входов памяти, вторая группа адресных входов которой соединена с группой выходов регистра и с шестым выходом блока управления, выходы памяти соеки и регистр настройки, причем управляющие входы мультиплексоров группы являются управляющими входами формирователя тестов, разрядные выходы регистра настройки соединены с первыми входами элементов И группы, выход первого разряда регистра настройки является синхровыходом формирователя тестов, вторые входы элементов И группы соединены с выходами соответствующих триггеров группы и первыми информационными входами мультиплексоров группы и с информационными выходами Формирователя тестов, выходы эле0

5

ется входом блокировки блока управления, выход кнопки Сброс соединен с входом сброса первого, второго и третьего триггеров, первым входом первого и вторым входом второго элементов ИЛИ и является вторым выходом блока управления, выход второго элемента И соединен со счетным входом второго счетчика, выходы которого соединены с первой группой адресных входов памяти, вторая группа адресных входов которой соединена с группой выходов регистра и с шестым выходом блока управления, выходы памяти соеринены с первой группой входов схемы сравнения, вторая группа входов которой соединена с выходами третьего с,четчика и с входами данных регистра, йыход схемы сравнения соединен с вторым входом второго элемента И и с первым входом элемента 2И-ИЛИ, выход которого является пятым выходом блока управления, выходы третьего элемента И и второго элемента ИЛИ соеди- tjieHbi соответственно со счетным и сбросовым входами третьего счетчика, торые входы третьего элемента И и Элемента 2И-ИЛИ являются входом разрешения блока управления, прямой и

инверсный выходы второго триггера соединены с третьим и четвертым входами элемента 2И-ИЛИ, вход данных третьего триггера соединен с прямым выходом второго триггера, прямой выход третьего триггера соединен с вторыми входами первого элемента ИЛИ и пятого элемента И, выход которого является первым выходом блока управления, инверсный выход третьего триггера соединен с вторым входом четвертого элемента И, выход которого является четвертым выходом блока управления.

| Устройство для контроля логических узлов | 1980 |

|

SU868764A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 1183969, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1990-03-30—Публикация

1988-01-13—Подача