1

Изобретение относится к вычислительной технике и может быть использовано при реали зации технических средств.

Известно устройство для сравнения двоичных чисел, содержащее элементы И, ИЛИ, НЕ, триггеры 1.S

Недостаток устройства - сложность.

Наиболее близким к предлагаемому является устройство для сравнения двоичных тасел, содержащее 1-К-триггеры, элементы ИЛИ-НЕ, НЕ, причем первый и второй информационные входы устройства соединены с первыми (-входами первого и второго .1-К-триггеров соответственно, вход синхронизации устройства подключген ко входам синхронизации J-К-триггеров 21.

Недостаток этого устройства - низкая достоверность функционировання, связанная с воз- JQ можностью появления устойчивого запрещенного состояния.

Цель изобретения - повышение надежности работы устройства.

Поставленная цель достигается тем, что в устройстве для сравнений двоичных чисел, содержащем J-К-триггеры, элементы ИЛИ-НЕ, НЕ, причем первый и второй информационные входы устройства соединены с первыми 1-входами первого и второго J-К-триггеров соответственно, вход синхронизации устройства подключен ко входам синхронизации J-К-триггеров, первый информационный вход устройства через первый элемент НЕ соединен со вторым f-входом второго 1-К-триггера, прямой выход которого подключен к первому выходу устройства, к первому входу элемента ИЛИ-НЕ и ко входу установки в единичное состояние первого J-К-триггера, инверсный выход которого соединен со вторым выходом устройства и со вторым входом элемента ШШ-НЕ, выход ког(ого подключен к третьему выходу устройства, второй информационный вход устройства через второй элемент НЕ соединен со вторым J-входом первого 1-К-триггера, вход начальной установки устройства подключен ко входам установки в нулевое состояние , I-К-трнггеррв.

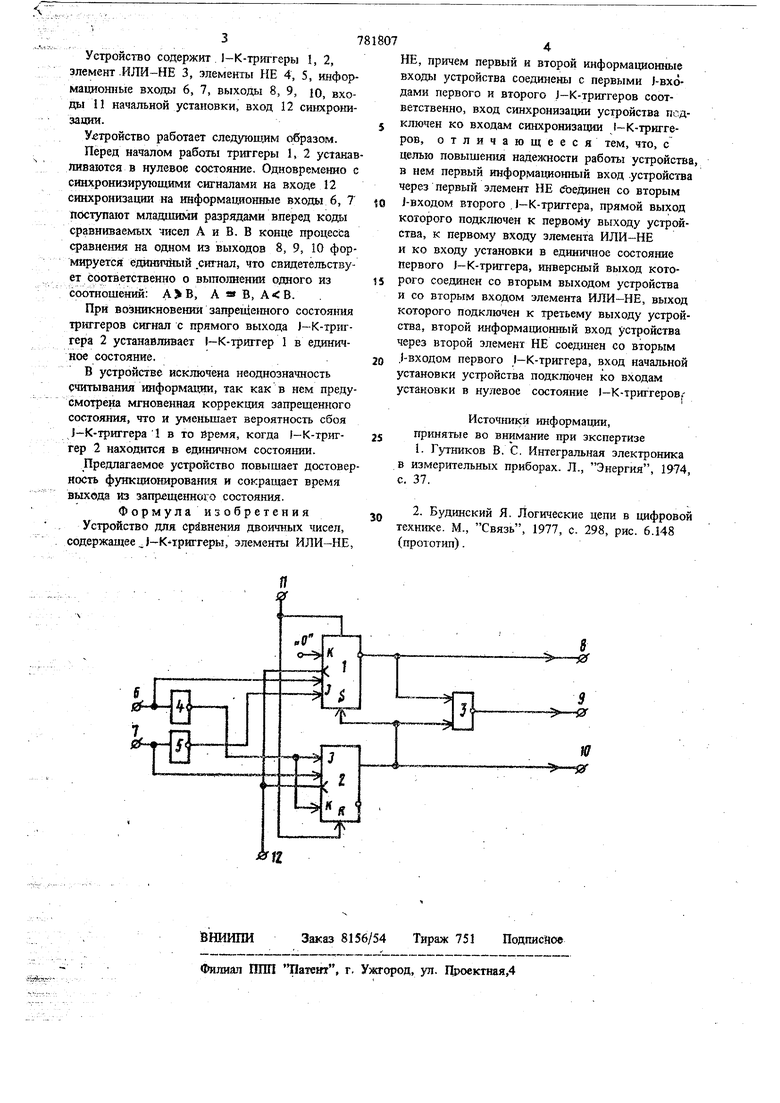

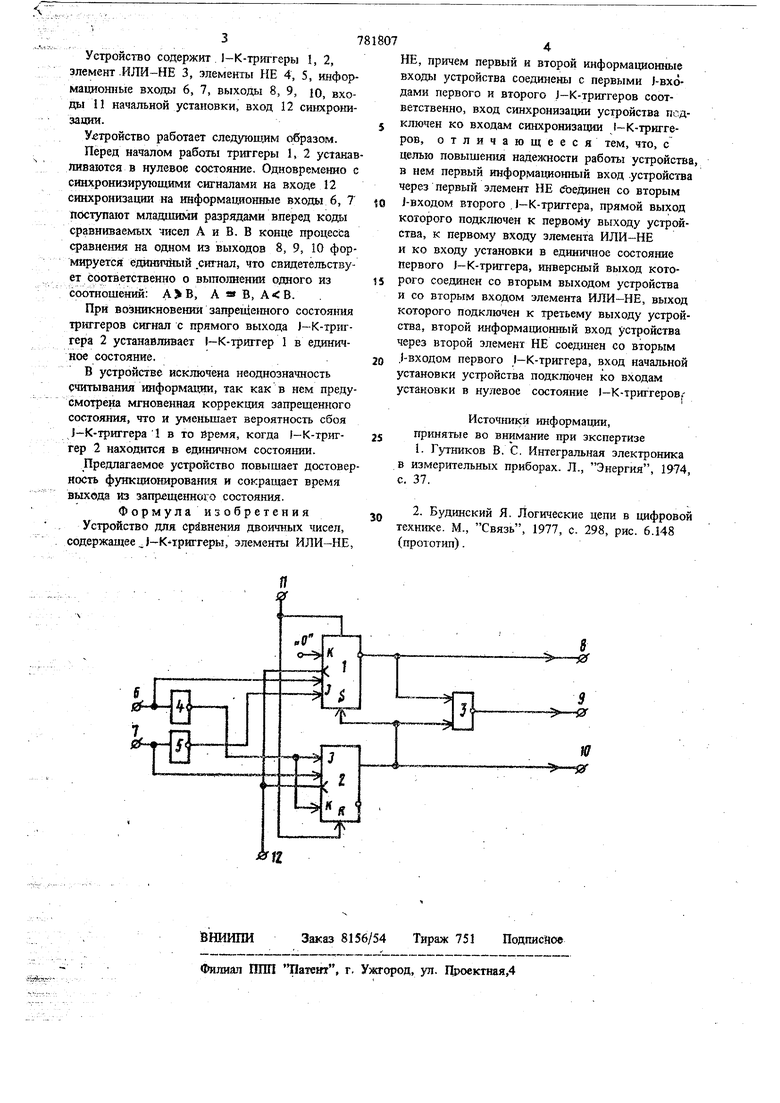

На чертеже представлена блок-схема устрсяс- тва.

37

Устройство содержит )-К-триггеры 1,2, элемент .ИЛИ-НЕ 3, элементы НЕ 4, 5, ннфорMauHomjbre входы 6, 7, выходы 8, 9, ю, входы il начальной установки, вход 12 синхронизации.

Удгтройство работает следующим образом.

Перед началом работы триггеры 1, 2 устанавливаются в нулевое состояние. Одновременно с синхронизирующими сигналами на входе 12 синхронизации на информационные входы 6, 7 поступают младшими разрядами вперед коды сравниваемых чисел А и В. В конце процесса сравнения на одном из выходов 8, 9, 10 формируется ёдйничйый .сигнал, что свидетельствует соответственно о выполнении одного из

соотношений: А В, А В, А В.

При возникновения запрещенного состояния триггеров сигнал с прямого выхода J-K-xpin-гера 2 устанавливает 1-К-триггер I в единичное состояние.

В устройстве исключена неоднозначность считывания информагош, так как в нем предусмотрена мгновенная коррекция запрещенного состояния, что и уменьшает вероятность сбоя J-К-триггера 1 в то время, когда 1-К-триггер 2 находится в единичном состоянии.

Предлагаемое устройство повышает достоверность функционирования и сокращает время выхода из эапреще1шого состояния.

Формулаизобретения

Устройство для сравнения двоичных чисел, содержащее }-К триггеры, элементы ИЛИ-НЕ,

НЕ, причем первый и второй информационные входы устройства соединены с первыми J-BXOдами первого и второго J-К-триггеров соответственно, вход синхронизации устройства подключен ко входам синхронизации I-К-триггеров, отличающееся тем, что, с целью повыщешш надежности работы устройства в нем первый информационный вход .устройства через первый элемент НЕ (Яэединен со вторым j-входом второго , J-К-триггера, прямой выход которого подключен к первому выходу устройства, к первому входу элемента ИЛИ-НЕ и ко входу установки в едшпггаое состоя{ше первого J-К-триггера, инверсный выход которого соединен со вторым выходом устройства и со вторым входом элемента ИЛИ-НЕ, выход которого подключен к третьему выходу устройства, второй информационный вход устройства через второй элемент НЕ соед1шен со вторым .1-входом первого I-К-триггера, вход начальной установки устройства подключен ко входам установки в нулевое состояние )-К-триггеров.ИстоЧники информации, принятые во внимание при экспертизе

1.Гутников В. С. Интегральная электроника в измерительных приборах. Л., Энергия, 1974, с. 37.

2.Будинский Я. Логические цепи в цифровой технике. М., Связь, 1977, с. 298, рис. 6.148

(прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сравнения двоичных чисел | 1979 |

|

SU798816A1 |

| Устройство для сравнения чисел | 1979 |

|

SU822176A1 |

| Устройство для сравнения двоич-НыХ чиСЕл | 1979 |

|

SU798811A1 |

| Устройство для сравнения чисел | 1979 |

|

SU842791A1 |

| Устройство для сравнения чисел | 1981 |

|

SU1008730A1 |

| Устройство для сравнения двоичныхчиСЕл | 1979 |

|

SU822178A1 |

| Генератор двоичных чисел | 1984 |

|

SU1201827A1 |

| Устройство для сравнения двоичных чисел | 1980 |

|

SU907542A2 |

| Устройство для сравнения двоичных чисел | 1977 |

|

SU696440A1 |

| Устройство для сравнения двоичных чисел | 1978 |

|

SU752328A1 |

Авторы

Даты

1980-11-23—Публикация

1979-03-28—Подача