1

Изобретение относится к автомата ке, измерительной .технике и может быть использовано в различных логических управляющих, программных, вычислительных, измерительных и других устройствах.

В современных устройствах автоматики, измерительной техники,, системах программного управления широкое распространение получила последовательная (поразрядная) передача и обработка цифровой информации, при которой несколько снижается быстродействие по сравнению с устройствами, в которых принят параллельный способ обработки и передачи информации, но значительно сокращается количество электрических связей, упрощается схемотехника отдельных узлов, в частности арифметических устройств (сумматот ров), что повышает надежность всего устройства в целом.

В системах с последовательной передачей информации числа преимущественно передаются начиная от младшего разряда к старшему, что обуславливается работой последовательного сумматора. В состав таких систем входят устройства сравнения, выявлянмцие равнозначность или неравнозначность празрядных двоичных чисел (сравнение двух чисел между собой, сравнение уставки с числом и т,д.).

Известно устройство сравнения-двух

чисел, основанное на их поразрядном сравнении, содержащее п-ячеек поразрядного сравнения, каждая с двумя входами и двумя выходами, и пирамидально соединенные ярусы ячеек срав нения-к-разрядных кодов, входы ячеек поразрядного сравнения подключены ко входам устройства, а выходы ячейки сравнения к-разрядных кодов последнего яруса соединены с выходами устройства 1 .

Недостатки этого устройства состоят в том, что число ячеек поразрядного сравнения равно разрядности сравниваемых чисел, а для проведения операций сравнения сравниваемые числа должны быть предварительно записаны в соответствующие регистры.

Тот факт, что операция сравнения в этом устройстве производится начиная со старшего разряда, а в цифровых устройствах с последовательной передачей, более приемлема передача информации начиная с младшего разряда, также приводит к тому, -что сравнение

чисел по данным устройствам требует

Предварительной записи сравниваемых чисел в регистры.

Наиболее близким к предлагаемому является устройство, содержащее логические элементы ИЛИ-НЕ, триггеры и логические элементы И, в котором сравниваемые числа А и В последовательным кодом поступают на устройство сравнения начиная со старших разрядов. Первая неравнозначность в сравниваемых разрядах чисел свидетельствует о неравенстве чисел и фиксируется соответствующими триггерами. Последующие разряды чисел не проходят на счетные входы триггеров. Существующее устройство сравнения позволяет создавать устройства сравнения двоичных чисел с малым, не зависящим от разрядности чисел, количеством элементов логических схем 2J

Однако применение этих устройств в системах с последовательной передачей информации, начиная с младшего разряда, связано с предварительной записью чисел в сдвигаквдие регистры, что приводит к снижению быстродействия, а также к усложнению в целом устройства сравнения, снижению его надежности.

Цель изобретения - повышение быстродействия.

Указанная цель достигается тем, что в устройстве для сравнения чисел содержащем элементы И-НЕ, НЕ,-ИСКЛЮЧАЮЩЕЕ ИЛИ, триггеры, в которых .первый информационный вход устройства соединен с первым входом первого элемента И-НЕ и через первый элемент НЕ с первым входом второго элемента ИНЕ, второй информационный вход устройства подключен ко второму входу второго элемента И-НЕ и через второйэлемент НЕ - ко второму входу первого элемента И-НЕ, выход которого соединен с первым входом третьего элемента И-НЕ, с первым входом четвертого элемента И-НЕ и с первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход второго элемента И-НЕ подключен к первому входу пятого элемента И-НЕ ко второму входу четвертого элемента И-НЕ и ко второму входу первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ,.выход которого соединен со вторыми входами третьего и пятого элементов И-НЕ, выходы третьего и пятого элементов И-НЕ соединены с информационными входами первого и второго триггеров соответственно, выход четвертого элемента ИНЕ подключен через третий элемент НЕ к первому входу элемента ИЛИ-НЕ, выход которого соединен со входом синхронизации первого и второго триггеров, выходы которых подключены ко входам второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого подключен к третьему входу четвертого элемента И-НЕ, шина начальной установки соединена со входами установки в единичное состояние первого и второго триггеров и со входом установки в нулевое состояние третьего триггера, шина синхронизации устройства подклю чена ко второму входу элемента ИЛИ. НЕ и ко входу синхронизации третьего

триггера.

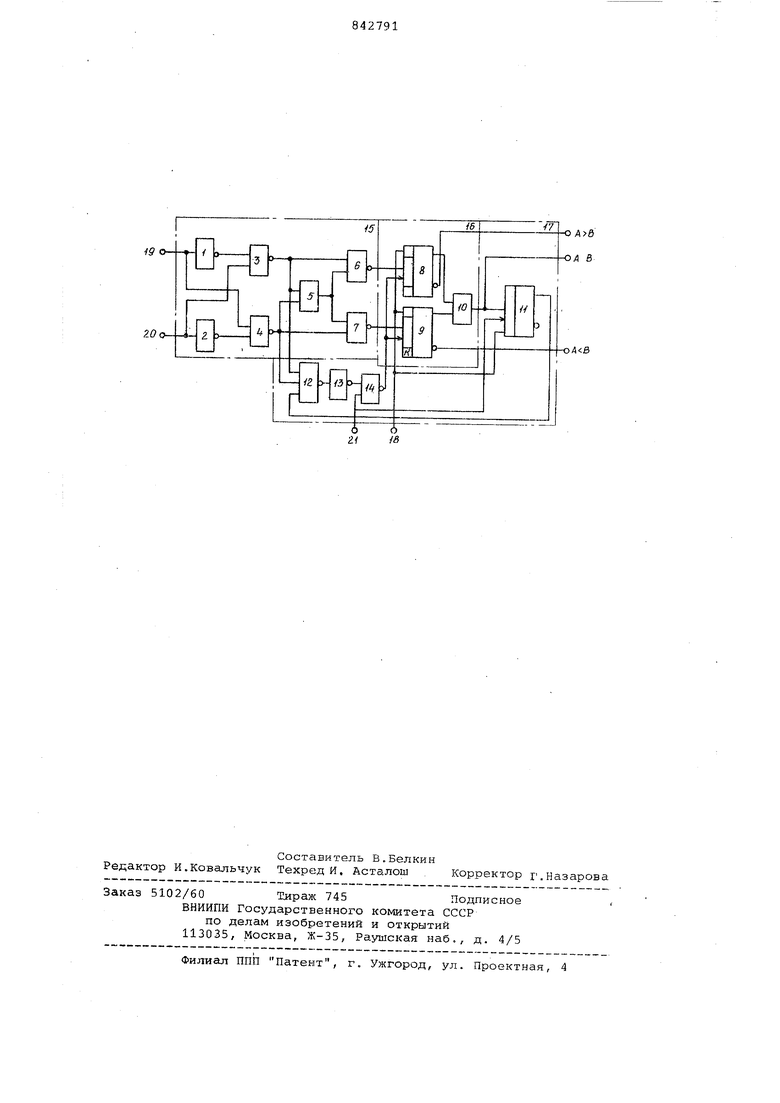

На чертеже приведена функциональ- ная схема устройства.

Устройство для сравнения чисел л содержит элементы НЕ 1 и 2, элементы И-НЕ 3 и 4, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 5, элементы И-НЕ б и 7, триггеры

8и 9 D-типа, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 10, триггер 11 , элемент И-НЕ 12, элемент НЕ 13, элемент ИЛИ5 НЕ 14. Элементы НЕ 1 и 2, И-НЕ 3 и 4, ИСКЛЮЧАЮЩЕЕ ИЛИ 5, И-НЕ 6 и 7 Образуют блок 15 Определения неравнозначности; триггеры 8 и 9 и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 10 образуют блок 16

0 фиксации неравнозначности. Триггер 11 и элементы И-НЕ 12, НЕ 13, ИЛИНЕ 14 образуют блок 17 запрещения изменения состояния блока 16. Триггеры 8 и 9 фиксируют неравнозначность

5 в каждом из сравниваемых разрядах чисел, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 10, триггер 11, элемент И-НЕ 12, элемент НЕ 13 и элемент ИЛИ-НЕ 14 запрещают изменение их состояния, если за неп равнозначностью в более младших разрядах сравниваемых чисел следует их равнозначность в более старших разрядах.

Устройство работает следующим

, образом.

Перед началом операции сравнения импульсный сигнал, приходящий на шину 18, устанавливает триггеры 8 и

9в состояние 1, которые сохраняют это -состояние до окончания срав0 нениятолько в случае, если сравниваемые числа равны между собой.

В случае, если сравниваемые, разрядел чисел не равны,между собой, например , в 0 , в блоке 15 на

5 выходе отдельных его элементов устанавливаются следующие уровни выходных сигналов: на выходах элементов НЕ 1и , на выходах элементов И-НЕ 3 и , при этом на выходе

Q элемента ИСКЛЮЧАЩЕЕ ИЛИ 5 появляется сигнал 1, что разрешает прохождению информации с выходов элементов И-НЕ 3 и Г через элементы И-НЕ б и V на информационные входы .триггеров 8 и 9, в результате на вход триггера 8 поступает сигнал О, а на вход триггера 9 - 1.

Поскольку информация на входах 19и 20 появляется синхронно с появлением тактового импульса по .шине 21,

0 при его исчезновении (по заднему фронту импульса) информация, поступившая на информационные входы триггеров 8 и 9, записывается в эти триггеры ri ,следовательно, триггер 8 ус-

5 танавливается в состояние О, а

триггер 9 сохраняет свое прежнее состояние, т.е. остается в состоянии 1. Как следствие этого,на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 10, а значит и на информационном входе триггера 11, появляется сигнал 1. В момент прихода следукяцего такт вого импульса на входы 19 и 20 пост пает информация об очередных сравни BaeN&ix разрядах чисел, прямой выход триггера 11 принимает состояние сво го информационного входа, а на соот ветствующем входе элемента И-НЕ 12 появляется сигнал 1. Если очередные сравниваемое разряды а: и в равны между собой, на выходах элементов И-НЕ 4 и 3 устана ливаются сигналы 1, вследствие че го на выходе элемента И-НЕ 12 появл ется сигнал О, а на выходе элемен та НЕ 13 - 1. Появление сигнала 1 на первом входе элемента ИЛИ-НЕ 14 запрещает прохождение через этот элемент такт .вых импульсов с шины 21 на счетные входы триггеров 8 и 9, а поэтому последние сохраняют принятое ранее состояние, т.е. сохраняйт неравнозначность, зафиксированную в младших разрядах сравниваемых чисел, в случае, если в более старших разрядах наблюдается их равнозначность. Если в старших разрядах сравниваемы чисел имеет место неравнозначность вида , , то в результате их сравнения триггеры 9. и 8 изменяют свое состояние на противоположное, (как в случае а; 1 и в, 0) . Таким образом, в результате поразрядного сравнения двух чисел А и В, начиная с младшего разряда,, триггеры 9 и 8 зафиксируют последнюю неравнозначность в сравниваемых разрядах чисел, что является окончательным результатом их сравнения между собой. В зависимости от окончательного результата сравнения на одном из входов А7 В или появляется сигнал 1.в случае неравенства сравниваемых чисел, а на выходе А в (инверсный сигнал Равно) - сигнал 1 Если сравниваемые числа равны меж ду собой, на выходах А В, А В и устанавливается сигнал О. В предлагаемом устройстве операция сравнения при последовательной передаче информации, начиная с младшего разряда, может производиться синхронно с продвижением самой инфор мации; сравнение чисел может производиться без предварительной их запи си в соответствующие регистры, что уменьшает количество элементов в сис

теме, в которой применяется устройство сравнения, что повышает над: ежность всей система в целом; кроме того, количество элементов в устройстве для сравнения чисел не зависит от разрядности сравниваемых чисел. Формула изобретения Устройство для сравнения чисел, содержащее элементы И-НЕ, ЙДИ-НЕ, НЕ, ИСКЛЮЧАЮЩЕЕ ИЛИ, триггеры, причем первый информационный вход устройства соединен с первым входом первого элемента И-НЕ и через первый элемент НЕ с первым входом второго элемента И-НЕ, второй информационный вход устройства подключен ко второму входу второго элемента И-НЕ и через второй элемент НЕ - ко второму входу первого элемента И-НЕ, выход которого соединен с первым входом третьего элемента И-НЕ, с первым входом четвертого элемента И-НЕ и с первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход второго элемента И-НЕ подключен к первому входу пятого элемента И-НЕ, ко второму входу четвертого элемента И-НЕ и ко второму входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен со вторыми входами- третьего и пятого элементов И-НЕ, отличающееся тем, что, с целью повышения быстродействия,, в нем выходы третьего и пятого элементов И-НЕ соединены с информационными входами первого и второго триггеров соответст венно, выход четвертого элемента ИНЕ подключен через третий элемент НЕ к первому входу элемента ИЛИ-НЕ, выход которого соединен со входами синхронизации первого и второго триггеров , прямые выходы которых подключены ко входам -второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с информационным входом третьего триггера, прямой выход которого подключен к третьему входу четвертого элемента И-НЕ, шина начальной установки соединена со входами установки в единичное состояние первого и второ- . го триггеров и со входом установки в .нулевое состояние третьего триггера, шина синхронизации устройства подключена ко второму входу элемента ИЛИ-НЕ и ко входу синхронизации третьего триггера. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 531151, кл. G 06 F 7/04, 1975. 2.Авторское свидетельство СССР № 352274, кл. G 06 F 7/.02, 1970 (прототип).

2/ /

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сравнения чисел | 1979 |

|

SU798815A1 |

| Устройство для сравнения чисел | 1980 |

|

SU1003071A1 |

| Устройство для определения фазы спектральных составляющих | 1982 |

|

SU1080148A1 |

| Устройство для сравнения двоичных чисел | 1989 |

|

SU1633390A1 |

| Устройство для сравнивания двоичных чисел | 1982 |

|

SU1089575A1 |

| Устройство для сравнения двоичных чисел | 1977 |

|

SU696440A1 |

| Устройство для определения фазы спектральных составляющих | 1985 |

|

SU1247890A2 |

| Устройство для сравнения чисел | 1981 |

|

SU960768A1 |

| Устройство для спектрального анализа | 1984 |

|

SU1241256A1 |

| Устройство для сравнения двоичных чисел | 1980 |

|

SU907542A2 |

Авторы

Даты

1981-06-30—Публикация

1979-10-17—Подача