печивает высокой стабильности хранимого параметра, поэтому наличие блока аналоговой памяти не только усложняет схему узлового элемента, но и снижает его точность.

Цель изобретения - упрощение,схемы и повышение точности узлового элемента.

yKasaHHasT цель достигается тем, что в узловЪй элемент сеточной модели, содержащий блок проводимости, BXO ды которого соединены с выходами блока управления, первый вход которОго подключен к выходу программного блока введены блок формирования относительной длительности импульса, сглаживающая емкость и блок линеаризации, включающий два усилителя, выходы которых соединены с крайними выводами делителя напряжения, средний вывод которого подключен ко второму входу блока управления, третий вход которого соединен с выходом блока формирования относительной длительности импульса, первый и второй выходы блока проводимости подключены соответственно ко вхдам первого и второго усилителей блока Линеаризации, одна обкладка сглс1живающей емкости соединена с первьам выходом блока проводимости, другая обкладка сглаживающей емкости подключена к.шине нулевого потенциала. А также тем, что блок управления содержит полевой транзистор, резистор обратной связи, выходной резистор и ограничительный диод, анод которого через выходной резистор соединен с истоком полевого транзистора и с одним выводом резистора обратной связи, другой вывод которого подключен к затвору полей ого транзистора, сток которого является вторым входом блока управления катод ограничительного диода является третьим входом блока управления, другой вывод резистора обратной свяэтл является первым входом блока управления, анод ограничительного диода является выходом блока управления.

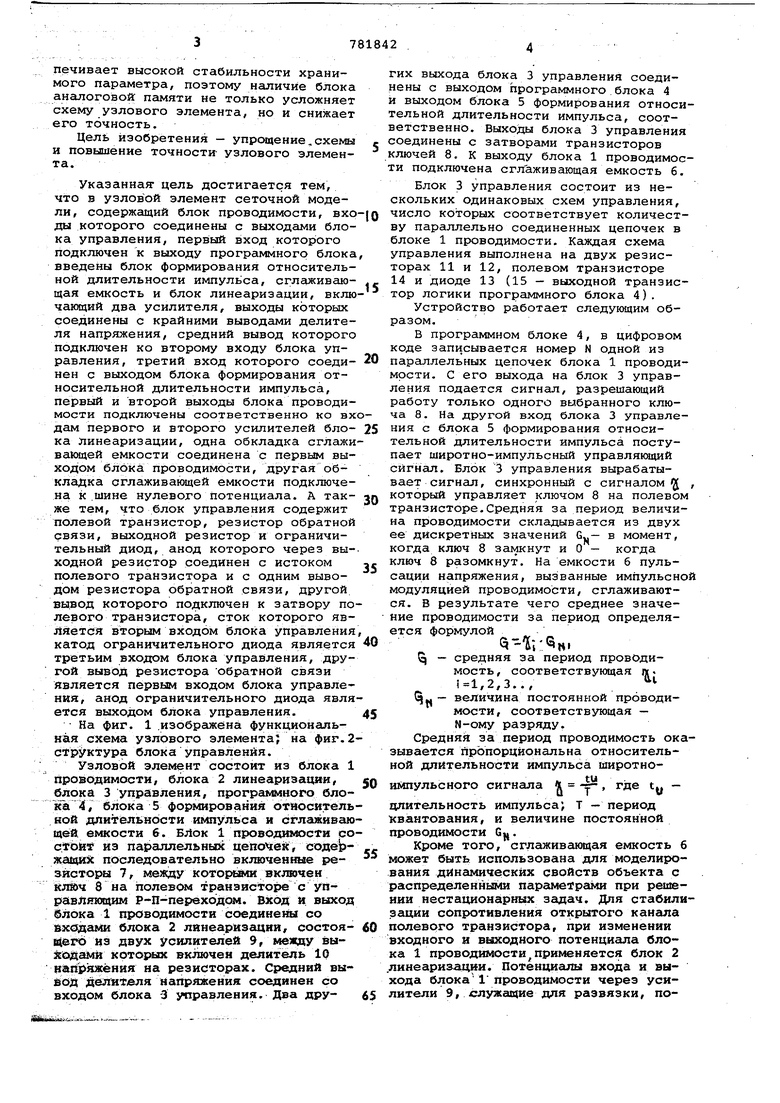

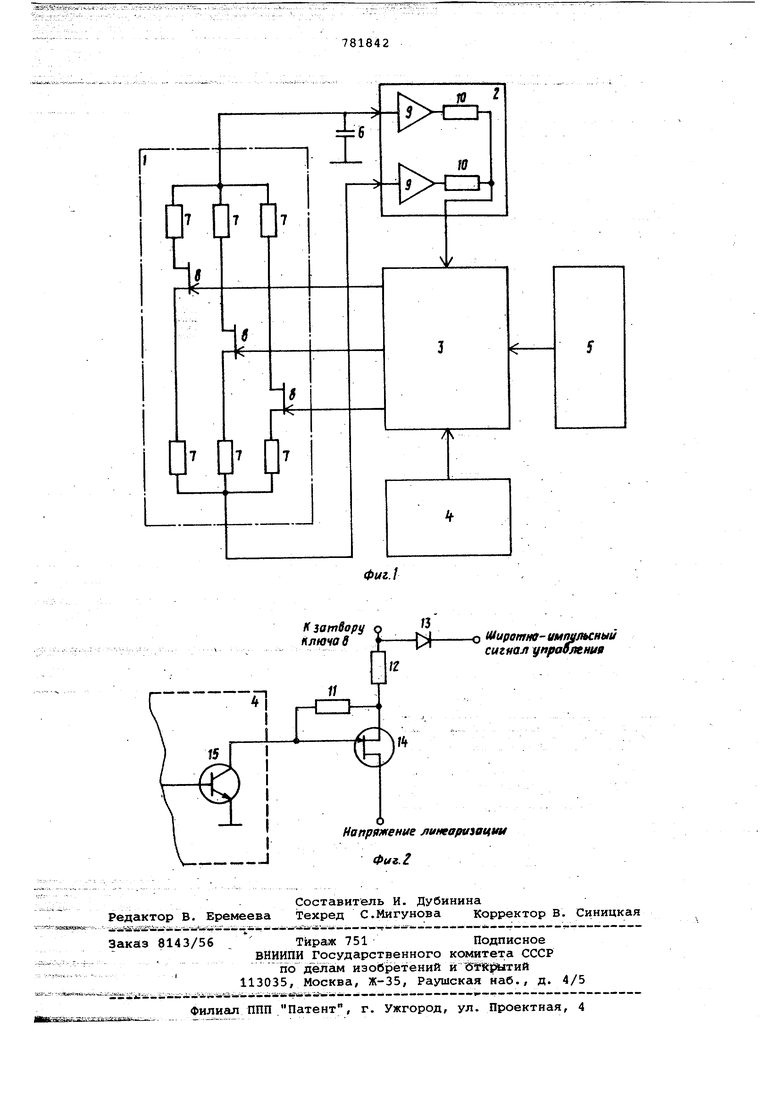

На фиг. 1 .изображена функциональная схема узлового элемента; на фиг.2стр ктура блока управления.

Узловой элеме нт состоит из блока 1 проводимости, блока 2 линеаризации, блока 3 управления, программного 4/ блока 5 формирования отйосительной длит1ельн6сти импульса и сглаживающей емкости 6. БЛОК 1 проводимости сосТойт йэ параллельных uenoftekfCoaebIукзлаея последовательно включенные ре зйсторы 7, между которьили включен 8 на полевом транзисторе с управляющим Р-П-переходом. Вход и выход блока 1 проводимости соединены со ахсщами блока 2 линеаризации, состоящего из двух усилителей 9, ме)вду выxOjEiaiMB KOTOjMJX включен делитель 10 ншп)яжёния на резисторах. Средний выйОйдалителя напряжения соединен со входом блока -3 управления. Два других выхода блока 3 управления соединены с выходом программного блока 4 и выходом блока 5 формирования относительной длительности импульса, соответственно. Выходы блока 3 управления соединены с затворами транзисторов ключей 8. к выходу блока 1 проводимости подключена сглаживающая емкость 6.

Блок 3 управления состоит из нескольких одинаковых схем управления, число которых соответствует количеству парсигшельно соединенных цепочек в блоке 1 проводимости. Каждая схема управления выполнена на двух резисторах 11 и 12, полевом транзисторе 14 и диоде 13 (15 - выходной транзистор логики программного блока 4).

Устройство работает следующим образом.

В программном блоке 4, в цифровом коде записывается номер N одной из параллельных цепочек блока 1 проводимости. С его выхода на блок 3 управления подается сигнал, разрешающий работу только одного выбранного ключа 8. На другой вход блока 3 управления с блока 5 формирования относительной длительности импульса поступает широтно-импульсный управлякиций сигнал. Блок 3 управления вырабатывает сигнсш, синхронный с сигналом который управляет ключом 8 на полевом транзисторе.Средняя за период величина проводимости складывается из двух ее дискретных значений G..- в момент, когда ключ 8 замкнут и О - когда ключ 8 разомкнут. На емкости б пульсации напряжения, вызванные импульсно модуляцией проводимости, сглаживаются, в результате чего среднее значение проводимости за период определяется формулой

Q-llr w

- средняя за период проводимость, соответствующая и. i 1,2,3..,

(q. - величина постоянной проводимости, соответствующая - N-ому разряду.

Средняй за период проводимость оказывается пропорциональна относительной длительности импульса широтноимпульсного сигнала 11 l. где ty Еьлительность импульса j Т - период квантования, и величине постоянной проводимости GU.

Кроме того, сглаживавмцая емкость б может быть использована для моделирования динамических свойств объекта с распределенныоии параметрами при решении нестационарных задач. Для стабили.зации сопротивления открытого канала полевого транзистора, при изменении входного и выходного потенциала блока 1 проводимости применяется блок 2 линеаризации. Потенциалы входа и выхода блока 1 проводимости через усилители 9, служащие для развязки, поступают на реэистивный делитель напряжения на резисторах 10, с которог снимается полуразность поданных напр жений. Из теории полевых транзисторо известно, что стабилизация сопротивления канала или. линеаризация, возможна при подаче на затвор половины разности напряжений стока и истока. Если учесть, что величина сопЕ отйвле ния резисторов 7 каждой из цепочек блока 1 проводимости одинакова, а следовательно, одинаковы и падения напряжения на них, то на выходе дели теля блока 2 линеаризации выделяется только полуразность напряжений между ctOKOM и истоком транзистора, так ка равные падения напряжения на -резисTO iax 7 компенсируются. Напряжение линеаризации с помощью блока 3 управ ления подается на затвор выбранного транзистора в моменты отпирания ключа. Блок управления работает следующим образом. При сигнале Логическая 1 с выхо да соответствующей схемы программного блока 4 закрывается выходной тран зистор 15 логики. Исток и затвор транзистора 14 оказываются связанными через резистор 11 и транзистор от крывается, при этом на истоке его пр сутствует напряжение линеаризации. При подаче запирающего значения широтно-импульсного управляющего сиг нала с блока 5 формирования относительной длительности импульса диод 13открывается и на затвор ключа 8 подается низкий запирающий.потенциал При отпирающем значении широтноимпульсного сигнала диод 13 закрыт и на затвор ключа 8 через, транзистор 14и резистор 12 подается напряжение линеаризации. При сигнале логический О на выходе блока 4 на затвор транзистора 1 подается нулевой потенциал. Транзистор 14 и резистор 11 представляют со бой генератор тока малой величины, поскольку резистор 11 выбирается выcOKOOMHtoM, включенный между источником напряжения линеаризации и шиной нулевого потенцисша. Омическое сопротивление канала транзистора 14 практически равно дифференциальному сопротивлению стабилизатора тока. По этому напряжение линеаризации оказывается практически отключенным от за твора ключа 8. На резисторе 11 выделяется напряжение, примерно равйое напряжению бтсёчкй транзйстора 14 и которое закрывает ключ 8. Предлагаемые блоки и связи меж,цу НИМИ повшиают точность и упрощают схему узлового элемента сеточной модели. Формула изобретения 1.Узловой элемент сеточно модели, содержащий блок проводимости, входы которого соединены с выходами блока управления, первый вход котороо подключен к выходу программного блока, отличающийся тем, что, с целью упрощения и пОвьпдения точности, в него введены блок формирования относительной длительности . импульса, сглаживающая емкость и блок линеаризации, включающий два усилителя, выходы которых соединены с крайними выводами делителя напрЯжения, средний вывод которого подключен ко второму входу блока управления, третий вход которого соединен с выходом блока формирования относительной длительности импульса, первый и второй выходы блока проводимости подключены соответственно ко входам первого и второго усилителей блока линеаризации, одна обкладка сглаживающей емкости соединена с первым выходом блока проводимости, другая обкладка сглаживающей емкости подключена к шине нулевого потенциала. 2.Узловой элемент по п. 1, о т личающийсй тем, что блок управления содержит полевой транзистор, резистор обратной связи, выходной резистор и огра ничительный диод, анод которого через выходной резистор соединен с истоком полевого транзистора и с одним выводом резистора обратной связи, другой вывод которого подключен к затвору полевого транзистора, сток которого является вторым входом блока управления, катод ограничительного диода является третьим входом блока управления, другой вывод резистора обратной связи является первым.входом блока управления, анод ограничительного диода является выходом блока управления. Источники информации, принятые во внимание при экспертизе 1,Авторское свидетельство СССР I 417803,G 06 G 7/48, 1972. 2.Авторское свидетельство СССР 547790, G Об G 7/46, 1975 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Резистивный узел сеточной модели | 1983 |

|

SU1120366A1 |

| Сеточная модель | 1984 |

|

SU1260981A1 |

| Устройство для моделирования распределенных объектов управления | 1974 |

|

SU491960A1 |

| Высоковольтный электронный ключ | 2024 |

|

RU2837267C1 |

| Высоковольтный электронный ключ | 2022 |

|

RU2780816C1 |

| Устройство для включения и отключения электрического освещения | 1988 |

|

SU1767475A1 |

| Расширитель биполярных импульсов | 1979 |

|

SU788362A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ В УПРАВЛЯЕМЫЙ ПОСТОЯННЫЙ ТОК | 2012 |

|

RU2491703C1 |

| Амплитудно-импульсный модулятор | 1983 |

|

SU1157677A1 |

| ПОЛУПРОВОДНИКОВЫЙ ДАТЧИК МАГНИТНОГО ПОЛЯ | 1995 |

|

RU2092933C1 |

Авторы

Даты

1980-11-23—Публикация

1979-02-19—Подача